# 32-Bit Memory System design: Design of Memory Controller for Micron SDR SDRAM

By CHIN CHUN LEK

### A REPORT

SUBMITTED TO

Universiti Tunku Abdul Rahman in partial fulfillment of the requirements for the degree of BACHELOR OF INFORMATION TECHNOLOGY (HONS) COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus) JAN 2015

## **DECLARATION OF ORIGINALITY**

I declare that this report entitled "**Design of Memory Controller for Micron SDR SDRAM**" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other award.

Signature : \_\_\_\_\_

Name : Chin Chun Lek

Date : 6 APRIL 2015

## ACKNOWLEDGEMENTS

First and foremost I would like to take this opportunity to express my gratitude to my final year project supervisor, Mr. Mok Kai Ming, for his guidance and wisdom during the entire course of this project. I would also like to thank my friends, Chang Boon Chiao, Goh Dih Jian and Arthur for providing me supports. Lastly, I would like to thank my parents for the moral, emotional and financial support they have been providing.

By Chin Chun Lek

### ABSTRACTS

This project focuses on the design of SDRAM Controller that is compatible with Micron SDR SDRAM MT48LC4M32B2 (1 Meg x 32 x 4 banks). After reviewing the previous work, the SDRAM controller is working but there are some differences with the conventional design that makes it to become complicated. This topic will be further discussed in the Literature Review and Design Methodology.

Currently, the interface of SDRAM controller connects to the host is not fully determined. The bus interface within the controllers is required to redesign in order to enable the caches to access the main memory. Therefore, this project is aiming to provide verification to the integration between the SDRAM controller and the cache controller.

## **Table of Contents**

| List of Tables                                         | 7  |

|--------------------------------------------------------|----|

| List of Figures                                        | 8  |

| List of Abbreviations                                  |    |

| Chapter 1: Introduction                                | 11 |

| 1.1: Background                                        | 11 |

| 1.1.2 MIPS – a RISC processor                          | 11 |

| 1.2: Motivation                                        | 12 |

| 1.2.1: Problem Statement                               | 13 |

| Chapter 2: Literature Review                           | 14 |

| 2.1: Memory Hierarchy                                  | 14 |

| 2.2: Processor and Main Memory Interfacing             | 15 |

| 2.3: SDRAM Controller System Background                | 16 |

| 2.4: SDRAM                                             | 16 |

| 2.5: SDRAM controller                                  |    |

| 2.5.1: Read/Write Cycle Timing diagram                 | 20 |

| 2.6: SDRAM Controller and Cache Controller Interfacing | 21 |

| 2.7: Load Mode Register                                | 22 |

| 2.8: Memory Arbiter                                    | 24 |

| 2.9: Protocol Controller State Diagram                 | 25 |

| Chapter 3: Project Scope and Objectives                | 26 |

| 3.1: Project Scope                                     | 26 |

| 3.2: Project Objectives                                | 26 |

| 3.3: Significance and Impact                           | 26 |

| Chapter 4: Methods/Technologies Involved               | 28 |

| 4.1: Design Methodology                                | 28 |

| 4.1.1 Architecture Level Design                        | 29 |

| 4.1.2 Micro-Architecture Level Design (Unit Level)     | 29 |

| 4.1.3 Micro-Architecture Level Design (Block Level)    | 29 |

| 4.2: Protocol Controller Block Design                  |    |

| 4.3: Load Mode Configuration with Multiple Cache       |    |

|                                                        |    |

Faculty of Information and Communication Technology, UTAR

| 4.7: Timeline                                                 |

|---------------------------------------------------------------|

| Chapter 5: Micro-architecture of Memory System                |

| 5.1: Memory System Micro-Architecture and its Partitioning    |

| 5.2: Design Hierarchy                                         |

| Chapter 6: Microarchitecture Specification                    |

| 6.1: Cache Unit51                                             |

| 6.1.1: I/O Description                                        |

| 6.2: Memory Arbiter                                           |

| 6.2.1: I/O Description55                                      |

| 6.2.2: Memory Arbiter State Diagram57                         |

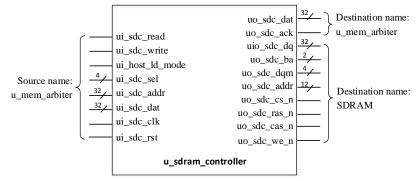

| 6.3: SDRAM Controller58                                       |

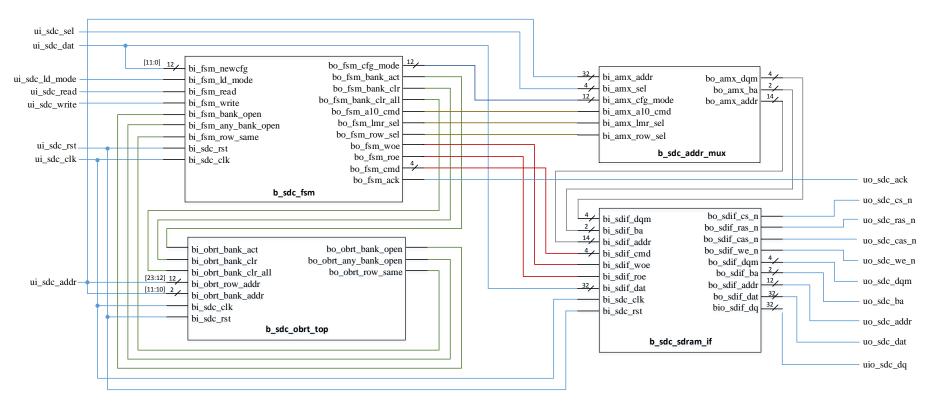

| 6.4: Block partitioning of SDRAM Controller61                 |

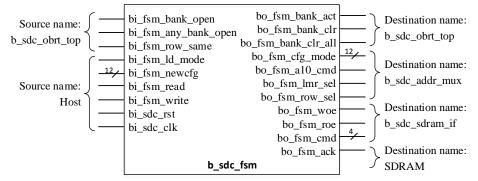

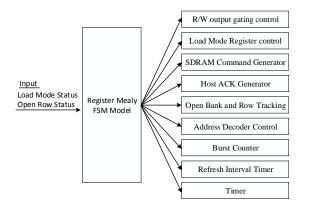

| 6.4.1: Protocol Controller62                                  |

| 6.4.2: Open Bank and Row Tracking (OBRT) Top67                |

| 6.4.3: Address Multiplexer71                                  |

| 6.4.4 SDRAM Interface Block Specification73                   |

| Chapter 7: Test and Verification75                            |

| 7.1: SDRAM Controller75                                       |

| 7.1.1: Test Plan75                                            |

| 7.1.2: Testbench Verilog code79                               |

| 7.1.3: Verification Result93                                  |

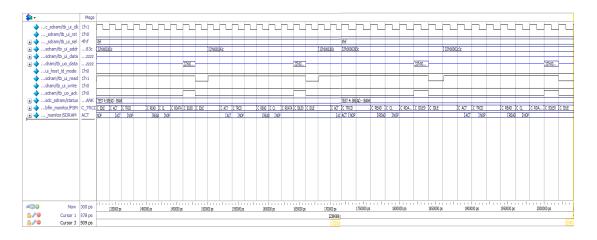

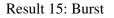

| 7.1.3: Simulation Result (Timing Diagram)95                   |

| 7.2: Memory System                                            |

| 7.2.1: Test Plan103                                           |

| 7.2.2: Testbench Verilog code104                              |

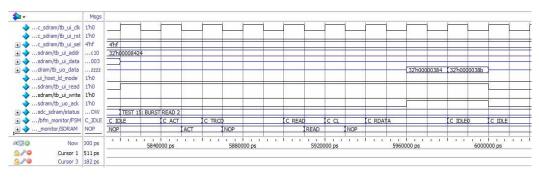

| 7.2.3: Simulation Result (Timing Diagram)111                  |

| Chapter 8: Discussions and Conclusion114                      |

| 8.1: Discussions                                              |

| 8.2: Conclusion                                               |

| 8.3: Future Work                                              |

| References                                                    |

| Appendices                                                    |

| Appendix A: System Specification Error! Bookmark not defined. |

| A.1 Feature                         | .118 |

|-------------------------------------|------|

| A.2 Naming Convention               | .118 |

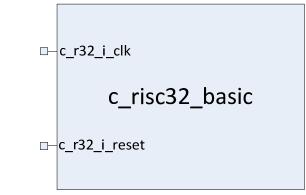

| A.3 Basic RISC32 processor          | .120 |

| A.3.1 Processor Interface           | .120 |

| A.3.2 I/O Pin Description           | .120 |

| A.4 System Register                 | .121 |

| A.4.1 General Purpose Register      | .121 |

| A.4.2 Special Purpose Register      | .121 |

| A.4.3 Program Counter Register      | .121 |

| A.5 Instruction Format              | .122 |

| A.6 Addressing Mode                 | .123 |

| A.7 Instruction Set and Description | .124 |

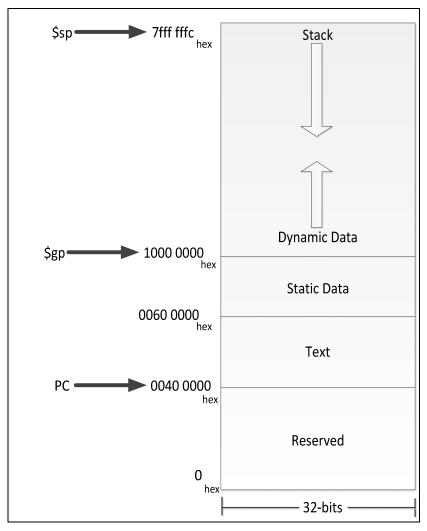

| A.8 Memory Map                      | .126 |

| A.9 Operating Procedure             | .127 |

## **List of Tables**

## LIST OF TABLES

| Table Number             | Title                                                              | Page                      |

|--------------------------|--------------------------------------------------------------------|---------------------------|

|                          | Command and DQM operation ( <i>A</i> itions (Adapted from [10])Err | ·                         |

| Table 2.9.3: Output or E | Schaviors Corresponding to the Sta                                 | ates (Adapted from [10])  |

|                          | Err                                                                | or! Bookmark not defined. |

| Table 4.4 Output or Beh  | avior to the Memory Arbiter FSM                                    | 1Error! Bookmark not      |

| defined.                 |                                                                    |                           |

| Table 4.5 Comparison b   | etween 'Big 3' Simulators                                          |                           |

| Table 4.7.1 Gantt chart  | for Project I                                                      |                           |

| Table 4.7.2 Planning Ga  | ntt chart for Project II                                           |                           |

| Table 5.1: Formation of  | a design hierarchy for 32-bit Men                                  | nory System 49            |

| Table 6.1.1: Cache Unit  | I/O Descriptions                                                   |                           |

| Table 6.2.1: Memory A    | rbiter I/O Descriptions                                            |                           |

| Table 6.2.3: State Defin | ition                                                              |                           |

| Table 6.2.4: Output or E | Sehaviors Corresponding to the Sta                                 | ates Error! Bookmark not  |

| defined.                 |                                                                    |                           |

| Table 6.3.1: SDRAM I/    | O Descriptions                                                     |                           |

| Table 6.4.1.1: Protocol  | Controller Input/ Output Pin Desc                                  | riptions 64               |

| Table 6.4.1.4: Output or | Behaviors Corresponding to the S                                   | StatesError! Bookmark not |

| defined.                 |                                                                    |                           |

| Table 6.4.2.1: OBRT To   | p Input /Output Pin Descriptions.                                  |                           |

| Table 6.4.2.4: OBRT In   | put/ Output Pins Descriptions                                      |                           |

| Table 6.4.2.5: OBRT In   | portant Registers                                                  |                           |

| Table 6.4.3.1: Address I | Multiplexer Input/ Output Pin Des                                  | criptions72               |

|                          | Interface I/ O pin descriptions                                    | -                         |

|                          | ontroller Full Chip Test Plan                                      |                           |

| Table A.1 RISC32 featu   | ires                                                               |                           |

| Table A.2 Naming Conv    | vention                                                            |                           |

| Table A.3 Basic RISC3    | 2 Input Pins Description                                           |                           |

|                          | 2                                                                  |                           |

|                          | ster                                                               |                           |

| Ũ                        | uction set                                                         |                           |

| Table A.8 Memory Map     | )                                                                  |                           |

# List of Figures

### LIST OF FIGURES

| Figure Number              | Title                                                | Page |

|----------------------------|------------------------------------------------------|------|

| Figure 2.1: The Memory     | Hierarchy (Adapted from [4])                         | 14   |

| •                          | anization (Adapted from [4])                         | 15   |

| ••••                       | diagram (Adapted from [11])                          | 16   |

| Figure 2.4: 128Mb bank     | s SDRAM Block diagram (Adapted from [10])            | 17   |

| Figure 2.5: SDRAM Cor      | ntroller Block Diagram (Adapted from [10])           | 18   |

| Figure 2.5.1: Write Timi   | ng Diagram                                           | 20   |

| Figure 2.5.2: Read Timin   | ng Diagram                                           | 21   |

| Figure 2.6: Connection b   | between Cache controller and SDRAM controller        | 21   |

| Figure 2.7: Mode Regist    | er Definition (Adapted from [14])                    | 23   |

| Figure 2.8.1: Micro-Arcl   | hitecture Level Design (Unit Level)                  | 24   |

| Figure 2.8.2: Interface of | f Memory Arbiter                                     | 24   |

| Figure 2.9: Initialization | Protocol FSM (Adapted from [10])                     | 25   |

| Figure 4.1: General Desi   | gn Flow without Logic Synthesis and Physical Design. | 28   |

| Figure 4.2.1: INIT_FSM     | (Adapted from [13])                                  | 31   |

| Figure 4.2.2: CMD_FSM      | (Adapted from [13])                                  | 32   |

| Figure 4.2.3: Timing dia   | gram for Divide by 3 (N=2)                           | 33   |

| Figure 4.2.4: Divide by 3  | 3 using T Flip-flops                                 | 33   |

| Figure 4.3: The interface  | e of Arbiter and Two Cache units                     | 34   |

| Figure 4.4 State diagram   | of Memory Arbiter                                    | 35   |

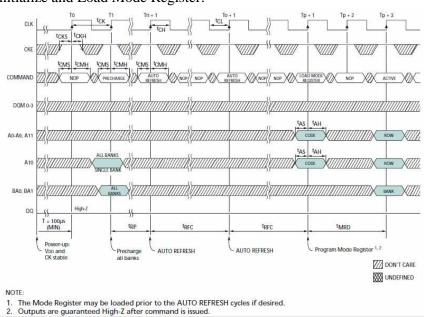

| Figure 4.6.F1: Initialize  | and Load Mode Register                               | 38   |

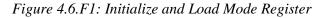

| Figure 4.6.F2: Auto Refi   | resh Mode                                            | 38   |

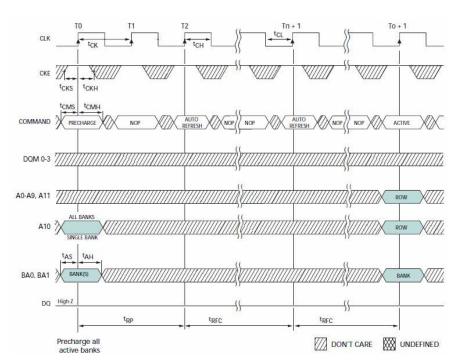

| Figure 4.6.F3: Self-Refre  | esh Mode                                             | 39   |

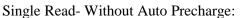

| Figure 4.6.F4: Single Re   | ad- Without Auto Precharge                           | 39   |

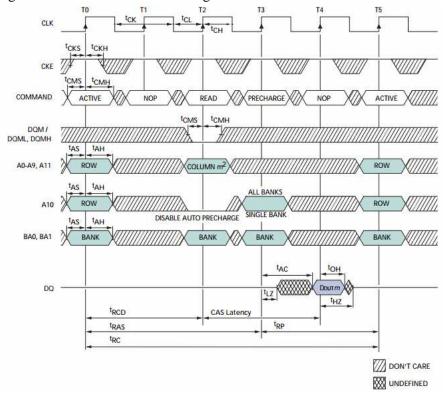

| Figure 4.6.F5: Read- Wi    | th Auto Precharge                                    | 40   |

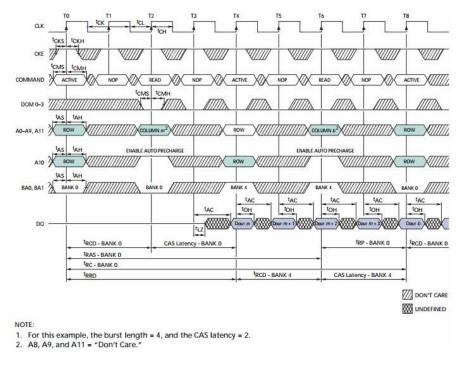

| Figure 4.6.F6: Alternatir  | ng Bank Read Accesses                                | 40   |

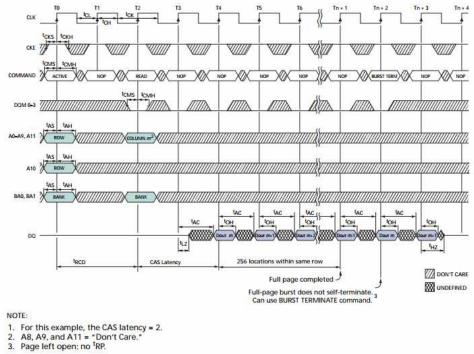

| Figure 4.6.F7: Read – Fu   | ıll page Burst                                       | 41   |

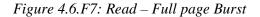

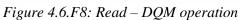

| Figure 4.6.F8: Read – D    | QM operation                                         | 41   |

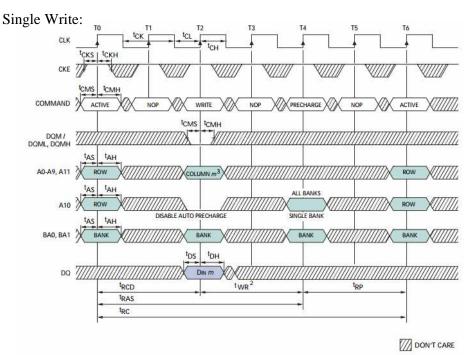

| Figure 4.6.F9: Single W    | rite                                                 | 42   |

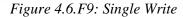

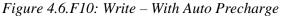

| Figure 4.6.F10: Write –    | With Auto Precharge                                  | 42   |

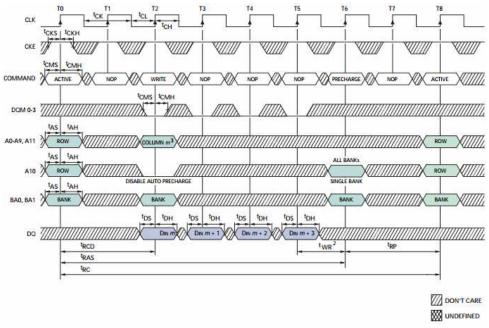

| Figure 4.6.F11: Write –    | Without Auto Precharge                               | 43   |

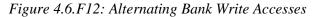

| Figure 4.6.F12: Alternat   | ing Bank Write Accesses                              | 43   |

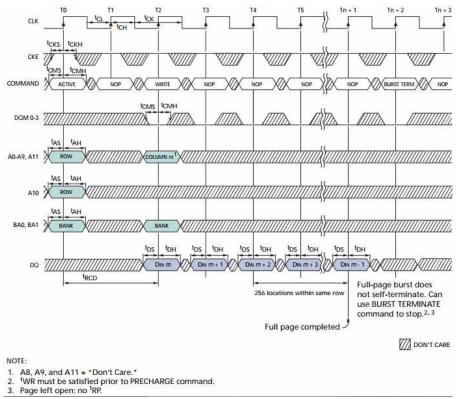

| Figure 4.6.F13: Write –    | Full Page Burst                                      | 44   |

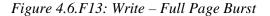

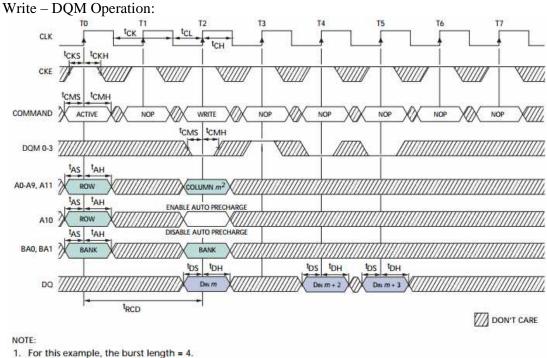

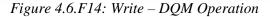

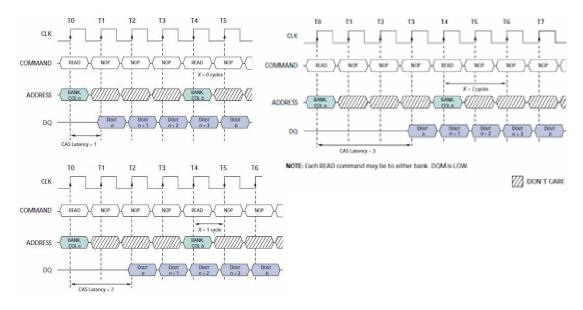

| Figure 4.6.F14: Write –    | DQM Operation                                        | 44   |

| Figure 4.6.F15: Consecu    | tive Read Burst                                      | 45   |

| Figure 4.6.F16: Termina    | ting a Read Burst                                    | 45   |

| Figure 5.0: Memory Sys     | tem Micro-Architecture and its Partitioning          | 48   |

Faculty of Information and Communication Technology, UTAR

| Figure 6: Unit Partitioning of Memory System                           | 50          |

|------------------------------------------------------------------------|-------------|

| Figure 6.1: Cache Unit Block Diagram                                   | 51          |

| Figure 6.2: Memory Arbiter Block Diagram                               | 54          |

| Figure 6.2.2: Memory Arbiter State Diagram                             | 57          |

| Figure 6.3: SDRAM Controller Block Diagram                             | 58          |

| Figure 6.4: The Micro-Architecture of the SDRAM Controller             | 61          |

| Figure 6.4.1: Protocol Controller Block Diagram                        | 62          |

| Figure 6.4.1.2.F1: A simplified view on the Protocol Block             | 64          |

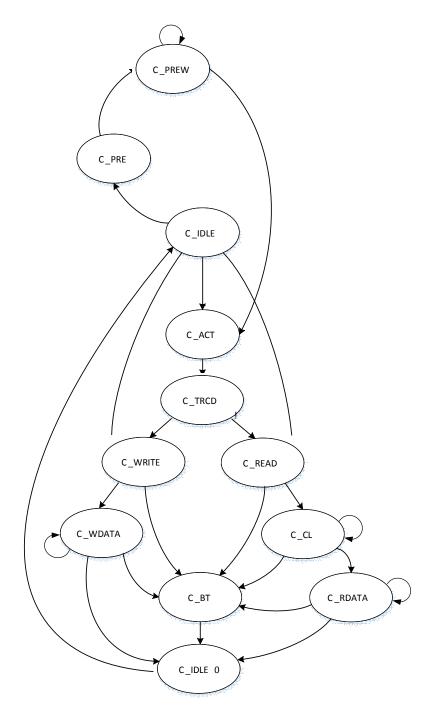

| Figure 6.4.1.2.F2: Initialization Protocol FSM                         | 65          |

| Figure 6.4.1.2.F3: Conceptual Model of Command Protocol FSM Error! E   | Bookmark    |

| not defined.                                                           |             |

| Figure 6.4.1.2.F4: Auto-Refresh Control sub-FSM Error! Bookmark no     | ot defined. |

| Figure 6.4.1.2.F5: Load Mode Control sub-FSM Error! Bookmark no        | ot defined. |

| Figure 6.4.1.2.F6: Open Bank and Row Tracking Control sub-FSM          | 66          |

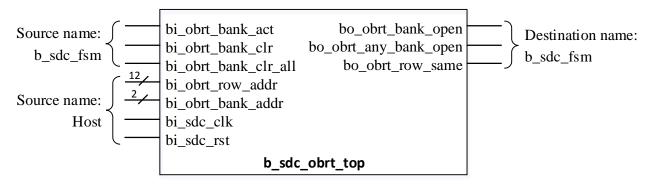

| Figure 6.4.2: OBRT Top Block diagram                                   | 67          |

| Figure 6.4.2.2: OBRT Top Internal Block diagram Error! Bookmark no     | ot defined. |

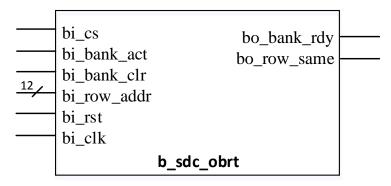

| Figure 6.4.2.3: OBRT Sub-block Diagram                                 | 69          |

| Figure 6.4.2.6: OBRT Internal Block diagram Error! Bookmark no         | ot defined. |

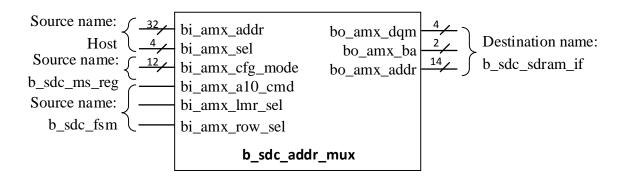

| Figure 6.4.3: Address Multiplexer Block Diagram                        | 71          |

| Figure 6.4.3.2: Address Multiplexer Internal Block diagram Error! Book | mark not    |

| defined.                                                               |             |

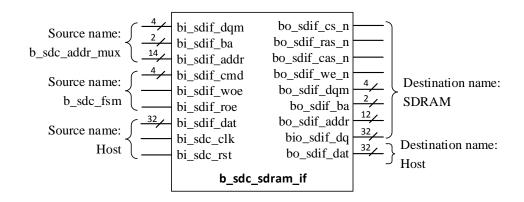

| Figure 6.4.4: SDRAM Interface Block Diagram                            | 73          |

| Figure 6.4.4.2: SDRAM Interfaces Internal Block diagram Error! Book    | mark not    |

| defined.                                                               |             |

| Figure A.3 Block diagram for RISC32-basic processor                    | 120         |

| Table A.5 Instruction Type                                             | 122         |

| Figure A.6 RISC32 Addressing Mode.                                     | 123         |

| Figure A.8 Memory map for Kuseg section, accessible without CP0        | 127         |

## **List of Abbreviations**

| ASIC  | Application-Specific Integrated Circuit            |

|-------|----------------------------------------------------|

| CPU   | Central Processing Unit                            |

| DRAM  | Dynamic Random-Access Memory                       |

| FSM   | Finite State Machine                               |

| HDL   | Hardware Description Language                      |

| ISA   | Instruction Set Architecture                       |

| Inc   | Incorporated                                       |

| I/O   | Input /Output                                      |

| MIPS  | Microprocessor without Interlocked Pipeline Stages |

| MMU   | Memory Management Unit                             |

| PSP   | Sony Playstation Portable                          |

| RISC  | Reduced Instruction Set Computer                   |

| RTL   | Register Transfer Level                            |

| SoC   | System-on-Chip                                     |

| SDRAM | Synchronous Dynamic Random-Access Memory           |

| SRAM  | Static Random-Access Memory                        |

| TLB   | Translation Lookaside Buffer                       |

| VCS   | Verilog Compiled code Simulator                    |

| VHDL  | VHSIC Hardware Description Language                |

| VHSIC | Very High Speed Integrated Circuit                 |

### **Chapter 1: Introduction**

#### **1.1: Background**

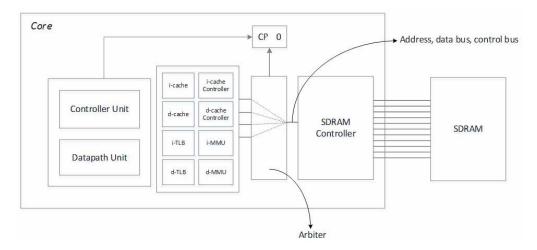

With the widening gap between processor and memory speeds, system performance has become gradually more reliant upon the efficient use of memory hierarchy [1]. Many computations executed on current machine are often than not limited by the response of the memory system rather than the speed of the processor [2]. The introduction of high speed cache into the memory hierarchy is to bridge this speed gap. However, this introduction is not perfectly without flaw. By organizing memory system into hierarchy, it also indicate more complex analysis have to be done on the performance of the memory system. Nevertheless, since the benefit brought forward by implementing hierarchical ordering in memory design outshone its flaws [3-4], it is unavoidable to use this method in our memory system which is recently compiled and interfaced using Verilog [5]. Therefore, our project will be focused on the design and the implementation of a 32-Bit Memory System in particular the integration of caches, cache controllers, Translation Lookaside Buffer (TLB), Memory Management Unit (MMU), SDRAM and SDRAM controllers, and the verification for the memory system integrated to a Reduced Instruction Set Computers 32-bit (RISC32) processor. RISC32 is a 32-bit processor which is compatible to the MIPS ISA compatible. It runs a subset of MIPS instructions set, which uses small and highly-optimized set of instructions.

#### **1.1.2 MIPS – a RISC processor**

MIPS (Microprocessor without Interlocked Pipelined Stage) is a RISC (Reduced Instruction Set Computers) processor which use hardware implementation to directly execute instructions, without microprogrammed control. MIPS is widely used in digital consumer, home networking, personal entertainment, communications and business applications, such as Sony Playstation Portable (PSP), Smart Tab 1 (Karbonn Mobiles) and *Linksys wireless router which primarily used in MIPS implementations. MIPS can be develop using Verilog* – a hardware description language (HDL).

### **1.2: Motivation**

The motivations to initiate the project are due to the following limitation:

- Microchip design companies develop microprocessors cores as Intellectual Property or IP for commercial purposes. The microprocessor IP includes information on the entire design process for the front-end (modeling and verification) and back-end (physical design) integrated circuit (IC) design. These are trade secrets of a company and certainly not made available in the market at an affordable price for research purposes.

- The microprocessor cores that are freely available from source such as the miniMIPS (www.opencores.org), the PH processor (Leicester University), uCore (www.opencores.org), Yellow Star (Manchester University), etc are incomplete in documentation and therefore do not provide good support for reuse. It is difficult to modify and extent the design for a specific applications under research. Apart from that, the cores are not well modeled and developed.

- The verification specification for a freely available RISC microprocessor core that is available on the Internet is not well developed and complete. Therefore, without a good verification specification, the verification process will be slow and hence, will slow down the overall design process.

- Since the freely available microprocessor cores and the verification are not well developed, this has affected the physical design phase. The physical design of the microprocessor cores is not well developed and complete.

The RISC32 project will look into the above problems, to create a 32-bit RISC corebased development environment to assist research work in the area of application specific hardware modeling. The RISC32 processor is a MIP-compatible ISA processor. In the RISC32 project, it is divided into several units based on the MIPS architecture. Up to date, a basic central processing unit (CPU) has been modeled at Register Transfer Level (RTL) using Verilog HDL (VHDL) and verified using a bus functional model. During the verification process, a high -level memory system unit model was developed and temporarily used. So currently, an RTL memory system unit model is not available.

#### **1.2.1: Problem Statement**

At present, a basic central 32-bit memory system that has been modeled at RTL using VHDL is the SDRAM controller design that compatible with Micron SDR SDRAM MT48LC4M32B2. However, the protocol controller block of SDRAM controller design is rather complicated and need to be resolved. Another problem has been encountered is the SDRAM controller can currently support a single cache, but typically RISC32 processor design has separated caches. Those caches are i-cache, d-cache, i-TLB, d-TLB, which will need to access to the SDRAM. This implies the limitation of the SDRAM controller interfaces and its redesigning is needed. Hence, the design of memory arbiter is also required to allow the shared bus for multiple caches.

### **Chapter 2: Literature Review**

### **2.1: Memory Hierarchy**

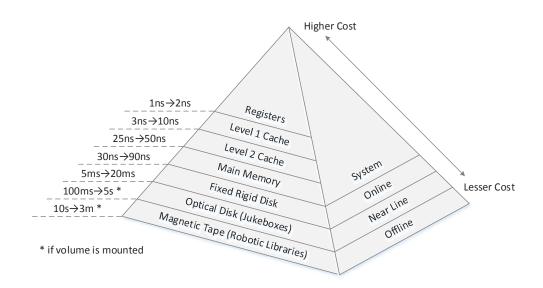

Computer memory is implemented with hierarchy (memory hierarchy) to take the advantage of principle of locality. There are three primary technologies used in building memory hierarchies. Main memory is implemented from DRAM, levels closer to processor (cache) use SRAM. The third technology is magnetic disk which is used to implement largest and slowest in the hierarchy. The price per bit and access time of these technologies vary widely. Therefore, we can take advantage by implementing memory hierarchy. Figure below shows the faster memory is close to the processor, while the slower memory is below it. This helps to present the user with more memory as is available in cheapest technology while it also provides the speed from the fast memory.

Figure 2.1: The Memory Hierarchy (Adapted from [4])

#### 2.2: Processor and Main Memory Interfacing

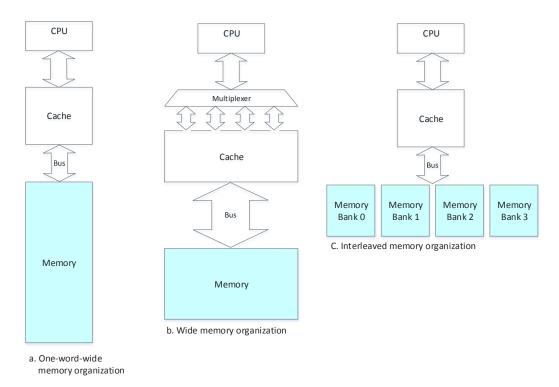

The processor is connected to the main memory by a bus system [4] and the bandwidth of the bus system has a significant impact on miss penalty. This is due to the clock rate for the bus is always slower than the processor as much as a factor of 10. Therefore, the selection of memory organization to be use in processor is important in deciding the performance of the processor.

Figure 2.2 below shows three types of available memory organizations which are one-word-wide memory, wide memory and interleaved memory organization. If a cache block of four words and in a) one-wide memory organization, it only can fetch one word per time. That is the main memory have to access 4 times to fetch all data require from the cache. In b) wide memory organization allows the require data fetch with parallel access in a widening bandwidth of bus system between memory and the processor. If a cache block of four words and c) interleaved memory organization, it is capable to fetch four words to access the main memory at once.

Figure 2.2: Memory Organization (Adapted from [4])

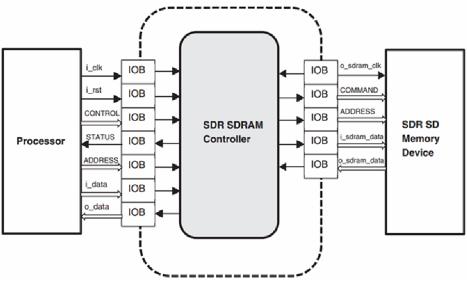

### 2.3: SDRAM Controller System Background

The overall figure of SDR SDRAM controller system is shown in the figure 2.3 below, which is describing a brief on how SDRAM controller can communicate with processor each other and interface with the SDRAM.

Figure 2.3: System block diagram (Adapted from [11])

### **2.4: SDRAM**

Synchronous Dynamic Random Access Memory (SDRAM) is a type of DRAM that has a synchronous interface. There are two major types of SDRAM which can be distinguished by their data transfer rate. Single data rate (SDR) SDRAM transfers data on the rising edge of the clock, and double data rate (DDR) SDRAM transfers data on both rising and falling edge.

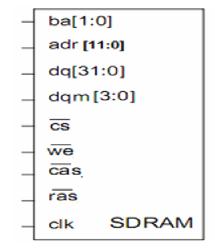

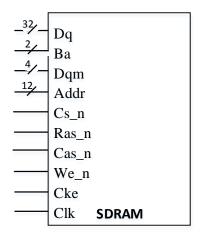

Figure 2.4 shows the pins for a conventional 1M x 32-bit x 4 banks SDRAM which is referring to the Micron. Pin ba(1:0) is used to select the 4 internal memory banks within the SDRAM while adr(11:0) is used as an input to send column address, row address and configuration setting to the SDRAM. The SDRAM has adopted bidirectional data line, dq, for write transfer and read transfer. This is because the SDRAM can only do one of the operations at a time. The granularity of a bus is defined as the smallest transfer can be done by that bus. According to [12], the granularity of a SDRAM is 8-bit. This is accomplished using the data masking

pin,dqm(3:0). The data masking pin is used to select which byte of the 32-bit bidirectional data line, dq, is valid.

For example, if dqm = 0001 (binary), the valid 8-bit data is located at dq(7:0). Here is another example, if dqm = 1100 (binary), the valid 16-bit data is located at dq(31:16). As mentioned, since the smallest transfer is 8-bit, the granularity of this SDRAM is 8-bit. As a comparison, the customized SDRAM [11] has a granularity of 32-bit for its 32-bit write data line and 256-bit granularity for its 256-bit read data line. This also means that the customized SDRAM cannot support byte addressing.

Figure 2.4: 128Mb banks SDRAM Block diagram (Adapted from [10])

To select the SDRAM, the cs (active low) pin is used. Meanwhile active low command signals (we, cas and ras) are used to request operations from the SDRAM. The list of commands available in SDRAM is shown in Table 2.4.

| Name (Function)                                        | CS# | RAS# | CAS# | WE# | DQM | ADDR     | DQ     | Notes |

|--------------------------------------------------------|-----|------|------|-----|-----|----------|--------|-------|

| COMMAND INHIBIT (NOP)                                  | н   | Х    | Х    | Х   | X   | Х        | Х      |       |

| NO OPERATION (NOP)                                     | L   | н    | н    | н   | X   | Х        | х      |       |

| ACTIVE (select bank and activate row)                  | L   | L    | н    | н   | X   | Bank/row | х      | 2     |

| READ (select bank and column, and start READ burst)    | L   | н    | L    | н   | L/H | Bank/col | х      | 3     |

| WRITE (select bank and column, and start WRITE burst)  | L   | н    | L    | L   | L/H | Bank/col | Valid  | 3     |

| BURST TERMINATE                                        | L   | н    | н    | L   | X   | Х        | Active | 4     |

| PRECHARGE (Deactivate row in bank or banks)            | L   | L    | н    | L   | X   | Code     | Х      | 5     |

| AUTO REFRESH or SELF REFRESH (enter self refresh mode) | L   | L    | L    | н   | X   | Х        | Х      | 6, 7  |

| LOAD MODE REGISTER                                     | L   | L    | L    | L   | X   | Op-code  | х      | 8     |

| Write enable/output enable                             | X   | Х    | Х    | Х   | L   | х        | Active | 9     |

| Write inhibit/output High-Z                            | X   | Х    | Х    | Х   | н   | Х        | High-Z | 9     |

Table 2.4: Truth Table - Command and DQM operation (Adapted from [14])

### **2.5: SDRAM controller**

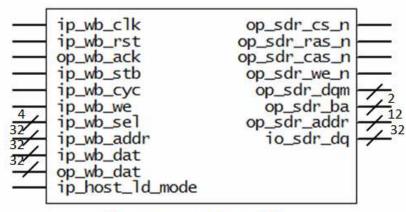

The SDRAM Controller is located between SDRAM and the host, provide proper commands for SDRAM initialization, read/write accesses and memory refresh. The host can be either a microprocessor or a user's proprietary module interface. The SDRAM Controller has been previously modele\d based on industry standard WISHBONE SoC interface [10].

## sdram controller

Figure 2.5: SDRAM Controller Block Diagram (Adapted from [10])

| Pin name: ip_wb_clk                                                                   |

|---------------------------------------------------------------------------------------|

| Path: Memory Bus Clock -> SDRAM Controller                                            |

| Description: Wishbone Clock Input                                                     |

| Pin name: ip_wb_rst                                                                   |

| Path: System Reset -> SDRAM Controller                                                |

| Description: Wishbone Synchronous reset                                               |

| Pin name: ip_wb_cyc                                                                   |

| Path: Host -> SDRAM Controller                                                        |

| Description: When asserted, this pin indicates that a valid bus cycle is in progress. |

| Pin name: ip_wb_stb                                                                   |

| Path: Host -> SDRAM Controller                                                        |

| Description: When asserted, this pin indicates that the SDRAM controller is selected. |

| Pin name: ip_wb_we                                                                    |

| Path: Host -> SDRAM Controller                                                        |

| <b>Description:</b> When asserted, this pin indicates that the current cycle is READ. |

| When deasserted, it indicates WRITE.                                                  |

| Pin name: op_wb_ack                                                                   |

| Path: SDRAM Controller -> Host                                                        |

| Description: When asserted, it indicates that the current READ or WRITE is            |

| successful.                                                                           |

| Pin name: ip_wb_sel                                                                   |

| Path: Host -> SDRAM Controller                                                        |

| Description: This signal indicates where valid data is placed on the input data line  |

|                                                                                       |

#### BIT (Hons) Computer Engineering

Faculty of Information and Communication Technology, UTAR

| (ip_wb_dat) during WRITE cycle and where it should present on the output data line                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (op_wb_dat) during READ cycle. The array boundaries are determined by the                                                                                        |

| granularity of a port. In this SDRAM controller, 8-bits granularity is used and all the                                                                          |

| data ports are 32-bits. Therefore, there would be 4 select signals with the boundaries                                                                           |

| of ip_wb_sel(3:0). Each individual select signal correlates to one of 4 active bytes on                                                                          |

| the 32-bits data port.                                                                                                                                           |

| Pin name: ip_wb_addr                                                                                                                                             |

| Path: Host -> SDRAM Controller                                                                                                                                   |

| <b>Description:</b> The address input is used to pass the memory address from the host.                                                                          |

| Pin name: ip_wb_dat                                                                                                                                              |

| Path: Host-> SDRAM Controller                                                                                                                                    |

| <b>Description:</b> This pin is used to pass WRITE data from the host.                                                                                           |

| Pin name: op_wb_dat                                                                                                                                              |

| Path: SDRAM Controller -> Host                                                                                                                                   |

| <b>Description:</b> This pin is used to output READ data from the SDRAM.                                                                                         |

| Pin name: ip_host_ld_mode                                                                                                                                        |

| Path: SDRAM Controller -> Host                                                                                                                                   |

| <b>Description:</b> This pin is asserted to load a new mode into the SDRAM.                                                                                      |

| Pin name: op_sdr_cs_n                                                                                                                                            |

| Path: Host -> SDRAM                                                                                                                                              |

| Description: SDRAM chip select                                                                                                                                   |

| Pin name: op_sdr_ras_n                                                                                                                                           |

| Path: Host -> SDRAM                                                                                                                                              |

| <b>Description:</b> SDRAM row address select                                                                                                                     |

| <b>Pin name:</b> op_sdr_cas_n                                                                                                                                    |

| Path: Host -> SDRAM                                                                                                                                              |

| <b>Description:</b> SDRAM column address select                                                                                                                  |

| Pin name: op_sdr_we_n                                                                                                                                            |

| Path: Host -> SDRAM                                                                                                                                              |

| <b>Description:</b> SDRAM write enable.                                                                                                                          |

| Pin name: op_sdr_addr                                                                                                                                            |

| Path: Host -> SDRAM                                                                                                                                              |

| <b>Description:</b> This pin is used as an address output to the SDRAM. The address will                                                                         |

| be segmented into row, column and bank before being sent out through this pin.                                                                                   |

| Pin name: op_sdr_ba                                                                                                                                              |

| Path: Host -> SDRAM                                                                                                                                              |

|                                                                                                                                                                  |

| <b>Description:</b> This pin is used to select the bank within the SDRAM. There are a total of 4 honks within the SDRAM and each of them energies independently. |

| of 4 banks within the SDRAM and each of them operates independently.                                                                                             |

| Pin name: op_sdr_dqm                                                                                                                                             |

| Path: Host -> SDRAM                                                                                                                                              |

| <b>Description:</b> This pin is used to select which bits of the data line (io_sdr_dq) to be                                                                     |

| masked.                                                                                                                                                          |

| Pin name: io_sdr_dq                                                                                                                                              |

| Path: Host -> SDRAM                                                                                                                                              |

| <b>Description:</b> This data line is a bidirectional line to receive READ data or send                                                                          |

| WRITE data.                                                                                                                                                      |

#### 2.5.1: Read/Write Cycle Timing diagram

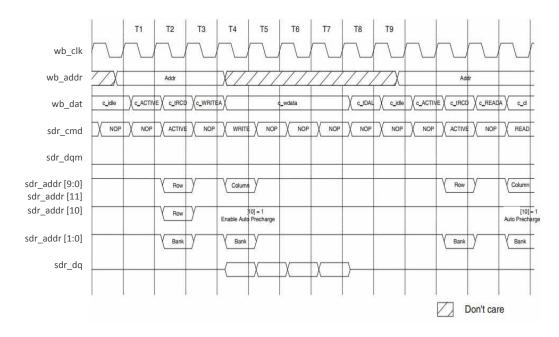

Figure 2.5.1 indicates the timing diagram for writing a burst of four data words to the SDRAM. The wb\_dat indicates the command received from host is in the idle state at the begining. At T1, the system places Address on the bus continue until T3. After SDRAM detects ACTIVE command and row address at T2 and after RAS-to-CAS delay (tRCD), SDRAM receives the WRITE command and the first data comes in. The four words burst write is done at T8.

#### Figure 2.5.1: Write Timing Diagram

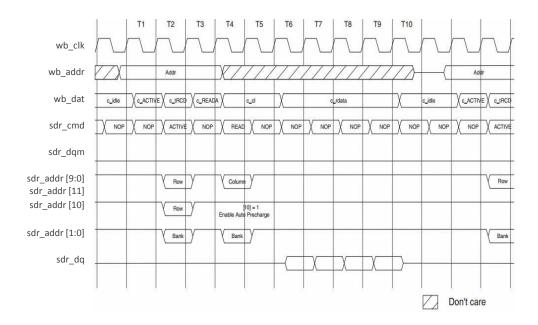

Figure 2.5.2 indicates the timing diagram for reading a burst of four data words to the SDRAM. At T1, the system places Address on the bus until T3. After SDRAM detects the ACTIVE command and row address at T2, and after RAS-to-CAS delay, SDRAM receives the READ command and the column address at T4. After CAS latency delay, the SDRAM starts to receive first data at T6. The four words burst read are completed in T9.

Figure 2.5.2: Read Timing Diagram

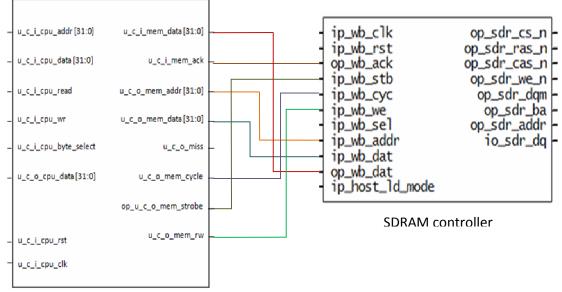

### 2.6: SDRAM Controller and Cache Controller Interfacing

The following figure 2.6 shows the interface of SDRAM controller to the cache unit.

Cache controller

Figure 2.6: Connection between Cache controller and SDRAM controller

ip\_host\_ld\_mode indicates as an enable pin to load new mode by passing write data from the host (ip\_wb\_dat). If the current load mode register (LMR) command is same with the previous mode, the register will retain the same configuration and not going to load any new mode to the SDRAM. But if both modes are differences, the

ip\_host\_ld\_mode will be asserted high to allow a new mode load to the SDRAM. This feature is required in order to reduce LMR time delayed whenever the same mode is appeared in the next stage.

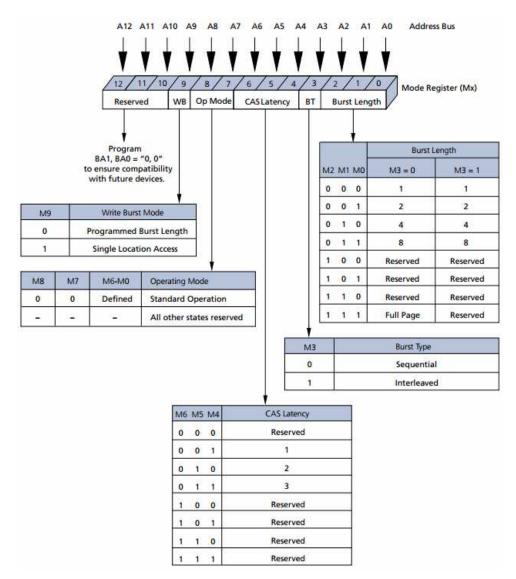

#### 2.7: Load Mode Register

The pins of the SDRAM adr[11:0]and command signals (cs, we, cas and ras) are used to configure the mode register which can define the specific mode of operation for SDRAM via the LOAD MODE REGISTER (LMR) command and the information stored will be retain until it has been reprogrammed or the device has been powered off. The definition includes the selection of burst length, burst type, CAS latency, operating mode and write burst mode. Burst indicates the technique used as continuous read or continuous write the data. An example of read operation with burst is when the burst length is set to be 4; the data will be read 4 times continuously. And the sequence of data will be read or write operation and either in a sequential or interleaved order. The figure 2.7 will show the data status to be configured.

The description of each Mode Register definition from figure 2.4.2 is listed as below:

#### Burst Length

To determine the maximum number of column locations that can be accessed for a given READ or WRITE command.

#### Burst Type

Access within a given burst can be programmed to be either sequential burst or interleaved burst to be adopted by SDRAM. The ordering of accesses within a burst is determined by burst length, burst type, and the starting column address.

#### CAS Latency

Delay in clock cycles between registration of a READ command and the availability of the first piece of output data. It can only be set to 2 or 3 clock cycles.

#### Operating Mode

To select the operating mode should be used in the SDRAM. Currently there is only normal operating mode is available for use.

#### Write Burst Mode

When the mode is asserted high, the burst length is programmed as READ burst or WRITE burst. If it is asserted low, the programmed burst length applies to READ burst, but WRITE access are single-location access (non-burst). The burst length that mentioned is referred to the M0-M2.

Figure 2.7: Mode Register Definition (Adapted from [14])

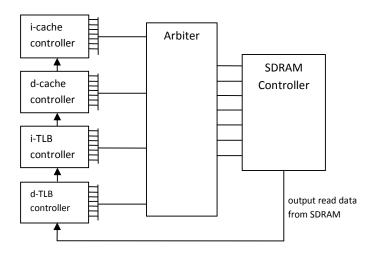

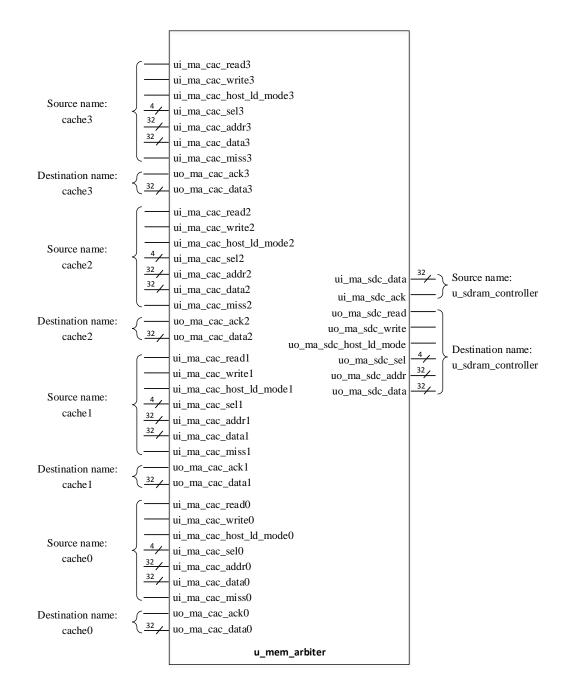

#### 2.8: Memory Arbiter

The Figure 2.6 interface that shows in previously is merely an explanation on how SDRAM controller is connected with a cache. If there are independent requesting processor units connecting to the SDRAM, we required a memory arbiter to resolve the shared bus conflict. The memory arbiter allows one MASTER to access SDRAM controller at single time while the other MASTERs have to be waiting. It is given a pattern or ordering for each of the MASTER to access first. The shared bus usually uses a priority or a round robin arbiter. These grant the shared bus on a priority or equal basis. And a timeout is given to ensure that the bus does not remain locked at particular MASTER for duration greater than the time out period.

Figure 2.8.1: Micro-Architecture Level Design (Unit Level)

Figure 2.8.2: Interface of Memory Arbiter

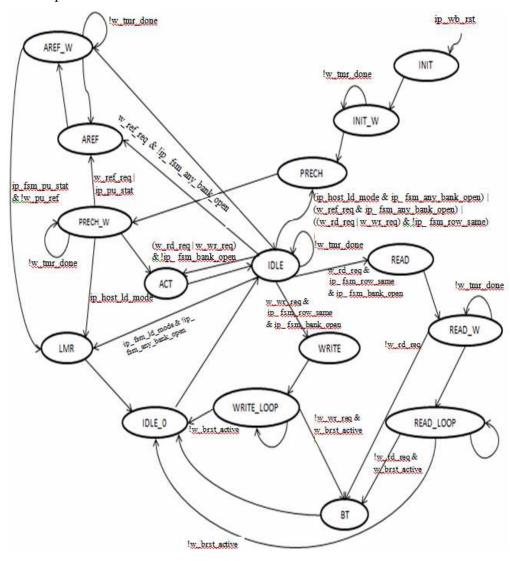

#### 2.9: Protocol Controller State Diagram

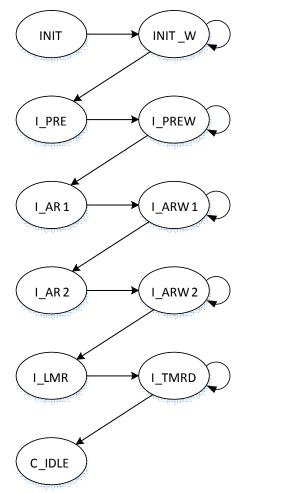

A 32-Bit Memory System of SDRAM controller was integrated by the previous work [10]. However there was an attempt to integrate this SDRAM controller, the design has its own readability issue.

The SDRAM controller was designed in the previous work has consequently leads to the difficulty of understanding how the design protocol works in SDRAM controller. The design has a combination of SDRAM initialization and SDRAM command in the finite state machine (FSM). Therefore this project is initiated to create a better and easier analyzing SDRAM controller. In the figure below shows the FSM of SDRAM protocol in previous work.

Figure 2.9: Initialization Protocol FSM (Adapted from [10])

## **Chapter 3: Project Scope and Objectives**

### **3.1: Project Scope**

This project is to redesign the existing interface of memory system and processor. A completed 32-bit memory system will be delivered. There are two parts of works required to be improved, which are the design of SDRAM controller compatible with Micron SDRAM and compatible with current memory system design.

### **3.2: Project Objectives**

The project's objectives include:

- Analyze the 32-Bit Memory System organization for examining the scope of the integration done thus far. In addition, an appropriate test and testbench will be constructed to assist test analysis.

- Redesign the sub module of SDRAM controller Protocol Controller block Finite State Machine (PCB FSM) that compatible with Micron SDR SDRAM.

- Redesign the SDRAM controller to support multiple cached load mode configurations.

- Design of Memory Arbiter to allow the connection of differing caches to SDRAM controller.

- Verify the integration of the RISC32 processor and memory system by construct an appropriate test cases for direct test, integration test and random test.

### **3.3: Significance and Impact**

As a synopsis to the problem statement, there is a lack of well-developed and wellfounded 32-bit RISC microprocessor core-based development environment. The development environment refers to the availability of the following:

- A well-developed design document, which includes the chip specification, architecture specification and micro-architecture specification.

- A fully functional well-developed 32-bit RISC architecture core in the form of synthesis-ready RTL written in Verilog.

- A well-developed verification environment for the 32-bit RISC core. The verification specification should contain suitable verification methodology, verification techniques, test plans, testbench architectures etc.

- A complete physical design in FPGA with documented timing and resource usage information.

The project is an effort to develop the environment mentioned above: to be used as a multi-cycle pipelined RISC microprocessor core-based platform to support hardware modeling research work.

With the existing well-developed basic RTL model (which has been fully functionally verified), the verification environment and the design documents, a researcher can develop his research specific RTL model as part of the environment (whether directly modifying the internals of the processor or interface to the processor) and can quickly verify his model to obtain results, without having to worry about the development of the verification environment and the modeling environment. This can hasten the research work significantly. Relating exclusively to this project, the availability of a good methodology to help support memory system analysis makes it easier for any future improvement on the existing system.

## **Chapter 4: Methods/Technologies Involved**

### 4.1: Design Methodology

Design Methodology basically refers to the method of development of a system. It provides us with a set of guidelines to successfully carry out the design work. A good design methodology needs to ensure the following [8]:

- Correct Functionality

- Satisfaction of performance and power goals

- Catching bugs early

- Good documentation

The ideal design flow for this project would be the top-down methodology as shown in figure 4.1:

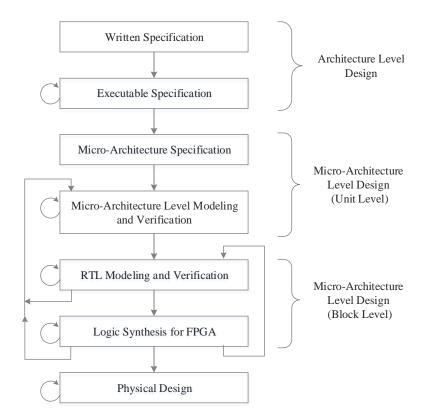

Figure 4.1: General Design Flow without Logic Synthesis and Physical Design.

Source: K.M. MOK [8]

### **4.1.1 Architecture Level Design**

Architecture Level Design is level where chip specifications are being developed. The level design includes the following two types, *written specification* and *executable specification*, which carry (refer to Appendix A):

- functionality / features

- Operating procedures and application

- Naming convention

- Pipeline chip interface and I/O description

- Memory map

- System register

- Supported instruction set (machine language)

- Instruction formats

- Addressing modes

### 4.1.2 Micro-Architecture Level Design (Unit Level)

Micro-Architecture Level Design can categorize into 2 phases, *Micro-Architecture specification* and *Micro-Architecture Level Modeling and Verification*. In the content of this level of design includes (refer to Appendix B):

- Design hierarchy

- Unit level functional partitioning (Datapath Unit, Instruction Fetch Unit, Control Unit, Instruction Memory Unit and Data Memory Unit)

- Worst case timing

- Full chip Verilog model

- Test plan

- Testbench

### 4.1.3 Micro-Architecture Level Design (Block Level)

In this level, RTL (Register Transfer Level) is developed. A micro-architecture specification of each unit, which used to describe the internal design of architecture block module. Micro-architecture specification may include information of:

- functionality / feature

- datapath unit interface and I/O pin description,

- internal operation, block / sub-block level functional partitioning (Register File Block, ALU Block, etc)

- Verilog model is later inserted

- Testbench and simulation result

After developed Micro-architecture Specification, RTL modeling with programming language can be start. Model can be simulate and verified with software. Verification includes development of test plan, timing verification and functionality verification. Hence designer can verify and modify the design to meet the chip specification.

### 4.2: Protocol Controller Block Design

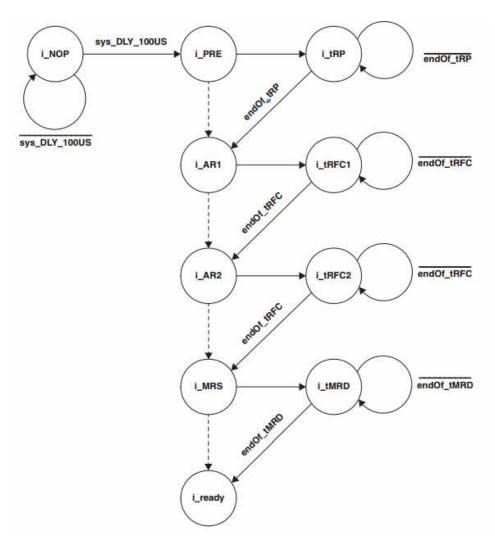

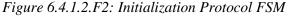

Instead of the design protocol discussed in the previous work from [10], the FSM also can be separated into two by using one-hot encoding FSM, which shows in the following figure 4.2.1 and figure 4.2.2.

The INIT\_FSM state machine from Figure 4.3.1 handles the SDRAM initialization. This initialization states begin with a NOP state, continued with PRECHARGE state, followed by AUTO REFRESH states, and then LOAD MODE REGISTER (LMR) states to configure SDRAM specific mode of operation. In each state consists of its delay time, and will be done by the timer. The auto refresh state use repeatedly [10] can be separated into two auto refresh to simplify the logic and state.

Figure 4.2.1: INIT\_FSM (Adapted from [13])

The CMD\_FSM state machine from Figure 4.2.2 handles commands such as read, write, and refresh of the SDRAM. The command FSM has its own auto refresh state, since the initialization and command FSM has been separated away. Other than that, the rest of the states are not much different with the previous work [10].

Figure 4.2.2: CMD\_FSM (Adapted from [13])

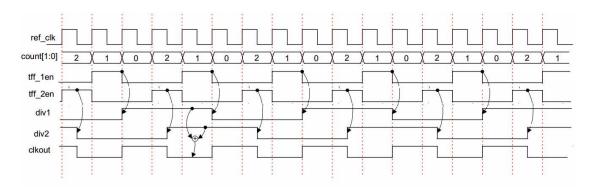

The signal sys\_DLY\_100US from Figure 4.2.1 indicates the system clock delayed for 100  $\mu$ s, which can be generated by the internal Phase-Locked Loop (PLL) by setting the proper PLL attributes (clock multiplication and division). An example of Clock divider with a 50% duty cycle can be generated as according to the following steps.

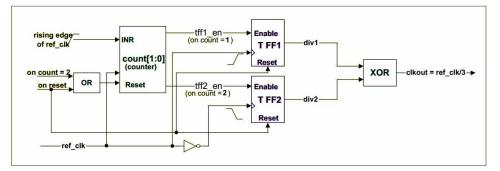

Firstly, the counts from N-1 to 0 count down counter must be created and always on the rising edge of input system clock. Secondly, toggle flip-flops TFFs are used and generate their enables. For an example the clock signal is divided by 3, TFF1 enable when count value is 1, TFF2 enable when count value is 2. Thirdly, the output of TFF1 (div1) triggered on rising edge of input clock whereas the output of TFF2 (div2) triggered on falling edge of input clock. Lastly, the final output signal is generated by the two clocks (div1 and div2) at half desired output frequency by undergoes XOR operation of the two waveforms together.

*Figure 4.2.3: Timing diagram for Divide by 3 (N=2)*

Figure 4.2.4: Divide by 3 using T Flip-flops

We can use the timer to create the exact delay time required for the SDRAM clock. To create the 50% duty cycle output clock delayed signal, we need to double up the input clock frequency use as referencing clock and perform the equation below:

$count \ value = \frac{output \ clock \ frequency}{100 \mu s \ delay \ time \ frequency} \, .$

For an example, the system clock speed has 100 KHz ( $10\mu$ s per clock), thus count value will count down from 9 to 0. Each round of count, the output delayed clock signal will toggle its previous state, in order to obtain a half clock cycle of the output.

### 4.3: Load Mode Configuration with Multiple Cache

There is a problem that needs to resolve, which is to redesign the SDRAM controller so it can support Load Mode configuration and allow multiple caches to access. The ip\_host\_ld\_mode is an enable pin to load new mode to the SDRAM. Caches need to share this pin. However, we can use one-hot method to separate the enable pin into individual pins and four individual load mode registers to store the configuration. For example if there are four caches, four ip\_host\_ld\_mode enable pins are connected to the caches respectively, and each enable pin is controlling its own load mode register. The i-cache load mode enable pin will be controlling the i-cache load mode register. Thus there will be four registers need to be created. But this method will rather increasing the hardware complexity.

A more efficient way is using only one enable pin and the register just keep its previous configuration. To decide whether to load a new mode to the SDRAM, the SDRAM controller need to check out for the current data and the previous one is either same or not. From the figure below aids to architecture view of how multiple caches can be connected to SDRAM controller.

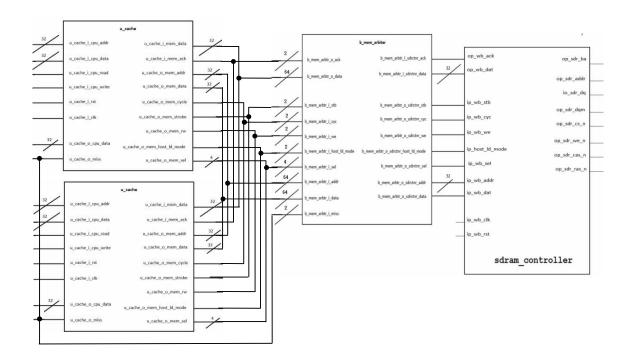

Figure 4.3: The interface of Arbiter and Two Cache units

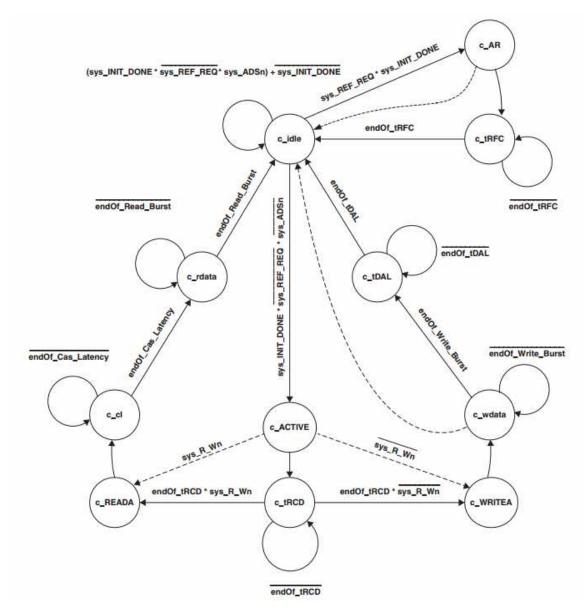

### **4.4: Design of Memory Arbiter**

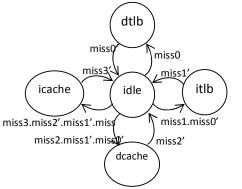

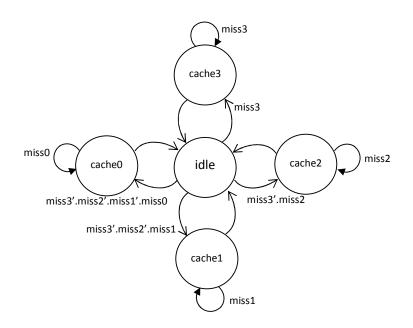

There are four independent caches that need to access to the SDRAM. And the priority can be given in the order d-tlb > i-tlb > d-cache > i-cache. If four of those caches sent a miss signal at the same time, the d-tlb will first to access SDRAM, then i-tlb will take turn, and followed by the d-cache, and the i-cache will come to the end. The state diagram of memory arbiter can be designed as figure below:

Figure 4.4 State diagram of Memory Arbiter

### **4.5: Designing Tools**

Since this project is using Verilog, which is a Hardware Description Language (HDL). Simulations tools that support Verilog HDL is required, tools that provide simulation environment to verify the functional and timing models of the design, and the HDL source code. There are a lot HDL simulator created by different company, which has their own advantages and disadvantages. In order to choose most appropriate design tools for this project, some researches had been done and the choices has been narrow into three choices, which are the best HDL simulation tools available on the market, they are also known as the 'Big 3' simulators, three major signoff-grade simulators which qualified for application-specific integrated circuit (ASIC) (validation) sign-off at nearly all semiconductor fabrications. They are:

- 1. Incisive Enterprise Simulator by Cadence Design Systems

- 2. ModelSim by Mentor Graphic

- 3. Verilog Compiled code Simulator (VCS) by Synopsys

| Simulator                   | Incisive Enterprise<br>Simulator | ModelSim                                            | VCS                          |

|-----------------------------|----------------------------------|-----------------------------------------------------|------------------------------|

| Performance & functionality | high                             | moderate                                            | High                         |

| Language Supported          | VHDL-2002<br>V2001<br>SV2005     | VHDL-2002<br>V2001<br>SV2005                        | VHDL-2002<br>V2001<br>SV2005 |

| Simulation run speed        | fastest                          | moderate                                            | faster                       |

| Price                       | Expensive                        | Cost Saving and<br>available for free<br>SE edition | Expensive                    |

### Table 4.5 Comparison between 'Big 3' Simulators

Due to the availability, affordability, platform supported and performance requirement, the suitable simulator for this project is *Modelsim SE 10.3a* which is a freeware of student edition and is enough for the designing requirement. Other simulators may offer good features too, but no free license is provided to the students and the cost of each license is normally about \$25000 and above which is unaffordable for a student.

## **4.6: Requirement Specification**

This SDRAM controller is designed depends on Micron SDRAM MT48LC4M32B2 (1 Meg x 32 x 4 Banks). The entire design of SDRAM controller will need to fulfill the following requirements, which able to perform:

- Auto-refresh , 4096-cycles refresh (15.6µs/row)

- Auto-precharge, includes read, write and auto refresh mode

- Bank and row tracking for 4 banks

- Programmable burst length: 1,2,4,8 or full page

- Addressing controls

- I/O data buffer for read and write

- Supports CAS Latency (CL) of 1,2 and 3

- Self-refresh mode

- Command Generator to SDRAM

- •

The SDRAM Controller design must provide input data for the Micron SDRAM as shown in the below:

Figure 4.6.1: Micron SDRAM Block diagram

Additional timing diagram appear in the following requirement specification section; these timing diagrams provide better information for SDRAM controller design.

Initialize and Load Mode Register:

Auto Refresh Mode:

Figure 4.6.F2: Auto Refresh Mode

#### Self-Refresh Mode:

Figure 4.6.F5: Read- With Auto Precharge

Alternating Bank Read Accesses:

Figure 4.6.F6: Alternating Bank Read Accesses

#### Read – Full page Burst:

### BIT (Hons) Computer Engineering Faculty of Information and Communication Technology, UTAR

NOTE:

For this example, the burst length = 1, and the WRITE burst is followed by a "manual" PRECHARGE. WR is required between <Din m> and the PRECHARGE command, regardless of frequency. 1.

tWR is required between spining

A8, A9, and A11 = "Don't Care."

Write - Without Auto Precharge:

NOTE:

- 1. For this example, the burst length = 4, and the WRITE burst is followed by a "manual" PRECHARGE.

- 2.

- Faster frequencies require two clocks (when <sup>1</sup>WR > <sup>1</sup>CK). A8, A9, and A11 = "Don't Care." <sup>1</sup>WR of 1 CLK available if running 100 MHz or slower. Check factory for availability. 4.

#### Alternating Bank Write Accesses:

NOTE:

1. For this example, the burst length = 4.

Faster frequencies require two clocks (when <sup>t</sup>WR > <sup>t</sup>CK). A8, A9, and A11 = "Don't Care." 2. 3.

## BIT (Hons) Computer Engineering Faculty of Information and Communication Technology, UTAR

#### Write - Full Page Burst:

3.

2. A8, A9, and A11 = "Don't Care."

#### BIT (Hons) Computer Engineering Faculty of Information and Communication Technology, UTAR

#### Consecutive Read Burst:

Figure 4.6.F15: Consecutive Read Burst

## Terminating a Read Burst:

Figure 4.6.F16: Terminating a Read Burst

## 4.7: Timeline

|                                                                  |          | Start   | End     | we | ek |   |   |   |   |   |   |   |    |    |    |    |    |

|------------------------------------------------------------------|----------|---------|---------|----|----|---|---|---|---|---|---|---|----|----|----|----|----|

| Task Name                                                        | Duration | Date    | Date    |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

|                                                                  | (weeks)  |         |         | 1  | 2  | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| Study the existing work that being developed                     | 2        | 2/6/14  | 14/6/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Develop test for the existing RISC<br>32 pipeline processor      | 4        | 9/6/14  | 3/7/14  |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Review the previous work of<br>SDRAM controller                  | 3        | 16/6/14 | 6/7/14  |    |    | — |   |   |   |   |   |   |    |    |    |    |    |

| Perform a deeper Literature<br>Reviews                           | 2        | 30/6/14 | 9/7/14  |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Research and Fact Findings                                       |          |         |         |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| *analyze the interface of SDRAM<br>and Cache                     | 3        | 9/7/14  | 25/7/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Develop a Methodology and<br>provide solutions                   |          |         |         |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| *Protocol Controller Block design                                | 2        | 26/7/14 | 3/7/14  |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| *improve SDRAM controller to<br>support multiple cache           | 3        | 27/7/14 | 5/8/14  |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Verify the integration of the                                    |          |         |         |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| controller of cache and SDRAM by<br>*Develop an appropriate test | 3        | 28/7/14 | 18/8/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Meet with Supervisor weekly                                      | 14       | 26/5/14 | 25/8/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Submission of proposal report                                    |          |         | 11/8/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| Project I presentation                                           |          |         | 25/8/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

| End of Project I                                                 |          |         | 29/8/14 |    |    |   |   |   |   |   |   |   |    |    |    |    |    |

According to schedule

Completed beyond time

Completed

Planning

Table 4.7.1 Gantt chart for Project I

| Task Name                                      | Duration | wee | k |   |   |   |   |   |   |   |    |    |    |    |    |

|------------------------------------------------|----------|-----|---|---|---|---|---|---|---|---|----|----|----|----|----|

|                                                | (weeks)  | 1   | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| Specification and development                  |          |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| i) Develop Architecture<br>Specification       | 1        |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| ii) Develop Microarchitecture<br>Specification | 2        |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| iii) Develop Verification<br>Specification     | 2        |     |   | _ |   |   |   |   |   |   |    |    |    |    |    |

| Develop Test case and<br>Verification          | 2        |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Documentation Report Writing                   | 1        |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Meet with Supervisor weekly                    | 14       |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Submission of proposal report                  |          |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| Project II presentation                        |          |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

| End of Project II                              |          |     |   |   |   |   |   |   |   |   |    |    |    |    |    |

Table 4.7.2 Planning Gantt chart for Project II

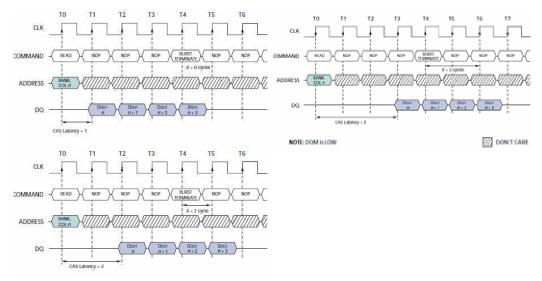

# Chapter 5: Micro-architecture of Memory System

## 5.1: Memory System Micro-Architecture and its Partitioning

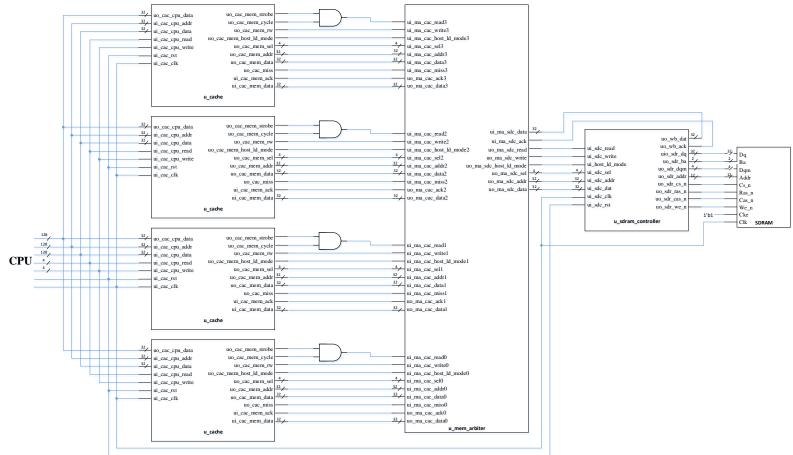

Figure 5.0: Memory System Micro-Architecture and its Partitioning

## **5.2: Design Hierarchy**

Cache is involved for the project purpose, to verify the compatibility of memory system and SDRAM controller. However, the Translation Lookaside Buffer (TLB) is not included in this design since memory initialization can be done by the testbench.

| Chip Partitioning at<br>Architecture level | Unit Partitioning at Micro-<br>Architecture Level | Block and Functional Block<br>Partitioning at RTL level<br>(Micro-Architecture level) |

|--------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------|

| Memory System unit                         | u_cache (for instruction)                         | b_cache_ctrl                                                                          |

|                                            | u_cache (for data)                                | b_cache_ctrl                                                                          |

|                                            | u_mem_arbiter                                     | -                                                                                     |

|                                            | u_sdram_controller                                | b_sdc_fsm                                                                             |

|                                            |                                                   | b_sdc_sdram_if                                                                        |

|                                            |                                                   | b_sdc_addr_mux                                                                        |

|                                            |                                                   | b_sdc_obrt_top                                                                        |

|                                            | sdram (mt48lc4m32b2)                              | -                                                                                     |

Table 5.1: Formation of a design hierarchy for 32-bit Memory System

### **Chapter 6: Microarchitecture Specification**

Unit Partitioning of Memory System

Figure 6: Unit Partitioning of Memory System

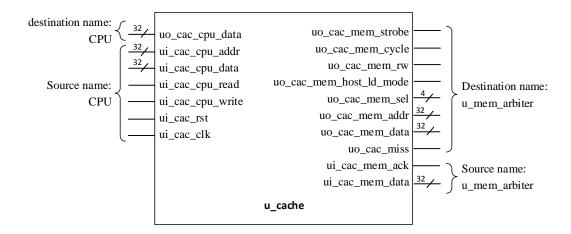

## 6.1: Cache Unit

This is a 2-way set associative cache. Functionalities of Cache Unit:

- 1. Store a small fraction of data (for D-Cache) or instructions (for I-Cache) of main memory.

- 2. Output desired data or instruction to CPU when it issues a READ.

- 3. Write data into desired location as instructed by CPU (D-Cache only).

- 4. Send signal to stall the CPU when read miss or write miss.

- 5. Communicate with SDRAM Controller to write back 'dirty' block of data back into SDRAM and fetch new block of data from it.

Figure 6.1: Cache Unit Block Diagram

This design includes Wishbone bus output signals, which are strobe and cycle, indicate that a valid bus cycle in progress and chip selected. However, the SDRAM controller does not use any Wishbone interfaces. The design is unnecessary for the cache and should be removed in future development. And yet it uses to test for the compatibility of new SDRAM controller only.

#### 6.1.1: I/O Description

| Pin name: ui_cac_clk                      |

|-------------------------------------------|

| Pin class: Global                         |

| <b>Path:</b> External $\rightarrow$ Cache |

| Description: System clock signal.         |

| Pin name: ui_cac_rst                      |

| Pin class: Global                         |

| <b>Path:</b> External $\rightarrow$ Cache |

| <b>Description:</b> System reset signal.  |

| Pin name: ui_cac_cpu_data                                                                      |

|------------------------------------------------------------------------------------------------|

| Pin class: Data                                                                                |

| Path: CPU→ Cache                                                                               |

| <b>Description:</b> 32-bits data from CPU that to be written into the cache.                   |

| Pin name: ui_cac_cpu_addr                                                                      |

| Pin class: Address                                                                             |

| Path: CPU→ Cache                                                                               |

| <b>Description:</b> 32-bits address from CPU that indicates a certain location that to be      |

| accessed.                                                                                      |

| Pin name: ui_cac_cpu_read                                                                      |

| Pin class: Control                                                                             |

| Path: CPU→ Cache                                                                               |

| <b>Description:</b> A control signal that enables the read from cache from given address       |

| when it is asserted (HIGH).                                                                    |

| Pin name: ui_cac_cpu_write                                                                     |

| Pin class: Control                                                                             |

| Path: CPU→ Cache                                                                               |

| <b>Description:</b> A control signal that enables the write of data into a certain location in |

| cache when it is asserted (HIGH).                                                              |

| Pin name: uo_cac_cpu_data                                                                      |

| Pin class: Data                                                                                |

| Path: Cache → CPU                                                                              |

| <b>Description:</b> 32-bits data that to be output to CPU.                                     |

| Pin name: uo_cac_mem_strobe                                                                    |

| Pin class: Control                                                                             |

| Path: Cache→ Memory Arbiter                                                                    |

| <b>Description:</b> Strobe signal that goes into SDRAM Controller.                             |

| Pin name: uo_cac_mem_cycle                                                                     |

| Pin class: Control                                                                             |

| Path: Cache→ Memory Arbiter                                                                    |

| Description: Cycle signal that goes into SDRAM Controller.                                     |

| Pin name: uo_cac_mem_rw                                                                        |

| Pin class: Control                                                                             |

| Path: Cache→ Memory Arbiter                                                                    |

| <b>Description:</b> A read or write signal that goes into SDRAM Controller.                    |

| When '1', write.                                                                               |

| When '0', read.                                                                                |

| Pin name: uo_cac_mem_host_ld_mode                                                              |

| Pin class: Control                                                                             |

| Path: Cache→ Memory Arbiter                                                                    |

| <b>Description:</b> Assert (HIGH) this signal to configure the operating mode of SDRAM         |

| Pin name: uo_cac_mem_sel                                                                       |

| Pin class: Control                                                                             |

| Path: Cache→ Memory Arbiter                                                                    |

| <b>Description:</b> 4-bits control signals to mask which byte of the 4 bytes (32-bits) data    |

| goes in or comes out from SDRAM.                                                               |

|                                                                                                |

| When it is '1', the corresponding byte will enable.                                     |

|-----------------------------------------------------------------------------------------|

| When it is '0', the corresponding byte will be masked and the output becomes 'z'.       |

| Pin name: uo_cac_mem_addr                                                               |

| Pin class: Address                                                                      |

| Path: Cache→ Memory Arbiter                                                             |

| <b>Description:</b> 32-bits address that indicates which location in the SDRAM to be    |

| accessed.                                                                               |

| Pin name: uo_cac_mem_data                                                               |

| Pin class: Data                                                                         |

| Path: Cache→ Memory Arbiter                                                             |

| <b>Description:</b> 32-bits data that to be written in to the SDRAM.                    |

| When in host load mode, it contains the valid mode value for configuration.             |

| Pin name: uo_cac_miss                                                                   |

| Pin class: Control                                                                      |

| Path: Cache→ Memory Arbiter                                                             |

| <b>Description:</b> A status signal indicates cache miss. It is to stall the pipelines. |

| Pin name: ui_cac_mem_ack                                                                |

| Pin class: Control                                                                      |

| <b>Path:</b> Memory Arbiter $\rightarrow$ Cache                                         |

| <b>Description:</b> Acknowledge signal (active HIGH) to indicate read or write to SDRAM |

| is done.                                                                                |

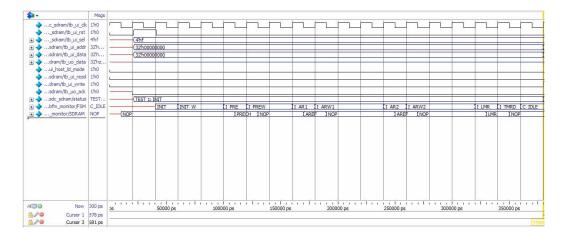

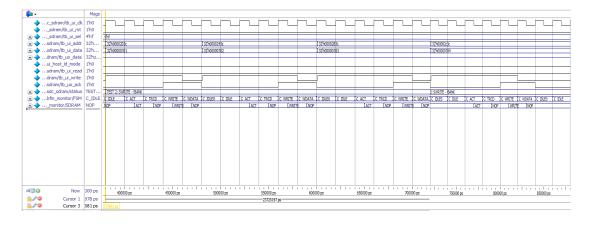

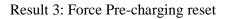

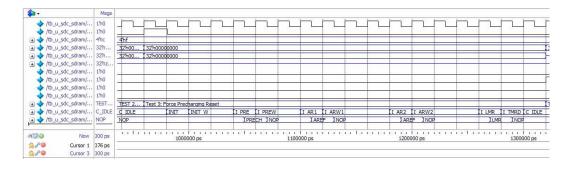

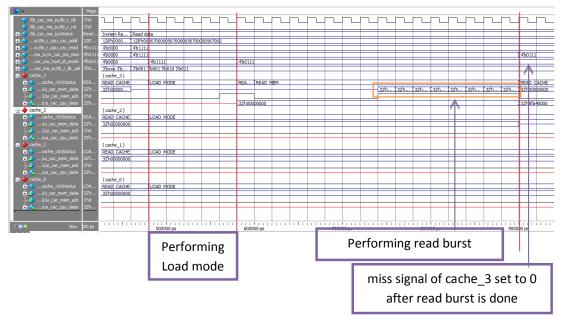

| Pin name: ui_cac_mem_data                                                               |