# DESIGN AND DEVELOPMENT OF MEMORY SYSTEM FOR 32-BIT 5 STAGE PIPELINE RISC: MEMORY SYSTEM INTEGRATION

BY GOH DIH JIANN

A REPORT

# SUBMITTED TO

UniversitiTunku Abdul Rahman

in partial fulfilment of the requirements

for the degree of

BACHELOR OF COMPUTER SCIENCE (HONS)

COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus)

OCTOBER 2015

# UNIVERSITI TUNKU ABDUL RAHMAN

| REPO                                                                   | ORT STATU                                                                         | S DECLARATION FORM                                                                                                          |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Title:                                                                 |                                                                                   |                                                                                                                             |

|                                                                        |                                                                                   | ic Session :                                                                                                                |

| I                                                                      |                                                                                   | APITAL LETTER)                                                                                                              |

| Universiti Tuni<br>1. The dissert                                      | tation is a property of the                                                       | ry subject to the regulations as follows:<br>e Library.                                                                     |

| Universiti Tuni<br>1. The dissert                                      | ku Abdul Rahman Librar<br>tation is a property of the                             | ry subject to the regulations as follows:                                                                                   |

| Universiti Tunl<br>1. The dissert<br>2. The Librar                     | ku Abdul Rahman Libra<br>tation is a property of the<br>ry is allowed to make cop | ry subject to the regulations as follows:<br>e Library.<br>pies of this dissertation for academic purposes.<br>Verified by, |

| Universiti Tuni<br>1. The dissert                                      | ku Abdul Rahman Libra<br>tation is a property of the<br>ry is allowed to make cop | ry subject to the regulations as follows:<br>e Library.<br>pies of this dissertation for academic purposes.                 |

| Universiti Tuni<br>1. The dissert<br>2. The Librar<br>(Author's signal | ku Abdul Rahman Libra<br>tation is a property of the<br>ry is allowed to make cop | ry subject to the regulations as follows:<br>e Library.<br>pies of this dissertation for academic purposes.<br>Verified by, |

# DESIGN AND DEVELOPMENT OF MEMORY SYSTEM FOR 32-BIT 5 STAGE PIPELINE RISC: MEMORY SYSTEM INTEGRATION

BY GOH DIH JIANN

# A REPORT

# SUBMITTED TO

UniversitiTunku Abdul Rahman

in partial fulfilment of the requirements

for the degree of

BACHELOR OF COMPUTER SCIENCE (HONS)

#### COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus)

OCTOBER 2015

# **DECLARATION OF ORIGINALITY**

I declare that this report entitled "DESIGN AND DEVELOPMENT OF MEMORY SYSTEM FOR 32-BIT 5 STAGE PIPELINE RISC: MEMORY SYSTEM INTEGRATION" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other award.

Signature : \_\_\_\_\_

Name

: \_\_\_\_\_\_\_\_GOH DIH JIANN\_\_\_\_\_\_

Date : <u>14/12/2015</u>

# ACKNOWLEDGEMENTS

I would like to take this opportunity to express my gratitude to my final year project supervisor, Mr. Mok Kai Ming, who encourage me when I lost confidence, comfort me when I am stressed, and enlighten me when I lost my way. A million appreciation and thank for his guidance and wisdom during the entire course of this project. Lastly, I would like to say thanks to my parents for their unconditional support during my hard time throughout the course.

#### ABSTRACTS

This project is to enhance the current RISC32 architecture that developed in Universiti Tunku Abdul Rahman under Faculty of Information and Communication Technology by redesigning the memory system. After reviewing the previous work, the RISC32 processor memory system cache unit using write-through scheme which is able to improve more of it efficiency.

Hence, this project is initiated to redesign the cache unit into write-back cache and adding a write buffer(FIFO) in the cache unit to handling the data transferring back to SDRAM when read miss and write miss occur. Some modification on memory arbiter was done in order for the new cache unit worked in the memory system. This project is modelled using Verilog HDL and a test program will be developed in order to test the functionality and compatibility of the newly design write-back cache with the rest of memory system (memory arbiter, SDRAM controller, SDRAM).

# **TABLE OF CONTENTS**

| Contents                                                                        |    |

|---------------------------------------------------------------------------------|----|

| Chapter 1 Introduction                                                          | 11 |

| 1.1 Background Information                                                      | 12 |

| 1.2 Motivation and Problem Background                                           | 13 |

| 1.3 Problem Statement                                                           | 14 |

| Chapter 2 Literature Review                                                     | 15 |

| 2.1 Write-through Scheme vs Write-back Scheme                                   | 15 |

| 2.2 Write buffer                                                                | 15 |

| 2.2.1 Write Buffer Saturation                                                   | 15 |

| 2.2.2 Write-back Scheme with Write Buffer                                       | 16 |

| 2.3 Reduce Miss Rate via Larger Block Size: Multiword Block Direct Mapped Cache | 16 |

| 2.4 Cache Unit                                                                  | 17 |

| 2.4.1 Cache Associative                                                         | 17 |

| 2.4.2 Scenarios to Represent Cache Behaviours                                   | 18 |

| 2.4.3 Block Partitioning of Cache Unit                                          | 20 |

| 2.5 SDRAM                                                                       | 22 |

| 2.6 SDRAM Controller                                                            | 25 |

| 2.6.1 Block partitioning of SDRAM Controller                                    | 26 |

| 2.7 Memory Arbiter                                                              | 27 |

| 2.7.1 I/O Description                                                           | 28 |

| 2.7.2 Memory Arbiter State Diagram                                              | 31 |

| 2.7.3 State Definition                                                          | 31 |

| 2.7.4 Output or Behaviors Corresponding to the States                           | 32 |

| Chapter 3 Project Scope and Objectives                                          | 34 |

| 3.1 Project Objectives                                                          | 34 |

| 3.2 Impact and Significance                                                     | 35 |

| Chapter 4 Method and Technologies Involved                                      | 36 |

| 4.1 Design Methodology                                                          | 36 |

|                                                                                 |    |

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

| 4.1.1 Micro-architecture Level Design (Unit Level)                 | 37           |

|--------------------------------------------------------------------|--------------|

| 4.1.2 Micro-architecture Level Design (Block Level)                | 37           |

| 4.2 Design Tools                                                   |              |

| 4.2.1 Verilog HDL Simulator - Mentor Graphics ModelSim SE-64 10.1c |              |

| Chapter 5 Memory System Specification                              | 39           |

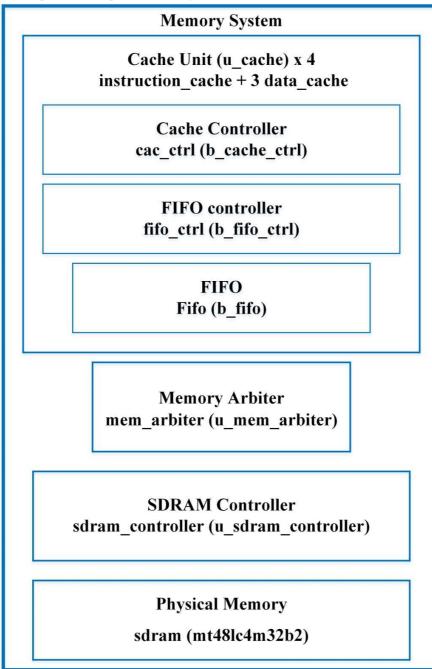

| 5.1 Partitioning and Design Hierarchy                              | 39           |

| 5.2 Memory System Specifications                                   | 40           |

| 5.3 Memory Map                                                     | 41           |

| 5.4 Architecture of Memory System                                  | 43           |

| Chapter 6 Micro-Architecture Specification                         | 44           |

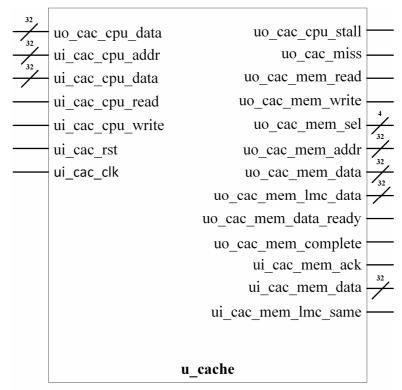

| 6.1 Cache Unit                                                     | 44           |

| 6.2 Scenarios to Represent Cache Behaviors Error! Bookmark r       | not defined. |

| 6.3 Cache Design Protocol Error! Bookmark r                        | not defined. |

| 6.4 Cache Unit I/O Description                                     | 46           |

| 6.5 Block Partitioning of Cache Unit                               | 49           |

| 6.6 Cache Controller Block                                         | 49           |

| 6.6.1 Cache Controller block I/O description                       | 50           |

| 6.6.2 Cache Controller State Diagram                               | 54           |

| 6.6.3 Cache Controller State Definition Error! Bookmark r          | not defined. |

| 6.6.4 Cache Controller Output behavior Error! Bookmark r           | not defined. |

| 6.7 FIFO Controller Block                                          | 55           |

| 6.7.1 FIFO Controller block I/O description                        | 55           |

| 6.7.2 FIFO Controller State Diagram                                | 57           |

| 6.7.3 FIFO Controller State Definition Error! Bookmark r           | not defined. |

| 6.7.4 Cache Controller Output behavior Error! Bookmark r           | not defined. |

| 6.8 FIFO Block                                                     | 58           |

| 6.8.1 FIFO Controller block I/O description                        | 59           |

| Chapter 7 Verification                                             | 62           |

| 7.1 Test Plan                                                      | 62           |

| 7.2 Testbench Verilog Code                                         | 66           |

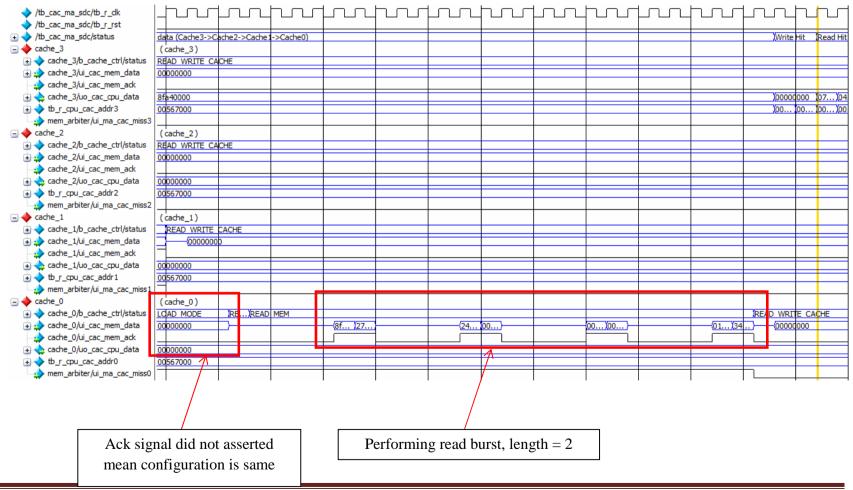

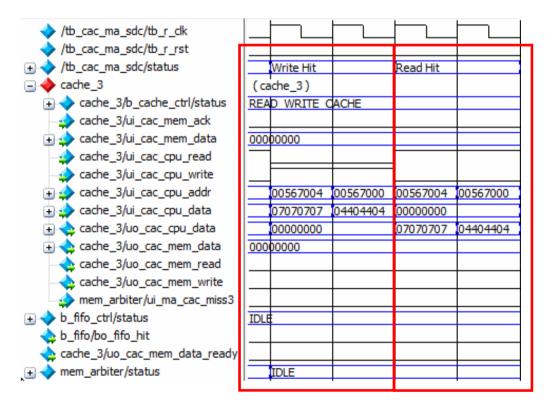

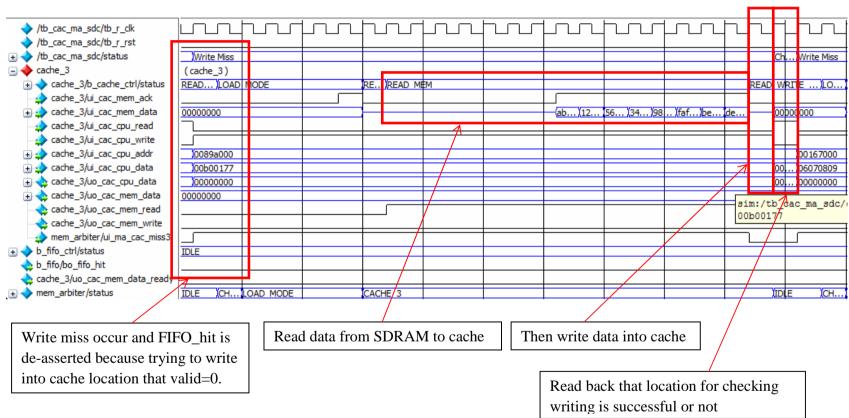

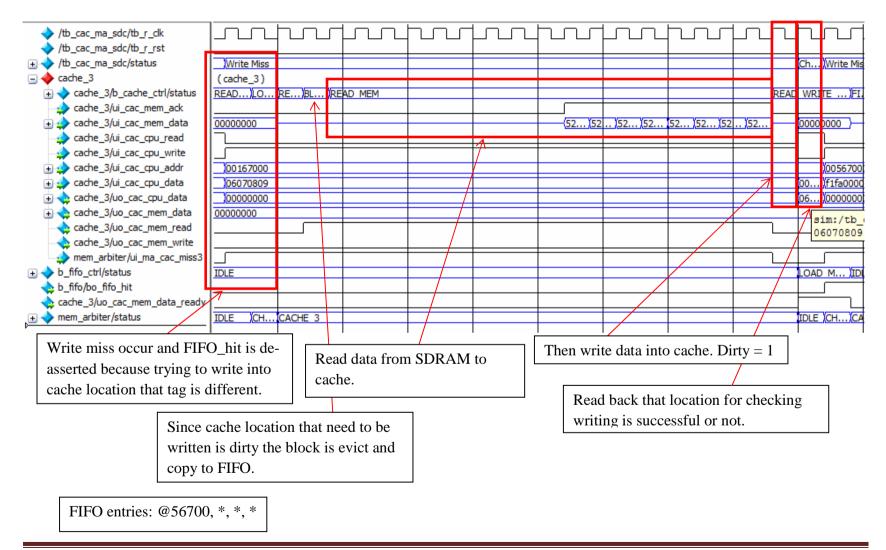

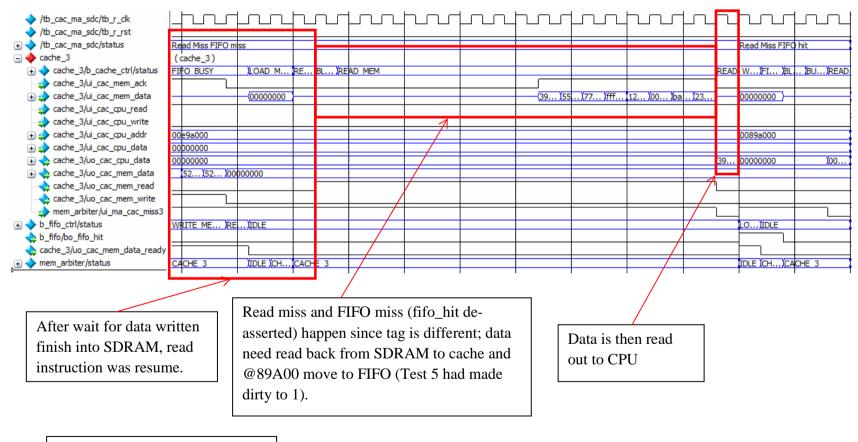

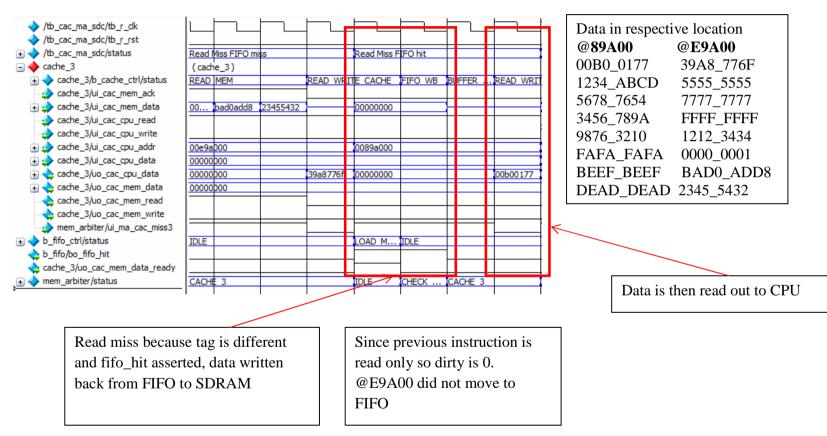

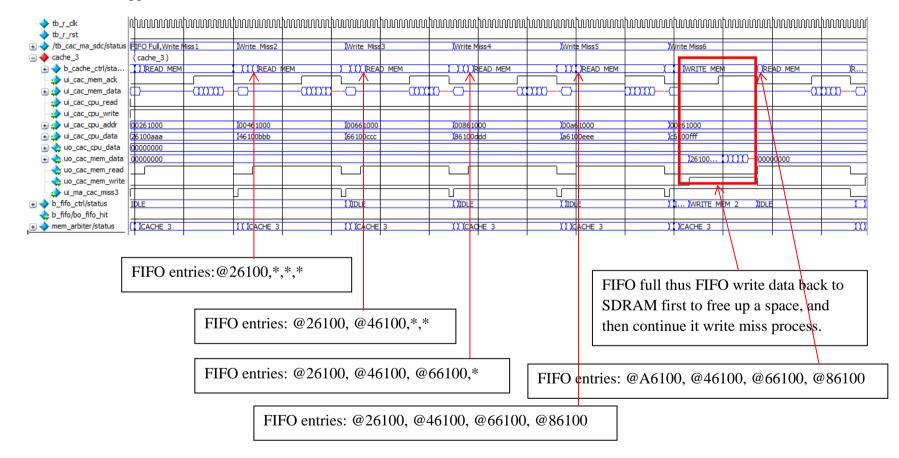

| 7.3 Simulation Result                                              | 82           |

| Chapter 8 Conclusion                                               |              |

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

| 8.1 Conclusion                      | 100 |

|-------------------------------------|-----|

| 8.2 Discussion and Future Work      |     |

| References                          | 101 |

| Appendices                          |     |

| Appendix A                          |     |

| System Specification                |     |

| A.2 Naming Convention               |     |

| A.3 Basic RISC32 processor          |     |

| A.3.1 Processor Interface           |     |

| A.3.2 I/O Pin Description           | 105 |

| A.4 System Register                 |     |

| A.4.1 General Purpose Register      |     |

| A.4.2 Special Purpose Register      |     |

| A.5 Instruction Format              | 107 |

| A.6 Addressing Mode                 |     |

| A.7 Instruction Set and Description |     |

| A.8 Memory Map                      | 112 |

| A.9 Operating Procedure             | 114 |

# LIST OF FIGURES

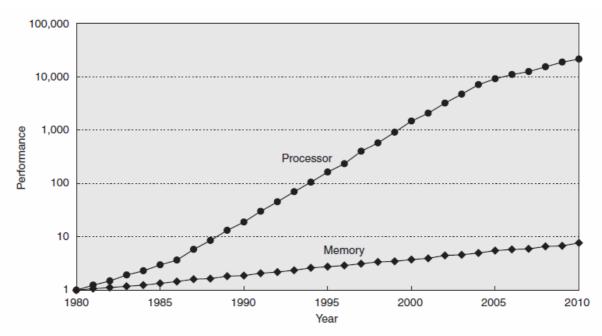

Figure 1-1-1 starting with 1980 performance as a baseline, the gap in performance between memory and processors is plotted over time.

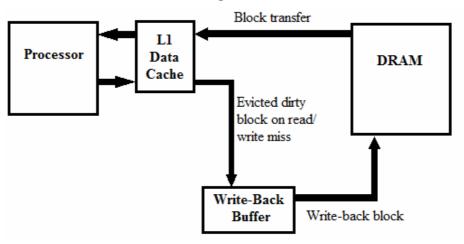

Figure 2-2-1 Write-back scheme with write buffer

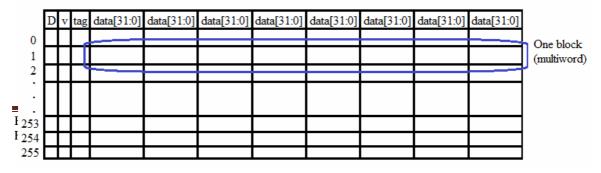

Figure 2-2-2 Multiword block direct mapped cache (block size = 32 bytes)

Figure 2-4-1 Cache Unit designed by Ching Li-lynn

Figure 2-4-2 Block Partitioning of Cache Unit designed by Ching Li-lynn

Figure 2-5-1 Block diagram of MT48LC4M32B2 (Oon Zhi Kang 2008)

Figure 2-5-2 Mode Register definitions to configure SDRAM (Micron)

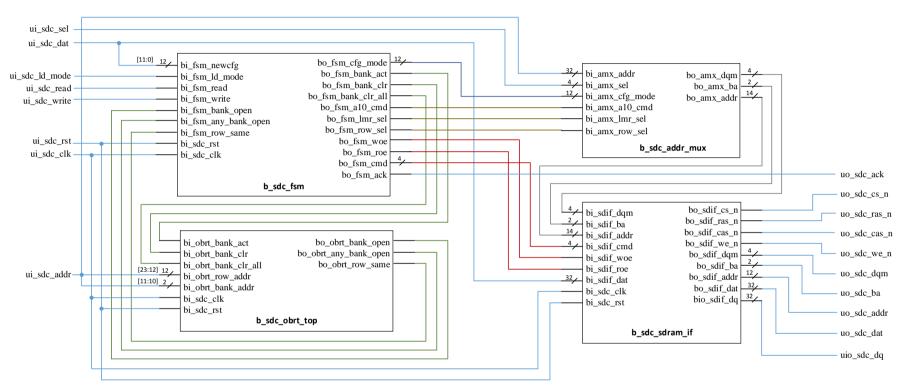

Figure 2-6-1: SDRAM Controller Block Diagram designed by Chin Chun Lek

Figure 2-6-2: The Micro-Architecture of the SDRAM Controller designed by Chin Chun Lek

Figure 2-7-1: Memory Arbiter Block Diagram

Figure 2-7-2: Memory Arbiter State Diagram

Figure 4-1-1 General Design Flow without Synthesis and Physical Design

Figure 5-1-1 Memory System Partitioning

Figure 5-4-1 Architecture of Memory System

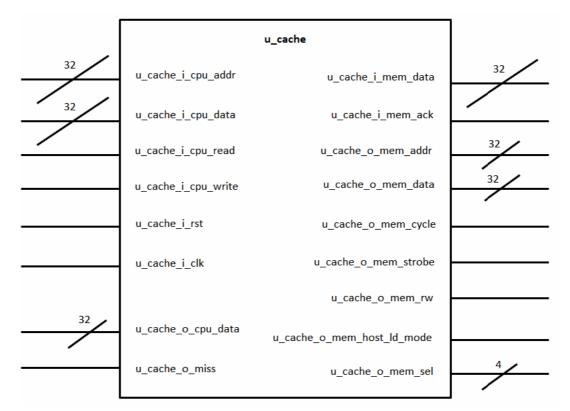

Figure 6-1-1 Block diagram of cache unit

Figure 6-3-1 Read Protocol of Cache

Figure 6-3-2 Write Protocol of Cache

Figure 6-5-1 Block Partition of Cache Unit

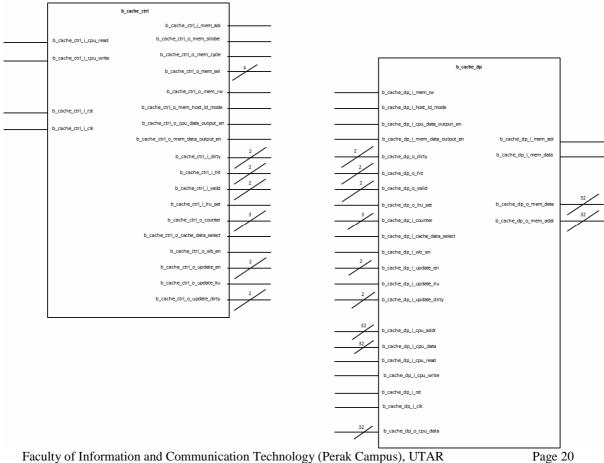

Figure 6-6-1 Block diagram of Cache Controller Block

Figure 6-6-2 State Diagram of Cache Controller

Figure 6-7-1 Block diagram of FIFO Controller Block

Figure 6-7-2 State Diagram of Cache Controller

Figure 6-8-1 Block diagram of FIFO Block

#### LIST OF TABLES

Table 2-5-1 List of SDRAM commands and function. (Micron datasheet)

Table 2-7-1: Memory Arbiter I/O Descriptions

Table 2-7-4: Memory Arbiter Output or Behaviours Corresponding to the States

Table 5-1-1 Design hierarchy for 32-bit Memory System

Table 5-2-1 Specifications of the Memory System

Table 5-3-1 Virtual memory map of 32-bits MIPS

Table 6-4-1: Cache Unit I/O Descriptions

Table 6-6-1: Cache Controller Block I/O Descriptions

Table 6-6-2: Cache Controller State Definition

Table 6-6-3: Cache Controller Output or Behaviors Corresponding to the State

Table 6-7-1: Cache Controller Block I/O Descriptions

Table 6-7-2: Cache Controller State Definition

Table 6-7-3: Cache Controller Output or Behaviors Corresponding to the State

Table 6-8-1: FIFO Block I/O Descriptions

Table 7-1-1: Memory system Full Chip Test Plan

# LIST OF ABBREVIATIONS

- MIPS Microprocessor without Interlocked Pipeline Stages

- RISC Reduced Instruction Set Computing

- CPU Central Processing Unit

- RTL Register Transfer Level

- I/O Input output

- FIFO First In First Out

- SOC System On Chip

#### **Chapter 1 Introduction**

#### **1.1 Background Information**

The growing disparity between microprocessor and memory cause by the division of the semiconductor industry into CPU fields and memory fields which their technology have focus on different achievement, the first one has concentrated on increased in speed, while the latter one has concentrated on increased in capacity. Thus the improvement rate in microprocessor speed by far exceeds the one in memory. The continuous growing gap between CPU and memory speeds is a crucial flaw in the overall computer performance. Throughout the history, CPU speeds have been improving at an average of 55% per year, while memory latency has only been improving at 7% per year (Hennessy and Patterson 2007, p. 289).

Figure 1-1-1 starting with 1980 performance as a baseline, the gap in performance between memory and processors is plotted over time.

The performance gap grows exponentially. This make increasing processormemory performance gap is now the leading direction to improved computer system performance.

Faculty of Information and Communication Technology (Perak Campus), UTAR

Memory Hierarchy was introduced in the late of sixties to provide decreased average latency and reduced bandwidth requirements to speed up memory system. The performance of a memory-hierarchy analyse through the average memory access time, using the following expression:

average memory access time = hit time + miss rate \* miss penalty.

(Araújo 2002, p.146)

Thus the effort to decrease the performance gap between processor and physical memory has been concentrated on efficient implementations of a memory hierarchy to reduce miss rate, miss penalty and hit time.

#### **1.2 Motivation and Problem Background**

A 32-bit RISC processor has been developed in Faculty of Information and Communication Technology, University Tunku Abdul Rahman (UTAR). The project is based on Reduced Instruction Set Computing (RISC) architecture. There are several purposes to initiate this project.

- Microchip design companies develop microprocessor cores as IP (Intellectual Property) for commercial purposes only. This simply means that the microprocessor IP which includes information of the entire design process for front-end and back-end IC design are trade secrets of the company and certainly not available in market at affordable price. Hence, RISC32 project is started at University Tunku Abdul Rahman few years ago and still working to complete the design.

- There are several freely available microprocessor cores from open source such as OpenCores (<u>opencores.org</u>) which is the largest site for development of hardware IP cores as open source. However these processors are not complete and did not implement the entire MIPS Instruction Architecture (ISA). Furthermore, they are lack of comprehensive documentation which makes them not suitable for reuse and further customization.

Faculty of Information and Communication Technology (Perak Campus), UTAR

- Verification is important for proving the functionality of any digital design. The microprocessors mentioned above are handicapped by incomplete and poorly developed verification specifications. This hampers the verification process, slowing down the overall design process.

- The lack of well-developed verification specifications for these microprocessor cores will certainly affect the physical design phase. A design need to be functionally proven before the physical design phase can proceed smoothly. Otherwise, if front-end design requires changing, the entire physical design needs to be redone.

#### **1.3 Problem Statement**

This project is aim to provide a solution to the above problems by creating a 32-bit RISC core-based development environment to assist research work in the area of softcore and also application specific hardware modelling. Currently, a SDRAM Controller and SDRAM provided by MICRON Technology Inc. has been modelled at the Register Transfer Level (RTL) using Verilog HDL and both of them have been combined together and had gone through a series of simulation test. There is also a cache and a TLB modelled at RTL using Verilog HDL, both of them were integrated together with the SDRAM controller as a complete memory system.

Seniors of UTAR FICT computer engineering implemented cache unit, memory arbiter and SDRAM controller. In previous implementation, cache unit is a writethrough 2-way set associative caches which it can be improved. Thus this project aim to redesign the cache unit into a write-back multiword direct mapped cache with write buffer (FIFO). The cache unit's protocol need to redesign because of the inclement of write-back ability in cache unit. After implemented the new cache unit, a little modification needs to be done in memory arbiter unit in order to compatible with the new cache unit. After that the functionality need to verify so that every unit is working as expected.

#### **Chapter 2 Literature Review**

#### 2.1 Write-through Scheme vs Write-back Scheme

Write-through cache: Data are written into the cache and sent to the main memory (in this project is SDRAM) as operation is executed. This ensures that the contents of the cache and main memory are always the same, but it has downside that it experiences latency based on writing to SDRAM. This cache is good for application that writes and then re-read data frequently.

Write-back cache: Write-back cache keep stored data in the cache, and when a block that has been written is evicted from the cache, the contents of the block are then written back (copied) into the main memory (SDRAM). Write-back cache keep stored data in the cache, the main memory become the same after the contents of the block are written back (copied) into main memory. The disadvantage is there is data availability exposure risk because the only copy of the written data is in cache. Write-back cache is the best performing solution for mixed workloads as both read and write have similar response time levels. (Carter 2002)

This mean that if use write-through cache system performance is limited by memory speed whereas if use write-back cache the cache will get the full performance.

#### 2.2 Write buffer

Data is not written to the main memory directly but into the write buffer first. Once the data is written into the write buffer and assuming cache hit, the CPU is done with the write, then the SDRAM controller will move the write buffer's contents to the real memory behind the scene. This work as long as the frequency of store is not too high.

#### 2.2.1 Write Buffer Saturation

When store frequency approaching main memory write frequency it leads to write buffer saturation. In this case no matter how big the write buffer it is it will still overflow because data simply come in faster than it can empty it, thus CPU will running at main memory cycle time, which is very slow. The solution for write buffer saturation is to get rid of this write buffer and replace this write through cache with a write back cache. (Mok KM 2009)

#### 2.2.2 Write-back Scheme with Write Buffer

Write buffer allow cache to proceed as soon as data is placed in buffer rather than wait the full latency to write the data into memory. Write-back scheme write data to cache only. It makes main memory is not updated and allow cache and memory to be inconsistent. Since data in cache and memory is inconsistent, each block of data requires a dirty bit to indicate a block is modified. If block replacement happen in cache, only evicted dirty block is kept in a write buffer so that it can write-back to memory later. The drawback of this is it has complex hardware.

Figure 2-2-1 Write-back scheme with write buffer

# 2.3 Reduce Miss Rate via Larger Block Size: Multiword Block Direct Mapped Cache

Using multiword block direct mapped cache is the simplest way to reduce miss rate. This take advantage of spatial locality which mean if a word is accessed, nearby words are likely to be accessed soon, thus it is better to move more words per block from memory to cache. However when miss happen it takes more cycle to handle the miss (miss penalty increase).

# Figure 2-2-2 Multiword block direct mapped cache (block size = 32 bytes)

#### 2.4 Cache Unit

A 2-way set associative write-through cache of 2MB has been modelled by Ching Lilynn. This cache can be used as both Instruction Cache and Data Cache. Inside of cache unit consists of cache controller block and cache datapath block.

Figure 2-4-1 Cache Unit designed by Ching Li-lynn

#### 2.4.1 Cache Associative

- The current cache is a 2-way set associative cache

- N-Way set associative uses N cache, data RAMs and N cache-tag RAMs (built out of N RAMs and N comparators, a cache controller, and isolation buffers. It is actually separate the memory into different set of caches and ease the replacement and searching policy.

• 1-way set associative cache = direct mapped cache

# 2.4.2 Scenarios to Represent Cache Behaviours

Basically there are just 4 scenarios might be happened on cache, we need to decide what to do when these scenarios happen.

- 1. Read Miss

- Receive physical address and instructions of read from the main controller of the CPU.

- Check validity and tag for the index of the physical address points to. A miss signal is produced due to either it is invalid or the tag is different.

- Cache controller asserts strobe, cycle, and read signals to SDRAM controller to fetch new black of data.

- Meanwhile, the pipelines of the CPU are stalled.

- Check LRU to determine which slot is least recently used, store the newly fetched block of data in it.

- Set valid bit for the index pointed.

- Update LRU.

- Deassert the miss, strobe, cycle and read signal, the pipelines are un-stalled.

2. Read Hit

- Receive physical address and instruction of read from the main controller of CPU.

- Check validity and tag for index of the physical address points to. Miss signal is active low.

- Load the selected instruction or data by determining the byte offset to host.

- Update LRU.

- 3. Write Miss (For D-Cache only)

- Receive physical address, data, and instruction of write from the main controller of CPU.

- Check validity and tag for the index of the physical address points to. A miss signal is produced due to either it is invalid or the tag is different.

- Stall the pipelines.

- Check LRU to determine which is least recently used.

- Cache controller asserts strobe, cycle, and read to SDRAM controller to access the data in SDRAM.

- If the block of data was dirty, send the block of 8 words back to SDRAM.

- Fetch new block of data from SDRAM.

- After the new block is updated from SDRAM, strobe, cycle, read and miss signals are deasserted.

- Perform the write.

- Update LRU.

- 4. Write Hit (For D-Cache only)

- Receive physical address, data, and instruction of write from main controller of CPU.

- Check validity of tag for index of the physical address points to. Miss signal is active low.

- Update the selected instruction or data.

- Update LRU.

# 2.4.3 Block Partitioning of Cache Unit

Faculty of Information and Communication Technology (Perak Campus), UTAR

Figure 2-4-2 Block Partitioning of Cache Unit designed by Ching Li-lynn

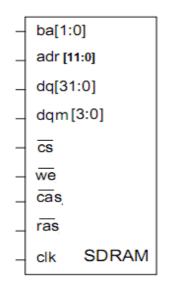

#### 2.5 SDRAM

Synchronous Dynamic Random Access Memory (SDRAM) is a type of DRAM that is synchronised with the system bus. This project uses a SDRAM that is provided by MICRON Technology Inc. It is MT48LC4M32B2, with 16MB of storage. (Micron datasheet, n.d.) SDRAM control by SDRAM controller modelled by Chin Chun Lek thus in this project just need to focus on function of SDRAM and it configuration – load mode definition.

#### Figure 2-5-1 Block diagram of MT48LC4M32B2 (Oon Zhi Kang 2008)

The cs (active low) pin is used to select the SDRAM, while we, cas and ras are used to request operations from the SDRAM.

| Name (Function)                                        | CS# | RAS# | CAS# | WE# | DQM | ADDR     | DQ     | Notes |

|--------------------------------------------------------|-----|------|------|-----|-----|----------|--------|-------|

| COMMAND INHIBIT (NOP)                                  | н   | X    | Х    | Х   | Х   | Х        | Х      |       |

| NO OPERATION (NOP)                                     | L   | н    | н    | н   | X   | х        | х      |       |

| ACTIVE (select bank and activate row)                  | L   | L    | н    | н   | Х   | Bank/row | Х      | 2     |

| READ (select bank and column, and start READ burst)    | L   | н    | L    | н   | L/H | Bank/col | Х      | 3     |

| WRITE (select bank and column, and start WRITE burst)  | L   | н    | L    | L   | L/H | Bank/col | Valid  | 3     |

| BURST TERMINATE                                        | L   | н    | н    | L   | Х   | Х        | Active | 4     |

| PRECHARGE (Deactivate row in bank or banks)            | L   | L    | н    | L   | Х   | Code     | Х      | 5     |

| AUTO REFRESH or SELF REFRESH (enter self refresh mode) | L   | L    | L    | н   | Х   | Х        | Х      | 6, 7  |

| LOAD MODE REGISTER                                     | L   | L    | L    | L   | X   | Op-code  | х      | 8     |

| Write enable/output enable                             | X   | X    | Х    | Х   | L   | Х        | Active | 9     |

| Write inhibit/output High-Z                            | X   | X    | Х    | Х   | н   | Х        | High-Z | 9     |

Table 2-5-1 List of SDRAM commands and function. (Micron datasheet)

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

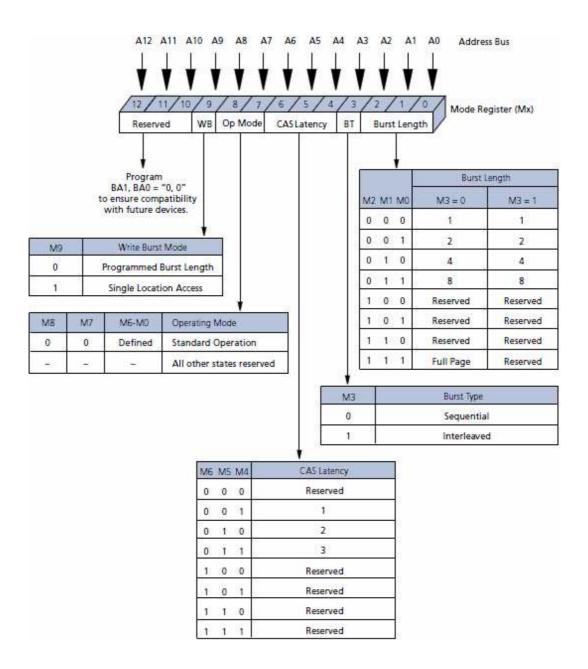

#### Figure 2-5-2 Mode Register definitions to configure SDRAM (Micron)

# • Burst Length

Determine the maximum number of column locations that can be accessed for a given READ or WRITE operation.

• Burst Type

Select either sequential or interleaved burst to be adopted by SDRAM. The ordering of accesses within a burst is determined by burst length, burst type, starting column address.

• CAS Latency

Delay in clock cycles between registration of a READ command and the availability of the first piece of output data. It can only be set to 2 or 3 clock cycles.

• Operating Mode

Select which operating mode should the SDRAM be. Currently there is only normal operating mode is available for use.

• Writing Burst Mode

When it is '0', the burst length is programmed via M0-M2 applies to both READ and WRITE burst.

When it is '1', the programmed burst length applies to READ bursts, but write accesses are single-location (non-burst) accesses.

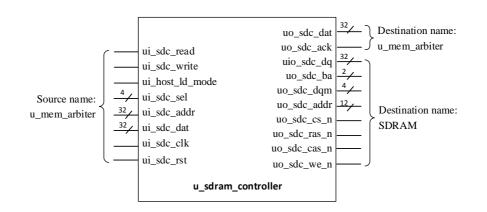

#### **2.6 SDRAM Controller**

A SDRAM controller had been modelled by Chin Chun Lek. The SDRAM controller acts as an intermediary between the SDRAM and the CPU. It handles SDRAM operations using some protocols. It has no longer been modeled based on Industry standard HOST SoC interface due to the current design needs.

The main features of SDRAM Controller are:

- 1) Burst transfers and burst termination

- 2) SDRAM initialization support

- 3) Performance optimization by leaving active rows open

- 4) Load mode control

Figure 2-6-1: SDRAM Controller Block Diagram designed by Chin Chun Lek

# 2.6.1 Block partitioning of SDRAM Controller

Figure 2-6-2: The Micro-Architecture of the SDRAM Controller designed by Chin Chun Lek

#### **2.7 Memory Arbiter**

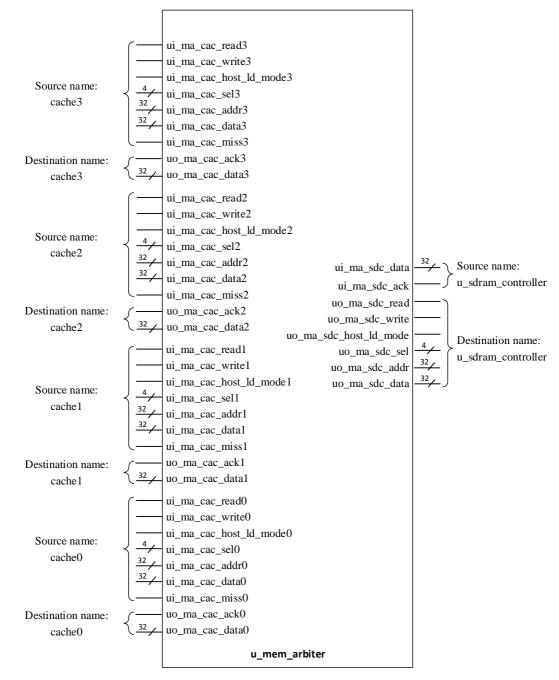

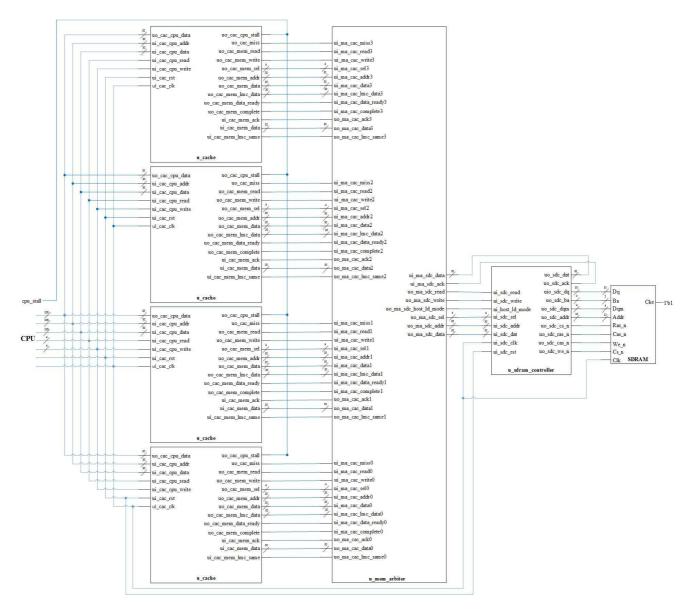

Chin Chun Lek had modelled a new memory arbiter. This memory arbiter allows multiple caches to access single SDRAM by given priority. The block diagram below shows a memory arbiter that can support up to 4 caches. Some modification needs to be done after that in order to compatible with this project newly designed cache unit.

Figure 2-7-1: Memory Arbiter Block Diagram

#### 2.7.1 I/O Description

Pin name: ui\_ma\_cac\_read

Pin class: Control

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

**Description:** read signals from the TLBs and Caches.

Pin name: ui\_ma\_cac\_write

Pin class: Control

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

**Description:** write signal from the TLBs and Caches.

**Pin name:** ui\_ma\_cac\_host\_ld\_mode

Pin class: Control

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

**Description:** Host Load Mode signals from the TLBs and Caches.

Pin name: ui\_ma\_cac\_sel

Pin class: Control

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

**Description:** Byte Select signals from the TLBs and Caches.

Pin name: ui\_ma\_cac\_addr

Pin class: Address

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

**Description:** Addresses from the TLBs and Caches.

**Pin name:** ui\_ma\_cac\_data

Pin class: Data

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

**Description:** Data from the TLBs and Caches.

**Pin name:** ui\_ma\_cac\_miss

Pin class: Control

**Path:** TLB or Cache  $\rightarrow$  Memory Arbiter

Description: Miss signals from the TLBs and Caches.

Pin name: uo\_ma\_cac\_ack

Pin class: Control

BIT (Hons) Computer Engineering

Faculty of Information and Communication Technology (Perak Campus), UTAR

**Path:** Memory Arbiter  $\rightarrow$  TLB or Cache

**Description:** Acknowledge signal (active HIGH) to indicate read or write to SDRAM is done, and send to Caches or TLB.

**Pin name:** uo\_ma\_cac\_data

Pin class: Data

**Path:** Memory Arbiter  $\rightarrow$  TLB or Cache

**Description:** 32-bits data that goes to Cache or TLB.

**Pin name:** ui\_ma\_sdc\_data

Pin class: Data

**Path:** Memory Arbiter  $\rightarrow$  SDRAM Controller

**Description:** 32-bits data that comes from SDRAM.

**Pin name:** ui\_ma\_sdc\_ack

Pin class: control

**Path:** Memory Arbiter  $\rightarrow$  SDRAM Controller

**Description:** Acknowledge signal (active HIGH) to indicate read or write to SDRAM is done.

Pin name: uo\_ma\_sdc\_host\_ld\_mode

Pin class: control

**Path:** Memory Arbiter  $\rightarrow$  SDRAM Controller

**Description:** Host Load Mode signals that send to SDRAM Controller.

**Pin name:** uo\_ma\_sdc\_read

Pin class: control

**Path:** Memory Arbiter  $\rightarrow$  SDRAM Controller

Description: read signal that goes to SDRAM Controller

**Pin name:** uo\_ma\_sdc\_write

Pin class: control

**Path:** Memory Arbiter  $\rightarrow$  SDRAM Controller

**Description:** Write signal that goes to SDRAM Controller.

Pin name: uo\_ma\_sdc\_sel

Pin class: control

**Path:** Memory Arbiter  $\rightarrow$  SDRAM Controller

BIT (Hons) Computer Engineering

Faculty of Information and Communication Technology (Perak Campus), UTAR

**Description:** 4-bits control signals to mask which byte of the 4 bytes (32-bits) data goes in or comes out from SDRAM.

When it is '1', the corresponding byte will enable.

When it is '0', the corresponding byte will be masked and the output becomes 'z'.

**Pin name:** uo\_ma\_sdc\_addr

Pin class: control

**Path:** SDRAM Controller  $\rightarrow$  Memory Arbiter

**Description:** 32-bits address to indicate which location in the SDRAM to be

accessed.

**Pin name:** uo\_ma\_sdc\_data

Pin class: control

**Path:** SDRAM Controller  $\rightarrow$  Memory Arbiter

**Description:** 32-bits data that goes into the SDRAM.

When wants to configure the operating mode of the SDRAM, the configuration values

goes into SDRAM via this port too.

# Table 2-7-1: Memory Arbiter I/O Descriptions

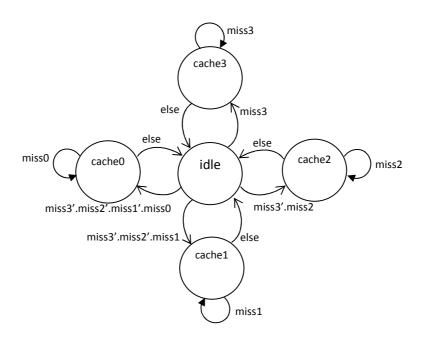

# 2.7.2 Memory Arbiter State Diagram

Figure 2-7-2: Memory Arbiter State Diagram

#### 2.7.3 State Definition

|         | State Name | Definition                                       |

|---------|------------|--------------------------------------------------|

| Memory  | cache3     | First priority cache given to perform operation  |

| Arbiter | cache2     | Second priority cache given to perform operation |

|         | cache1     | Third priority cache given to perform operation  |

|         | cache0     | Last priority cache given to perform operation   |

|         | idle       | Wait for new operation                           |

Table 2-7-2: State Definition of Memory Arbiter

| State Name | Correspondence Output Behaviors                  |

|------------|--------------------------------------------------|

| cache3     | When ui_ma_cac_miss3 = 1,                        |

|            |                                                  |

|            | from cache3 to SDRAM controller:                 |

|            | uo_ma_sdc_read = ui_ma_cac_read3,                |

|            | uo_ma_sdc_write = ui_ma_cac_write3,              |

|            | uo_ma_sdc_host_ld_mode = ui_ma_cac_host_ld_mode3 |

|            | uo_ma_sdc_sel = ui_ma_cac_sel3,                  |

|            | uo_ma_sdc_addr = ui_ma_cac_addr3,                |

|            | uo_ma_sdc_data = ui_ma_cac_data3                 |

|            |                                                  |

|            | from SDRAM controller to cache3:                 |

|            | ui_ma_sdc_ack = uo_ma_cac_ack3,                  |

|            | ui_ma_sdc_data = uo_ma_cac_data3                 |

| cache2     | When ui_ma_cac_miss3 = 0 and                     |

|            | ui_ma_cac_miss2 = 1,                             |

|            |                                                  |

|            | from cache2 to SDRAM controller:                 |

|            | uo_ma_sdc_read = ui_ma_cac_read2,                |

|            | uo_ma_sdc_write = ui_ma_cac_write2,              |

|            | uo_ma_sdc_host_ld_mode = ui_ma_cac_host_ld_mode2 |

|            | uo_ma_sdc_sel = ui_ma_cac_sel2,                  |

|            | uo_ma_sdc_addr = ui_ma_cac_addr2,                |

|            | uo_ma_sdc_data = ui_ma_cac_data2                 |

|            |                                                  |

|            | from SDRAM controller to cache2:                 |

|            | ui_ma_sdc_ack = uo_ma_cac_ack2,                  |

|            | ui_ma_sdc_data = uo_ma_cac_data2                 |

| cachel     | When ui_ma_cac_miss3 = 0 and                     |

| 274   | Output | or | Rehaviors | Corresi | nonding to | the States |

|-------|--------|----|-----------|---------|------------|------------|

| 4.1.4 | Output | UI | DEHAVIOIS | COLLES  | ponung to  | the States |

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

| [      |                                                  |

|--------|--------------------------------------------------|

|        | $ui_ma_cac_miss2 = 0$ and                        |

|        | ui_ma_cac_miss1 = 1,                             |

|        |                                                  |

|        | from cache1 to SDRAM controller:                 |

|        | uo_ma_sdc_read = ui_ma_cac_read1,                |

|        | uo_ma_sdc_write = ui_ma_cac_write1,              |

|        | uo_ma_sdc_host_ld_mode = ui_ma_cac_host_ld_mode1 |

|        | uo_ma_sdc_sel = ui_ma_cac_sel1,                  |

|        | uo_ma_sdc_addr = ui_ma_cac_addr1,                |

|        | uo_ma_sdc_data = ui_ma_cac_data1                 |

|        |                                                  |

|        | from SDRAM controller to cache1:                 |

|        | ui_ma_sdc_ack = uo_ma_cac_ack1,                  |

|        | ui_ma_sdc_data = uo_ma_cac_data1                 |

| cache0 | When ui_ma_cac_miss3 = 0 and                     |

|        | $ui_ma_cac_miss2 = 0$ and                        |

|        | $ui_ma_cac_miss1 = 0$ and                        |

|        | ui_ma_cac_miss $0 = 1$ ,                         |

|        |                                                  |

|        | from cache0 to SDRAM controller:                 |

|        | uo_ma_sdc_read = ui_ma_cac_read0,                |

|        | uo_ma_sdc_write = ui_ma_cac_write0,              |

|        | uo_ma_sdc_host_ld_mode = ui_ma_cac_host_ld_mode0 |

|        | uo_ma_sdc_sel = ui_ma_cac_sel0,                  |

|        | uo_ma_sdc_addr = ui_ma_cac_addr0,                |

|        | uo_ma_sdc_data = ui_ma_cac_data0                 |

|        |                                                  |

|        | from SDRAM controller to cache0:                 |

|        | ui_ma_sdc_ack = uo_ma_cac_ack0,                  |

|        | ui_ma_sdc_data = uo_ma_cac_data0                 |

| idle   | All outputs are received zero.                   |

|        |                                                  |

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

# Table 2-7-4: Memory Arbiter Output or Behaviours Corresponding to the States

#### **Chapter 3 Project Scope and Objectives**

This project aims to redesign existing memory system by changing write-through scheme to write-back scheme by adding a write buffer (FIFO) to improve the efficiency of previous memory system. A fully functionality verified and synthesis-ready model will be modelled in RTL using the Verilog HDL at the end of this project including the development of test specification, test plan, test vector and testbench which are written in Verilog HDL to ensure functional correctness and the performance.

#### **3.1 Project Objectives**

This project's objectives include:

- Design the write-back scheme direct mapped cache unit.

- Design the protocol of cache unit (cache controller block).

- Design the write buffer (FIFO).

- Design the protocol of write buffer (FIFO controller block).

- Modification on memory arbiter to compatible with new cache unit.

- Integration of cache unit, memory arbiter, SDRAM controller and SDRAM.

- Verified the functionality of the integrated unit (cache unit, memory arbiter, SDRAM controller and SDRAM) by construct proper test cases.

# **3.2 Impact and Significance**

As a summary to the problem statement, there is a lack of well-developed and wellfounded 32-bit RISC microprocessor core-based development environment. The development environment refers to the availability of the following:

- A well-developed design document, which includes the chip specification, architecture specification and micro-architecture specification.

- A fully functional well-developed 32-bit RISC architecture core in the form of synthesis-ready RTL written in Verilog HDL.

- A well-developed verification environment for the 32-bit RISC core. The verification specification should contain suitable verification methodology, verification techniques, test plans, testbench architectures etc.

- A complete physical design in Field Programmable Gate Array (FPGA) with documented timing and resource usage information.

With the available well-developed basic 32-bit RISC RTL model (which has been fully functional verified), the verification environment and the design documents, researchers can develop their own specific RTL model as part of the development environment (whether directly modifying the internals of the processor or interface to the processor) and can quickly verify their model to obtain results, without having to worry about the development of the verification environment and the modeling environment. This can speed up the research work significantly. For example, a researcher may have developed an image-processing algorithm and modified the algorithm to obtain a structure that suits the hardware implementation. The structure can be modeled in Verilog as part of a specialized datapath or as a coprocessor interfacing to the RISC processor.

## **Chapter 4 Method and Technologies Involved**

#### 4.1 Design Methodology

There are several types of design methodologies for design process:

- Top-down design methodology

- Bottom-up design methodology

- Mixed design methodology

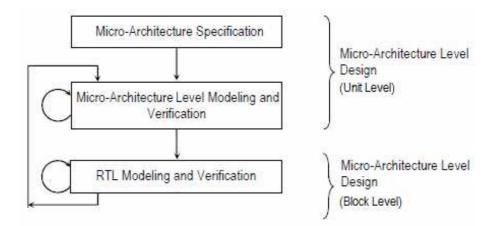

A top down design approach was adopted as the main design methodology in this project as shown in the following figure.

Figure 4-1-1 General Design Flow without Synthesis and Physical Design

This methodology put design partition reduces a complex design into smaller and a manageable piece thus provides step to step guideline that leading to a good design work and development of systems A good design methodology can ensure that functionality correctness in design, satisfaction in term of performance and power goals, can catches bugs at early stage, and provide good documentation for future references (Wolf 2004, p.22). This project only involved in micro-Architecture level design (Unit Level and Block Level) since higher architecture level had been complete and waiting for integration only.

#### **4.1.1 Micro-architecture Level Design (Unit Level)**

The alternate appellation of this level is RTL (Register Transfer Level). This level describes the internal design of architecture unit module with data flow. The unit module is partition into several blocks which each block have its own functionality to carry out the sub-function of the unit module to reduce complexity of design process.

#### **4.1.2 Micro-architecture Level Design (Block Level)**

This level further describes each partition from previous level which is block. Their specification are written in this level, normally carry following information such as:

- Functionality / Feature

- Block interface and I/O pin description

- Internal operation which include function table

- Schematic and block diagram

- Test plan

- Timing requirement

Once done with the micro-architecture specification, with the information in the specification, RTL modelling with High Level Language or Hardware Description Language (HDL) can be start. It is combination of behaviour and data flow synthesizable HDL model. Throughout the RTL modelling, Verilog will be use as the design language in this project. The model can be simulate and synthesis. The model is then need to go through verification process which verify the functionality of the design which need to meet the micro-architecture specification. Verification includes development of testbench, timing verification and functionality verification.

Faculty of Information and Communication Technology (Perak Campus), UTAR

#### **4.2 Design Tools**

#### 4.2.1 Verilog HDL Simulator - Mentor Graphics ModelSim SE-64 10.1c

Develop using Verilog Hardware Description Language (HDL) require a simulator tool that can provide simulation environment to verify the functional behaviours and waveform simulation. With multiple choices of HDL simulator in the market, a research had been to choose the most appropriate design tools for this project which affect by language supported, availability, price and etc. From the consideration above, ModelSim from Mentor Graphic is the best choice as a design tools for this project as they offer a free license for Student Edition, can found in internet and support Microsoft Windows platform. Although with some limitation, which is slower simulation speed than full version and have code limitation, but it is sufficient for this project as the scope of this project would not reach the limit.

## **Chapter 5 Memory System Specification**

**5.1 Partitioning and Design Hierarchy**

| Chip Partitioning at | Unit Partitioning at Micro- | Block and Functional Block |

|----------------------|-----------------------------|----------------------------|

| Architecture level   | Architecture Level          | Partitioning at RTL level  |

|                      |                             | (Micro-Architecture level) |

| Memory System unit   | u_cache (for data)          | b_cache_ctrl               |

|                      |                             | b_fifo_ctrl                |

|                      |                             | b_fifo                     |

|                      | u_cache (for instruction)   | b_cache_ctrl               |

|                      |                             | b_fifo_ctrl                |

|                      |                             | b_fifo                     |

|                      | u_mem_arbiter               | -                          |

|                      | u_sdram_controller          | b_sdc_fsm                  |

|                      |                             | b_sdc_sdram_if             |

|                      |                             | b_sdc_addr_mux             |

|                      |                             | b_sdc_obrt_top             |

|                      | sdram (mt48lc4m32b2)        | -                          |

Table 5-1-1 Design hierarchy for 32-bit Memory System

# **5.2 Memory System Specifications**

|                   | RISC32 with Integrated Main Memory  |

|-------------------|-------------------------------------|

| SDRAM             | 16MB                                |

| Instruction Cache | Direct mapped write-back cache, 2MB |

| Data Cache        | Direct mapped write-back cache, 2MB |

| Data Bus Width    | 32-bits                             |

| Instruction Width | 32-bits                             |

# Table 5-2-1 Specifications of the Memory System

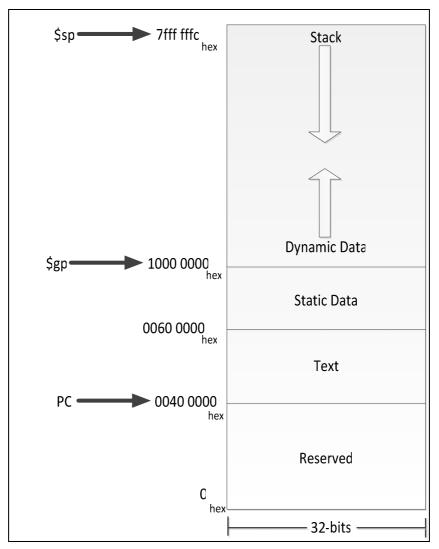

| 5.3 Memory Map |              |                                       |

|----------------|--------------|---------------------------------------|

| Segment        | Address      | Purpose                               |

| kseg2 – 1GB    | 0xFFFF FFFF  | Kernel module,                        |

|                |              | Page Table allocated here             |

|                | 0xC000 0000  |                                       |

| kseg1 – 512MB  | 0xBFFF FFFF  | Boot Rom                              |

|                |              | I/O Register (if below 512MB)         |

|                | 0xA000 0000  |                                       |

| kseg0 – 512MB  | 0x9FFF FFFF  | Direct view of memory to 512MB        |

|                |              | kernel code and data.                 |

|                |              | Exception and Page Table Base         |

|                |              | Register allocated here.              |

|                | 0x8000 0000  |                                       |

| kuseg – 2GB    | 0x7FFF FFFF  | Stack Segment starts from the ending  |

|                |              | address and expand down.              |

|                |              | Heap Segment starts from the starting |

|                |              | address and expand top.               |

|                | 0x1000 8000  |                                       |

|                | 0x1000 7FFF  | Data segment and Dynamic library      |

|                |              | code.                                 |

|                | 0x1000 0000  |                                       |

|                | 0x09FFF FFFF | Code Segment, where the main          |

|                |              | program stored.                       |

|                | 0x0040 0000  |                                       |

|                | 0x003F FFFF  | Reserved                              |

|                |              |                                       |

|                | 0x0000 0000  |                                       |

Table 5-3-1 Virtual memory map of 32-bits MIPS

# • Stack Segment

• Use for storing automatic variables, which are variables that allocated and de-allocated automatically when program flow.

# • Heap Segment

• Use for dynamic memory allocation such as malloc(), realloc() and free().

# • Data Segment

• Use for storing global or static variables that initialize by programmer.

#### • Code Segment

• Use for storing codes of main program or main program instructions.

## **5.4 Architecture of Memory System**

Figure 5-4-1 Architecture of Memory System

#### **Chapter 6 Micro-Architecture Specification**

#### 6.1 Cache Unit

Figure 6-1-1 Block diagram of cache unit

This is a direct mapped write-back cache with write buffer. The functionalities of Cache Unit are:

- 1. Store a small fraction of data (for D-Cache) or instructions (for I-Cache) of main memory.

- 2. Output desired data or instruction to CPU when it issues a READ.

- 3. Write data into desired location as instructed by CPU (D-Cache only).

- 4. Send signal to stall the CPU when read miss or write miss.

5. Communicate with SDRAM Controller to write back 'dirty' block of data back into SDRAM and fetch new block of data from it.

#### 6.4 Cache Unit I/O Description

#### **Input pins**

Pin name: ui\_cac\_clk

Pin class: Global

**Path:** External  $\rightarrow$  Cache

**Description:** System clock signal.

Pin name: ui\_cac\_rst

Pin class: Global

**Path:** External  $\rightarrow$  Cache

**Description:** System reset signal.

**Pin name:** ui\_cac\_cpu\_data[31:0]

Pin class: Data

**Path:** CPU→ Cache

Description: 32-bits data from CPU that to be written into the cache.

**Pin name:** ui\_cac\_cpu\_addr[31:0]

Pin class: Address

**Path:** CPU→ Cache

Description: 32-bits address from CPU that indicates the location that to be accessed.

**Pin name:** ui\_cac\_cpu\_read

Pin class: Control

**Path:** CPU→ Cache

**Description:** A control signal that enables the read from cache based on ui\_cac\_cpu\_addr[31:0] when it is asserted (HIGH).

Pin name: ui\_cac\_cpu\_write

Pin class: Control

**Path:** CPU→ Cache

**Description:** A control signal that enables the write of data into cache based on ui\_cac\_cpu\_addr[31:0] when asserted (HIGH).

**Pin name:** ui\_cac\_mem\_ack

Pin class: Control

**Path:** Memory Arbiter  $\rightarrow$  Cache

BIT (Hons) Computer Engineering

**Description:** Acknowledge signal (active HIGH) to indicate read data is ready from SDRAM (read from SDRAM) or SDRAM prepare to receive data (write to SDRAM).

**Pin name:** ui\_cac\_mem\_data[31:0]

Pin class: Data

**Path:** Memory Arbiter  $\rightarrow$  Cache

**Description:** 32-bits data that is read from SDRAM.

Pin name: ui\_cac\_mem\_lmc\_same

Pin class: Status

**Path:** Memory Arbiter  $\rightarrow$  Cache

Description: Indicate the configuration of SDRAM is same when asserted (HIGH).

**Output pins**

Pin name: uo\_cac\_cpu\_data[31:0]

Pin class: Data

**Path:** Cache→ CPU

**Description:** 32-bits data that to be output to CPU.

**Pin name:** uo\_cac\_cpu\_stall

Pin class: Control

Path: Cache → CPU

**Description:** A status signal that used to stall the pipelines.

Pin name: uo\_cac\_miss

Pin class: Status

**Path:** Cache → Memory Arbiter

**Description:** A status signal indicates cache miss.

**Pin name:** uo\_cac\_mem\_read

Pin class: Control

**Path:** Cache → Memory Arbiter

**Description:** Read signal that indicate need read from SDRAM.

**Pin name:** uo\_cac\_mem\_write

Pin class: Control

Path: Cache → Memory Arbiter

Description: Write signal that indicate need write data into SDRAM.

BIT (Hons) Computer Engineering

**Pin name:** uo\_cac\_mem\_sel[3:0]

Pin class: Control

**Path:** Cache → Memory Arbiter

Description: 4-bits control signals to mask which byte of the 4 bytes (32-bits) data

goes in or comes out from SDRAM.

When it is '1', the corresponding byte will enable.

When it is '0', the corresponding byte will be masked and the output becomes 'z'.

**Pin name:** uo\_cac\_mem\_addr[31:0]

Pin class: Address

**Path:** Cache → Memory Arbiter

**Description:** 32-bits address that indicates which location in the SDRAM to be accessed.

**Pin name:** uo\_cac\_mem\_data[31:0]

Pin class: Data

**Path:** Cache → Memory Arbiter

**Description:** 32-bits data that to be written in to the SDRAM.

**Pin name:** uo\_cac\_mem\_lmc\_data[31:0]

Pin class: Data

**Path:** Cache → Memory Arbiter

**Description:** 32-bits data that configure the SDRAM.

Pin name: uo\_cac\_mem\_data\_ready

Pin class: Status

Path: Cache → Memory Arbiter

**Description:** When asserted (HIGH), data is ready write back from FIFO to SDRAM.

Pin name: uo\_cac\_mem\_complete

Pin class: Status

Path: Cache → Memory Arbiter

Description: Indicates one block of data was written into SDRAM when HIGH.

# Table 6-4-1: Cache Unit I/O Descriptions

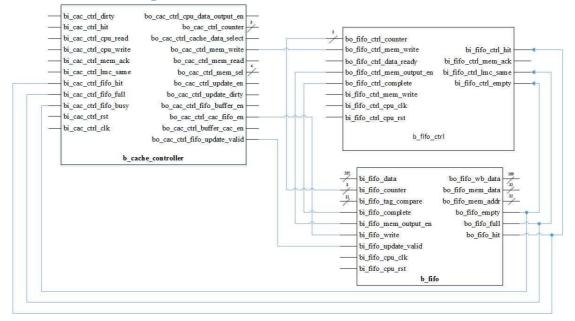

#### 6.5 Block Partitioning of Cache Unit

Figure 6-5-1 Block Partition of Cache Unit

#### **6.6 Cache Controller Block**

|                       | che controller                |

|-----------------------|-------------------------------|

| 1977 (J. 1978)        | bo cac ctrl fifo update vali  |

| bi cac ctrl clk       | bo cac ctrl buffer cac e      |

| bi_cac_ctr1_rst       | bo cac ctrl cac fifo e        |

| bi_cac_ctrl_fifo_busy | bo_cac_ctrl_fifo_buffer_e     |

| bi_cac_ctrl_fifo_full | bo_cac_ctrl_update_dirt       |

| bi_cac_ctrl_fifo_hit  | bo_cac_ctrl_update_e          |

| bi_cac_ctrl_lmc_same  | bo_cac_ctrl_mem_se            |

| bi_cac_ctr1_mem_ack   | bo_cac_ctrl_mem_rea           |

| bi_cac_ctrl_cpu_write | bo_cac_ctrl_mem_writ          |

| bi_cac_ctrl_cpu_read  | bo_cac_ctrl_cache_data_selec  |

| bi_cac_ctrl_hit       | bo_cac_ctrl_counter           |

| bi_cac_ctrl_dirty     | bo_cac_ctrl_cpu_data_output_e |

Functionalities of Cache Controller:

- 1. Control main activity of cache unit.

- 2. Determine data to read when read hit.

- 3. Determine data to be updated when write hit.

- 4. Determine data to read from SDRAM when miss.

- 5. Output control signal and status signal to write back data from FIFO to cache.

- 6. Output control signal to move dirty data from cache to FIFO.

- 7. Output control signal and status signal out to CPU and SDRAM.

## 6.6.1 Cache Controller block I/O description

| Input pins                                                                                                    |  |  |

|---------------------------------------------------------------------------------------------------------------|--|--|

| Pin name: bi_cac_ctrl_clk                                                                                     |  |  |

| Pin class: Global                                                                                             |  |  |

| <b>Path:</b> External $\rightarrow$ Cache $\rightarrow$ Cache Controller                                      |  |  |

| Description: System clock signal.                                                                             |  |  |

| Pin name: bi_cac_ctrl_rst                                                                                     |  |  |

| Pin class: Global                                                                                             |  |  |

| <b>Path:</b> External $\rightarrow$ Cache $\rightarrow$ Cache Controller                                      |  |  |

| <b>Description:</b> System reset signal.                                                                      |  |  |

| Pin name: bi_cac_ctrl_lmc_same                                                                                |  |  |

| Pin class: Status                                                                                             |  |  |

| <b>Path:</b> Memory Arbiter $\rightarrow$ Cache $\rightarrow$ Cache Controller                                |  |  |

| <b>Description:</b> Indicates the configuration of SDRAM is same when asserted (HIGH).                        |  |  |

| Pin name: bi_cac_ctrl_mem_ack                                                                                 |  |  |

| Pin class: Control                                                                                            |  |  |

| <b>Path:</b> SDRAM controller $\rightarrow$ Memory Arbiter $\rightarrow$ Cache $\rightarrow$ Cache Controller |  |  |

| Description: Acknowledge signal (active HIGH) to indicate read data is ready from                             |  |  |

| SDRAM(read from SDRAM) or SDRAM prepare to receive data (write to SDRAM).                                     |  |  |

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

**Pin name:** bi\_cac\_ctrl\_cpu\_write

Pin class: Control

**Path:** CPU $\rightarrow$  Cache  $\rightarrow$  Cache Controller

**Description:** A control signal that enables the write of data into cache based on ui\_cac\_cpu\_addr[31:0] when asserted (HIGH).

**Pin name:** bi\_cac\_ctrl\_cpu\_read

Pin class: Control

**Path:** CPU $\rightarrow$  Cache  $\rightarrow$  Cache Controller

**Description:** A control signal that enables the read from cache based on ui\_cac\_cpu\_addr[31:0] when it is asserted (HIGH).

**Pin name:** bi\_cac\_ctrl\_hit

Pin class: Status

**Path:** Cache  $\rightarrow$  Cache Controller

**Description:** Asserted when (tag == tag\_ram) && (valid\_ram == 1).

**Pin name:** bi\_cac\_ctrl\_dirty

Pin class: Status

**Path:** Cache  $\rightarrow$  Cache Controller

**Description:** Asserted when dirty\_ram == 1.

Pin name: bi\_cac\_ctrl\_fifo\_busy

Pin class: Status

**Path:** FIFO  $\rightarrow$  Cache Controller

Description: HIGH when FIFO is writing into SDRAM.

**Pin name:** bi\_cac\_ctrl\_fifo\_full

Pin class: Status

**Path:** FIFO  $\rightarrow$  Cache Controller

**Description:** Status signal that indicate FIFO is full.

**Pin name:** bi\_cac\_ctrl\_fifo\_hit

Pin class: Status

**Path:** FIFO  $\rightarrow$  Cache Controller

Description: Status Signal that FIFO contain same tag and index with the physical

address tag and index.

BIT (Hons) Computer Engineering

Output pins

**Pin name:** bo\_cac\_ctrl\_cpu\_data\_output\_en

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

Description: When asserted (HIGH), data is enabled to be output to CPU.

**Pin name:** bo\_cac\_ctrl\_counter[2:0]

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

**Description:** 3-bits counter value. This is used to count the data when transferring a whole block (8 words) of data.

**Pin name:** bo\_cac\_ctrl\_cache\_data\_select

Pin class: Control

**Path:** Cache  $\rightarrow$  Cache Controller $\rightarrow$  Cache

**Description:** Instruct the cache datapath which data (data from cpu or data from SDRAM) to be written into.

When HIGH, choose data from SDRAM.

When LOW, choose data from CPU.

**Pin name:** bo\_cac\_ctrl\_mem\_read

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache  $\rightarrow$  Memory Arbiter  $\rightarrow$  SDRAM Controller  $\rightarrow$  SDRAM

**Description:** Read signal that indicate need read from SDRAM.

Pin name: bo\_cac\_ctrl\_mem\_write

Pin class: Control

**Path:** Cache Controller → FIFO controller

**Description:** Write signal that indicate need write data into SDRAM.

Pin name: bo\_cac\_ctrl\_mem\_sel [3:0]

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache  $\rightarrow$  Memory Arbiter

Description: 4-bits control signals to mask which byte of the 4 bytes (32-bits) data

goes in or comes out from SDRAM.

When it is '1', the corresponding byte will enable.

BIT (Hons) Computer Engineering

When it is '0', the corresponding byte will be masked and the output becomes 'z'.

**Pin name:** bo\_cac\_ctrl\_update\_en

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

**Description:** Enables the update of cache when asserted (HIGH).

**Pin name:** bo\_cac\_ctrl\_update\_dirty

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

**Description:** Enables the update of 'Dirty' when asserted (HIGH).

**Pin name:** bo\_cac\_ctrl\_fifo\_buffer\_en

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

Description: Enable to move write back data from FIFO to temporary buffer.

**Pin name:** bo\_cac\_ctrl\_cac\_fifo\_en

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

**Description:** Enable to move cache data to FIFO.

**Pin name:** bo\_cac\_ctrl\_buffer\_cac\_en

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  Cache

Description: Enable to move write back data from temporary buffer to cache.

**Pin name:** bo\_cac\_ctrl\_fifo\_update\_valid

Pin class: Control

**Path:** Cache Controller → FIFO

**Description:** Control signal that update the valid bit in FIFO.

# Table 6-6-1: Cache Controller Block I/O Descriptions

6.6.2 Cache Controller State Diagram

Figure 6-6-2 State Diagram of Cache Controller

## **6.7 FIFO Controller Block**

| bo_fifo_ctrl_mem_write     | bi_fifo_ctrl_hit      |

|----------------------------|-----------------------|

| bo_fifo_ctrl_data_ready    | bi_fifo_ctrl_mem_ack  |

| bo_fifo_ctrl_mem_output_en | bi_fifo_ctrl_lmc_same |

| bo_fifo_ctrl_complete      | bi_fifo_ctrl_empty    |

| bi_fifo_ctrl_mem_write     |                       |

| bi_fifo_ctrl_cpu_clk       |                       |

| bi_fifo_ctrl_cpu_rst       |                       |

|                            |                       |

Figure 6-7-1 Block diagram of FIFO Controller Block

Functionalities of FIFO Controller:

- 1. Control main activity of FIFO block.

- 2. Send control signal to FIFO to write data back to SDRAM behind the scene.

# 6.7.1 FIFO Controller block I/O description

| Input pins                                                                        |

|-----------------------------------------------------------------------------------|

| Pin name: bi_fifo_ctrl_cpu_clk                                                    |

| Pin class: Global                                                                 |

| <b>Path:</b> External $\rightarrow$ Cache $\rightarrow$ FIFO Controller           |

| Description: System clock signal.                                                 |

| Pin name: bi_fifo_ctrl_cpu_rst                                                    |

| Pin class: Global                                                                 |

| <b>Path:</b> External $\rightarrow$ Cache $\rightarrow$ FIFO Controller           |

| <b>Description:</b> System reset signal.                                          |

| Pin name: bi_fifo_ctrl_hit                                                        |

| Pin class: Status                                                                 |

| <b>Path:</b> FIFO $\rightarrow$ FIFO Controller                                   |

| Description: Status Signal that FIFO contain same tag and index with the physical |

BIT (Hons) Computer Engineering

Faculty of Information and Communication Technology (Perak Campus), UTAR

address tag and index.

Pin name: bi\_fifo\_ctrl\_mem\_write

Pin class: Control

**Path:** Cache Controller  $\rightarrow$  FIFO controller

**Description:** Write signal that indicate need write data into SDRAM

**Pin name:** bi\_fifo\_ctrl\_mem\_ack

Pin class: Control

**Path:** SDRAM controller  $\rightarrow$  Memory Arbiter  $\rightarrow$  Cache  $\rightarrow$  FIFO Controller

Description: Acknowledge signal (active HIGH) to indicate read data is ready from

SDRAM(read from SDRAM) or SDRAM prepare to receive data (write to SDRAM).

**Pin name:** bi\_fifo\_ctrl\_lmc\_same

Pin class: Status

**Path:** Memory Arbiter  $\rightarrow$  FIFO Controller

**Description:** Indicate the configuration of SDRAM is same when asserted (HIGH).

**Pin name:** bi\_fifo\_ctrl\_empty

Pin class: Status

**Path:** FIFO  $\rightarrow$  FIFO Controller

Description: When asserted, it indicate FIFO is empty.

**Output pins**

**Pin name:** bo\_fifo\_ctrl\_counter [2:0]

Pin class: Control

Path: FIFO Controller → FIFO

Description: 3-bits counter value. This is used to count the data when transferring a

whole block (8 words) of data.

**Pin name:** bo\_fifo\_ctrl\_mem\_write

Pin class: Control

**Path:** FIFO Controller  $\rightarrow$  Memory Arbiter

Description: Write signal that indicate need write data from FIFO into SDRAM.

Pin name: bo\_fifo\_ctrl\_data\_ready

Pin class: Status

**Path:** FIFO Controller  $\rightarrow$  Memory Arbiter

BIT (Hons) Computer Engineering

**Description:** When asserted (HIGH), data is ready write back from FIFO to SDRAM.

**Pin name:** bo\_fifo\_ctrl\_mem\_output\_en

Pin class: Control

**Path:** FIFO Controller  $\rightarrow$  FIFO

Description: Enable data in FIFO to be written into SDRAM

Pin name: bo\_fifo\_ctrl\_complete

Pin class: Control

**Path:** FIFO Controller  $\rightarrow$  Memory Arbiter

Description: Indicates one block of data was written into SDRAM when HIGH.

# Table 6-7-1: Cache Controller Block I/O Descriptions

# 6.7.2 FIFO Controller State Diagram

Figure 6-7-2 State Diagram of Cache Controller

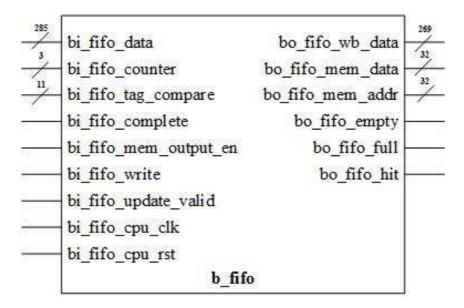

#### **6.8 FIFO Block**

Figure 6-8-1 Block diagram of FIFO Block

This FIFO block consists of 4 entries to store data block from cache. The functionalities of FIFO block are:

- 1. Store dirty block from cache that need to written back to SDRAM

- 2. Data able to written back to cache or back to SDRAM.

- 3. Communicate with SDRAM to written data back to SDRAM when SDRAM is free.

- 4. Compare tag and index to indicate whether same block of data need to accessed next in cache.

- 5. Output a full signal when 4 entries are used.

- 6. Output an empty signal when FIFO contains no data.

| 6.8.1 FIFO Controller block I/O description                                   |

|-------------------------------------------------------------------------------|

| Input pins                                                                    |

| Pin name: bi_fifo_cpu_clk                                                     |

| Pin class: Global                                                             |

| <b>Path:</b> External $\rightarrow$ Cache $\rightarrow$ FIFO                  |

| Description: System clock signal.                                             |

| Pin name: bi_fifo_cpu_rst                                                     |

| Pin class: Global                                                             |

| <b>Path:</b> External $\rightarrow$ Cache $\rightarrow$ FIFO                  |

| <b>Description:</b> System reset signal.                                      |

| Pin name: bi_fifo_update_valid                                                |

| Pin class: Control                                                            |

| <b>Path:</b> Cache Controller $\rightarrow$ FIFO                              |

| Description: Control signal that update the valid bit in FIFO.                |

| Pin name: bi_fifo_write                                                       |

| Pin class: Control                                                            |

| <b>Path:</b> Cache Controller $\rightarrow$ FIFO                              |

| <b>Description:</b> Write signal that indicate data write from cache to FIFO. |

| Pin name: bi_fifo_mem_output_en                                               |

| Pin class: Control                                                            |

| Path: FIFO controller → FIFO                                                  |

| Description: Enable data in FIFO to be written into SDRAM                     |

| Pin name: bi_fifo_complete                                                    |

| Pin class: Status                                                             |

| <b>Path:</b> FIFO controller $\rightarrow$ FIFO                               |

| Description: Indicates one block of data was written into SDRAM when HIGH.    |

| Pin name: bi_fifo_tag_compare[10:0]                                           |

| Pin class: Address                                                            |

| Path: Cache → FIFO                                                            |

| Description: Tag from physical address that used to compare FIFO_hit signal   |

| BIT (Hons) Computer Engineering                                               |

BIT (Hons) Computer Engineering Faculty of Information and Communication Technology (Perak Campus), UTAR

**Pin name:** bi\_fifo\_counter [2:0]

Pin class: Control

**Path:** FIFO Controller → FIFO

**Description:** 3-bits counter value. This is used to count the data when transferring a whole block (8 words) of data.

**Pin name:** bi\_fifo\_data [284:0]

Pin class: Data

Path: Cache→ FIFO

**Description:** contain index from physical address, tag\_ram, data\_ram and byte\_ram from cache.

**Output pins**

Pin name: bo\_fifo\_hit

Pin class: Status

**Path:** FIFO Controller  $\rightarrow$  Cache Controller

**Description:** Status Signal that FIFO contain same tag and index with the physical address tag and index.

Pin name: bo\_fifo\_full

Pin class: Status

**Path:** FIFO  $\rightarrow$  Cache Controller and FIFO Controller

**Description:** Status signal that indicate FIFO is full.

Pin name: bo\_fifo\_empty

Pin class: Status

**Path:** FIFO  $\rightarrow$  Cache Controller

**Description:** When asserted, it indicate FIFO is empty.

**Pin name:** bo\_fifo\_mem\_addr[31:0]

Pin class: Address

**Path:** FIFO  $\rightarrow$  Memory Arbiter  $\rightarrow$  SDRAM controller  $\rightarrow$  SDRAM

**Description:** 32-bits address that indicates which location in the SDRAM to be accessed.

Pin name: bo\_fifo\_mem\_data [31:0]

Pin class: Data

BIT (Hons) Computer Engineering

**Path:** FIFO  $\rightarrow$  Memory Arbiter  $\rightarrow$  SDRAM controller  $\rightarrow$  SDRAM

**Description: :** 32-bits data that to be written in to the SDRAM.

Pin name: bo\_fifo\_wb\_data [268:0]

Pin class: Data

**Path:** FIFO  $\rightarrow$  Cache

**Description:** Contain all data that need to write back to cache (data, tag and byte).

Table 6-8-1: FIFO Block I/O Descriptions

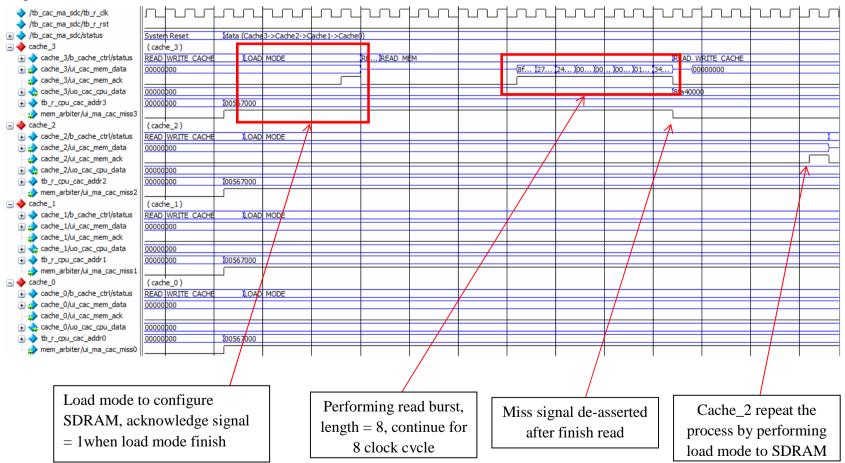

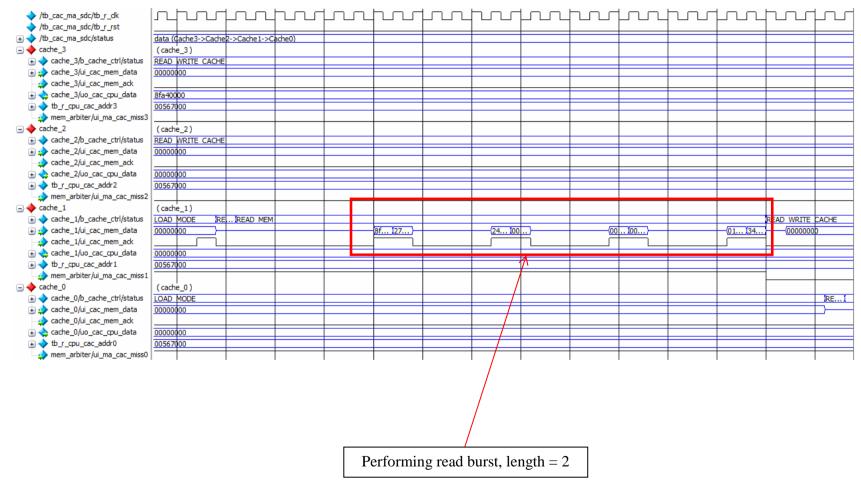

# **Chapter 7 Verification**

# 7.1 Test Plan

| Function To be Tested              | Test Case                                                                     |

|------------------------------------|-------------------------------------------------------------------------------|

| Test 1: System Reset               | tb_r_rst is asserted to high at least one clock cycle                         |

| Test 2: Testing Cache priority and | Different load mode configuration with burst                                  |

| reading in different burst length  | length 1, 2, 4 and 8.                                                         |

|                                    | tb_r_BL_sel[3] = 3'd3;//burst length = 8                                      |

|                                    | tb_r_BL_sel[2] = 3'd2; ;//burst length = 4                                    |

|                                    | $tb_r_BL_sel[1] = 3'd1; ;//burst length = 2$                                  |

|                                    | $tb_r_BL_sel[0] = 3'd1; ;//burst length = 2$                                  |

|                                    | $tb_r_cpu_cac_addr3 = 32'h00567000;$                                          |

|                                    | tb_r_cpu_cac_addr2 = 32'h00567000 ;<br>tb_r_cpu_cac_addr1 = 32'h00567000 ;    |

|                                    | $tb_1_cpu_cac_addr1 = 32'h0050'000',$<br>$tb_r_cpu_cac_addr0 = 32'h00567000;$ |

|                                    | 10_1_epu_eae_add10 = 32100307000,                                             |

|                                    | $tb_r_cpu_cac_read3 = 1;$                                                     |

|                                    | $tb_r_cpu_cac_write3 = 0;$                                                    |

|                                    | $tb_r_cpu_cac_read2 = 1;$                                                     |

|                                    | tb_r_cpu_cac_write2 = 0;                                                      |

|                                    | $tb_r_cpu_cac_read1 = 1;$                                                     |

|                                    | tb_r_cpu_cac_write1 = 0;                                                      |

|                                    | $tb_r_cpu_cac_read0 = 1;$                                                     |

|                                    | tb_r_cpu_cac_write0 = 0;                                                      |

| Test 3 : Write Hit in Cache 3 and  | First write instruction,                                                      |

| continuous Write Hit               | tb_r_cpu_cac_data3 = 32'h07070707;                                            |

|                                    | tb_r_cpu_cac_addr3 = 32'h00567004;                                            |

|                                    | tb_r_cpu_cac_read3 = 0;                                                       |