# OPTIMIZATION OF AN INTEGRATED CIRCUIT DEVICE BY IMPROVING ITS VLSI DESIGN FROM RTL TO GDSII

# THEE KANG WEI

A project report submitted in partial fulfilment of the requirements for the award of the degree of Bachelor of Engineering (Hons) Electronic Engineering

Faculty of Engineering and Green Technology

Universiti Tunku Abdul Rahman

January 2016

# **DECLARATION**

I hereby declare that this project report is based on my original work except for citations and quotations which have been duly acknowledged. I also declare that it has not been previously and concurrently submitted for any other degree or award at UTAR or other institutions.

| Signature | : |  |

|-----------|---|--|

|           |   |  |

| Name      | : |  |

|           |   |  |

| ID No.    | : |  |

|           |   |  |

|           |   |  |

Date

# APPROVAL FOR SUBMISSION

I certify that this project report entitled "OPTIMIZATION OF AN INTEGRATED CIRCUIT DEVICEBY IMPROVING ITS VLSI DESIGN FROM RTL TO GDSII" was prepared by THEE KANG WEI has met the required standard for submission in partial fulfilment of the requirements for the award of Bachelor of Engineering (Hons) Electronic Engineering at Universiti Tunku Abdul Rahman.

| Approved by,                |  |

|-----------------------------|--|

|                             |  |

| Signature :                 |  |

| Supervisor: Dr. Yeap Kim Ho |  |

| Date ·                      |  |

The copyright of this report belongs to the author under the terms of the copyright Act 1987 as qualified by Intellectual Property Policy of Universiti Tunku Abdul Rahman. Due acknowledgement shall always be made of the use of any material contained in, or derived from, this report.

© 2016, Thee Kang Wei. All right reserved.

#### **ACKNOWLEDGEMENTS**

I would like to thank everyone who had contributed to the successful completion of this project. I would like to express my gratitude to my research supervisor, Dr. Yeap Kim Ho for his invaluable advice, guidance and his enormous patience throughout the development of the research.

Besides, I would like to thank to my project Co-supervisor, Mr. Cheah Hun Wah for his useful advices and guidance throughout the development of the project.

Moreover, I would like to thank to Mr. Sree for his technical guidance throughout the development of the project.

In addition, I would also like to express my gratitude to my loving parent and friends who had helped and given me encouragement.

# OPTIMIZATION OF AN INTEGRATED CIRCUIT DEVICE BY IMPROVING ITS VLSI DESIGN FROM RTL TO GDSII

#### **ABSTRACT**

VLSI design flow from RTL to GDSII consists of two phases, namely front-end design and back-end design. In this project, the front-end design and back-end design were done in order to improve and optimize an 8051 microcontroller-based core. Logic synthesis, physical design, physical verification and others are done by using EDA tools, namely Synopsys Design Compiler and Synopsys IC Compiler. EDA tools provide the design automations for IC design process which can reduce the design TAT. In order to reduce the design cost, the chip-area is reduced as small as possible. The performance of the chip is improved by 10 times of its original clock frequency. Most of the violations that exist in the design are fixed. The optimized gate-level netlist is generated by Design Compiler in ddc format. The final layout is generated by IC Compiler. The layout and netlist have passed the verifications like static timing analysis and others. Lastly, the GDSII file is streamed out from IC Compiler.

# TABLE OF CONTENTS

| <b>DECLARA</b> | TION    |          |                                              | ii  |

|----------------|---------|----------|----------------------------------------------|-----|

| APPROVAL       | L FOR S | SUBMISS  | SION                                         | iii |

| ACKNOWI        | LEDGEN  | MENTS    |                                              | v   |

| ABSTRACT       | Γ       |          |                                              | vi  |

| TABLE OF       | CONTE   | ENTS     |                                              | vii |

| LIST OF TA     | ABLES   |          |                                              | X   |

| LIST OF FI     | GURES   |          |                                              | xi  |

| LIST OF SY     | MBOL    | S / ABBR | REVIATIONS                                   | XV  |

| LIST OF A      | PPENDI  | CES      |                                              | xvi |

|                |         |          |                                              |     |

|                |         |          |                                              |     |

| CHAPTER        |         |          |                                              |     |

|                |         |          |                                              |     |

| 1              | INTR    | ODUCTI   | ON                                           | 1   |

|                | 1.1     | Backgro  | ound                                         | 1   |

|                | 1.2     | Problen  | n Statements                                 | 4   |

|                | 1.3     | Aims a   | nd Objectives                                | 5   |

|                |         |          |                                              |     |

| 2              | LITE    | RATURE   | REVIEW                                       | 6   |

|                | 2.1     | VLSI D   | Design Flow                                  | 6   |

|                | 2.2     | Digital  | Design Using VHDL                            | 9   |

|                | 2.3     | Logic S  | Synthesis                                    | 10  |

|                |         | 2.3.1    | Logic Synthesis Tools with Design Automation | 10  |

|                |         | 2.3.2    | Synopsys Design Compiler                     | 12  |

|                | 2.4     | Physica  | al Design                                    | 13  |

|                |         | 2.4.1    | Partitioning                                 | 15  |

|   |      |         |                                      | viii |

|---|------|---------|--------------------------------------|------|

|   |      | 2.4.2   | Floor-planning                       | 16   |

|   |      | 2.4.3   | Placement                            | 16   |

|   |      | 2.4.4   | Routing                              | 17   |

|   |      | 2.4.5   | Physical Verification                | 17   |

|   |      | 2.4.6   | Tools for Physical Design            | 19   |

| 3 | MET  | HODOL   | OGY                                  | 20   |

|   | 3.1  | VLSI l  | Design Methodology                   | 20   |

|   |      | 3.1.1   | Register Transfer Level (RTL) Design | 23   |

|   |      | 3.1.2   | Logic Synthesis                      | 24   |

|   |      | 3.1.3   | Static Timing Analysis               | 25   |

|   |      | 3.1.4   | Floor-plan                           | 25   |

|   |      | 3.1.5   | Power Network Synthesis              | 26   |

|   |      | 3.1.6   | Clock Tree Synthesis                 | 26   |

|   |      | 3.1.7   | Placement and Routing                | 27   |

|   |      | 3.1.8   | Chip Finishing                       | 27   |

|   |      | 3.1.9   | Physical Verification                | 28   |

|   | 3.2  | Design  | n Compiler                           | 29   |

|   |      | 3.2.1   | Data Setup                           | 31   |

|   |      | 3.2.2   | Technology Mapping and Optimization  | 31   |

|   |      | 3.2.3   | Design Checking                      | 31   |

|   |      | 3.2.4   | Post-synthesis Output Data           | 31   |

|   | 3.3  | IC Cor  | npiler                               | 32   |

|   |      | 3.3.1   | Data Setup                           | 34   |

|   |      | 3.3.2   | Floor-planning                       | 35   |

|   |      | 3.3.3   | Placement                            | 36   |

|   |      | 3.3.4   | Clock Tree Synthesis                 | 37   |

|   |      | 3.3.5   | Routing                              | 37   |

|   |      | 3.3.6   | Chip Finishing                       | 37   |

| 4 | RESU | JLTS AN | ID DISCUSSIONS                       | 39   |

|   | 4.1  | Logic   | Synthesis                            | 39   |

|   |      | 4.1.1   | Design Compilation and Translation   | 39   |

|      |        | 4.1.2   | Check    | ing D  | <b>D</b> esigr | 1          |           |             | 42     |

|------|--------|---------|----------|--------|----------------|------------|-----------|-------------|--------|

|      |        | 4.1.3   | Static   | Tin    | ning           | Analysis   | before    | Mapping     | and    |

|      |        | Optimi  | ization  |        |                |            |           |             | 43     |

|      |        | 4.1.4   | Area     | of     | the            | Design     | before    | Mapping     | and    |

|      |        | Optimi  | ization  |        |                |            |           |             | 44     |

|      |        | 4.1.5   | Power    | Ana    | lysis l        | before Map | oping and | l Optimizat | ion45  |

|      |        | 4.1.6   | Mappi    | ng ar  | nd Op          | timization |           |             | 47     |

|      |        | 4.1.7   | Analys   | sis af | ter M          | apping and | d Optimiz | zation Proc | ess 48 |

|      |        | 4.1.8   | Outpu    | tting  | Gate-          | Level Net  | list      |             | 53     |

|      | 4.2    | Physic  | al Desig | n      |                |            |           |             | 54     |

|      |        | 4.2.1   | Librar   | y Set  | up             |            |           |             | 54     |

|      |        | 4.2.2   | Floor-   | plann  | ing            |            |           |             | 55     |

|      |        | 4.2.3   | Placen   | nent a | and R          | outing     |           |             | 64     |

|      |        | 4.2.4   | Design   | n R    | Rule           | Checking   | g Fixin   | ig and      | Final  |

|      |        | Verific | eations  |        |                |            |           |             | 68     |

| 5    | CON    | CLUSIO  | N AND    | REC    | OMN            | MENDAT     | IONS      |             | 75     |

|      | 5.1    | Conclu  | ısion    |        |                |            |           |             | 75     |

|      | 5.2    | Recom   | mendati  | ons    |                |            |           |             | 76     |

| REFE | RENCE  | S       |          |        |                |            |           |             | 78     |

| APPE | NDICES | S       |          |        |                |            |           |             | 81     |

# LIST OF TABLES

| TABLE                       | TITLE                                   | PAGE |

|-----------------------------|-----------------------------------------|------|

| Table 3.1: Examples of      | f Commands Used for Design Compiler     | 30   |

| Table 3.2: Script Files     | that are Included into Design Compile   | 30   |

| Table 3.3: Examples of      | f Command that Used for IC Compiler     | 33   |

| Table 3.4: Script Files     | that are Included into IC Compiler      | 34   |

| Table 4.1: Modes or Process | Options of the Mapping and Optimization | 48   |

| Table 5.1: Summary of       | f the Design Improvement                | 76   |

# LIST OF FIGURES

| FIGURE      | TITLE                                                                              | PAGE |

|-------------|------------------------------------------------------------------------------------|------|

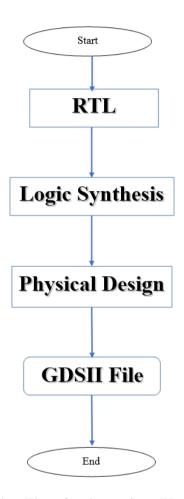

| Figure 1.1: | Design Flow for the project (Kang et al., 2015)                                    | 3    |

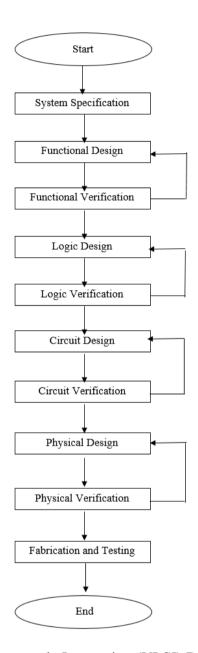

| Figure 2.1  | : Top-down Very-large-scale Integration (VLSI)<br>Design Flow (Das, 2010)          | 8    |

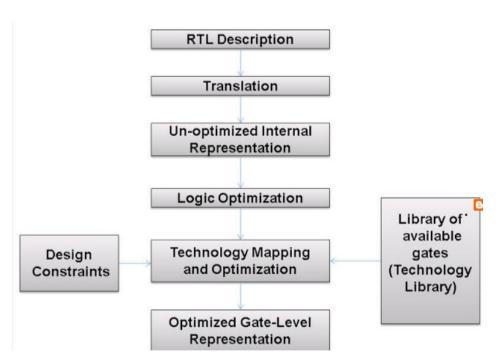

| Figure 2.2: | Logic Synthesis Flow by using Electronic Design<br>Automation Tools (Chirag, 2012) | 11   |

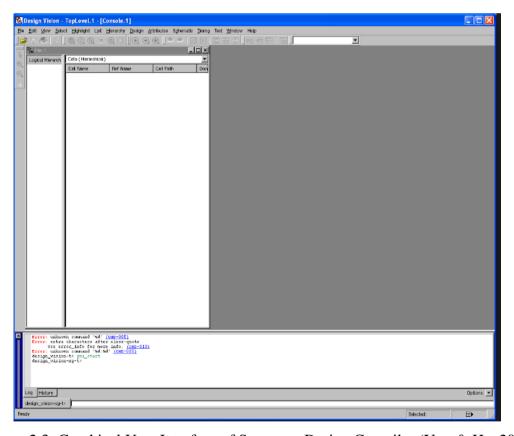

| Figure 2.3  | : Graphical User Interface of Synopsys Design<br>Compiler (Yun & Ha, 2009)         | 12   |

| Figure 2.4: | Synopsys Design Compiler dc_shell user interface (Steven & Zhao, 2010)             | 13   |

| Figure 2.5: | Physical Design Flow (Das, 2010)                                                   | 14   |

| Figure 2.6: | Graphical User Interface of IC Compiler (Derek, 2016)                              | 19   |

| Figure 3.1: | Very-large-scale Integration (VLSI) Front-end Design Flow                          | 21   |

| Figure 3.2: | Very-large-scale Integration (VLSI) Back-end Design Flow                           | 22   |

| Figure 3.3: | Hierarchical Level of the Core Unit (Oregano System, 2012)                         | 24   |

| Figure 4.1: | Result of Automated Library Setup                                                  | 40   |

| Figure 4.2: | Result of Loading Design                                                           | 40   |

| Figure 4.3: | Results of Compilation                                                             | 40   |

| Figure 4.4: | Result of Linking Process                                                          | 41   |

| Figure 4.5: | Result of the Libraries Checking                                                   | 41   |

| Figure 4.6: Design Issue                                                  | 42 |

|---------------------------------------------------------------------------|----|

| Figure 4.7: Static Timing Analysis Report before Mapping and Optimization | 44 |

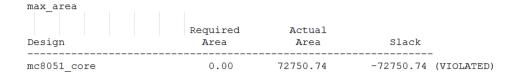

| Figure 4.8: Area of the Design before Mapping and Optimization            | 45 |

| Figure 4.9: Power Report before Mapping and Optimization                  | 46 |

| Figure 4.10: Status of the Mapping and Optimization Process               | 48 |

| Figure 4.11: Timing Report with Timing Issues                             | 51 |

| Figure 4.12: Timing Report without Timing Issues                          | 52 |

| Figure 4.13: Area Report Generated by the Tool                            | 52 |

| Figure 4.14: Power Report of the Design                                   | 52 |

| Figure 4.15: Report of the Constraint Checking                            | 53 |

| Figure 4.16: Result of the Checking Design                                | 53 |

| Figure 4.17: Status of the Outputting Netlist                             | 53 |

| Figure 4.18: Status of Design Library Setup                               | 54 |

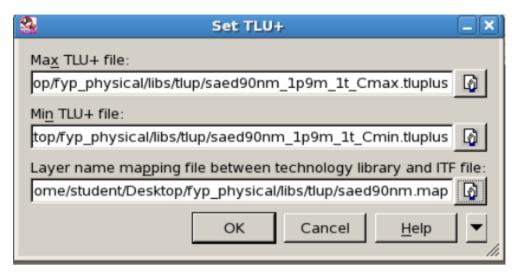

| Figure 4.19: Setting Tluplus Files                                        | 55 |

| Figure 4.20: Status of the Loading Design                                 | 55 |

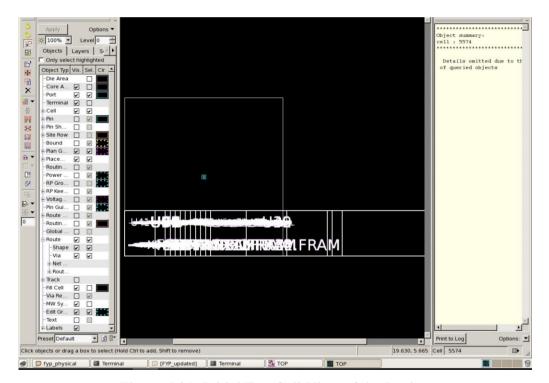

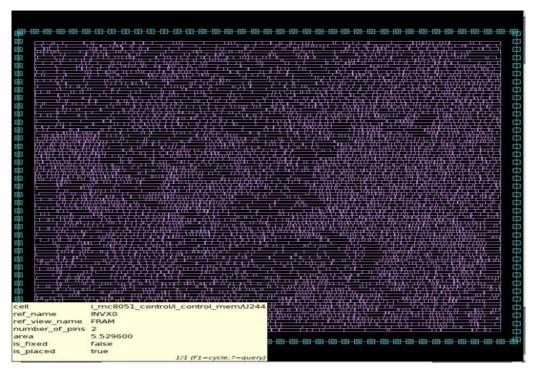

| Figure 4.21: Initial Top Cell View of the Design                          | 58 |

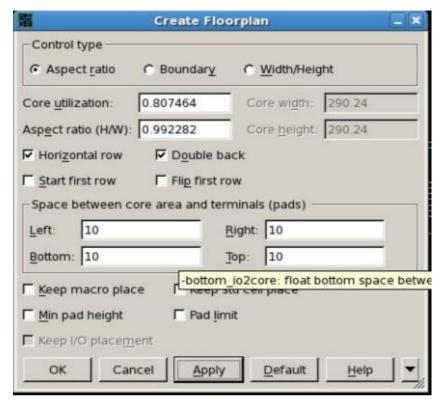

| Figure 4.22: Creating Floor-plan                                          | 59 |

| Figure 4.23: Created Floor-plan                                           | 59 |

| Figure 4.24: Virtual Placement                                            | 60 |

| Figure 4.25: Virtual Placement Report                                     | 60 |

| Figure 4.26: Chip Summary                                                 | 60 |

| Figure 4.27: Congestion Report                                            | 61 |

| Figure 4.28: Congestion Map with GRCs                                     | 61 |

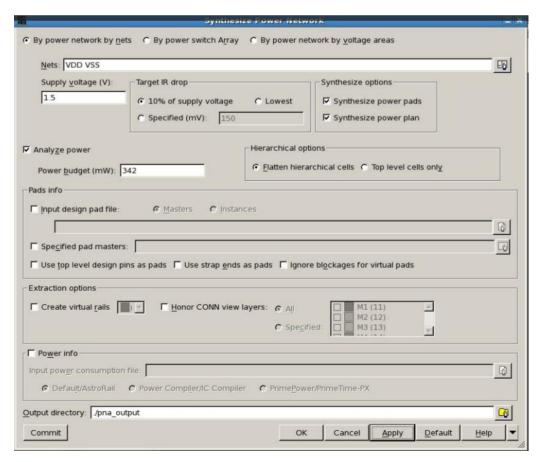

| Figure 4.29: Virtual Power Pad on the Top Hierarchy of the Design         | 62 |

| Figure 4.30: PNS setting                                   | 62 |

|------------------------------------------------------------|----|

| Figure 4.31: PNA Power Map                                 | 63 |

| Figure 4.32: PNS Report for VDD Nets                       | 63 |

| Figure 4.33: PNS Report for VSS Nets                       | 63 |

| Figure 4.34: Checking Design Report                        | 65 |

| Figure 4.35: Options for Placement                         | 65 |

| Figure 4.36: Status of Placement                           | 65 |

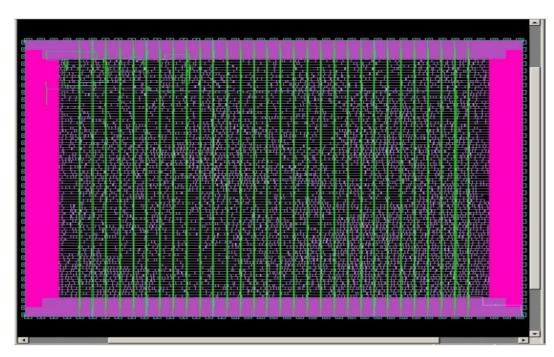

| Figure 4.37: Layout after Placement and Power Nets Routing | 66 |

| Figure 4.38: CTS Status                                    | 66 |

| Figure 4.39: Clock Tree Summary                            | 66 |

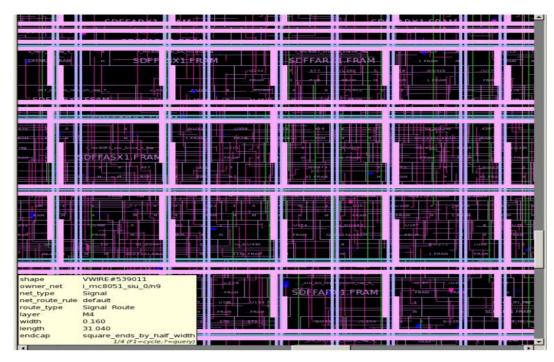

| Figure 4.40: Result of Clock Tree Routing (Global Routing) | 66 |

| Figure 4.41: Summary of the Initial Routing                | 67 |

| Figure 4.42: Summary of Detail Routing and Optimization    | 67 |

| Figure 4.43: Summary of ECO Routing                        | 67 |

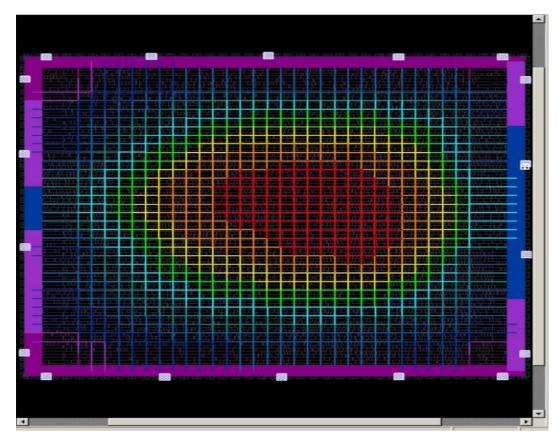

| Figure 4.44: Congestion Heat Map                           | 70 |

| Figure 4.45: Congestion Heat Map with Ratios               | 71 |

| Figure 4.46: Power Map of the Design                       | 71 |

| Figure 4.47: Result of the ECO Routing                     | 72 |

| Figure 4.48: Result of LVS Verification                    | 72 |

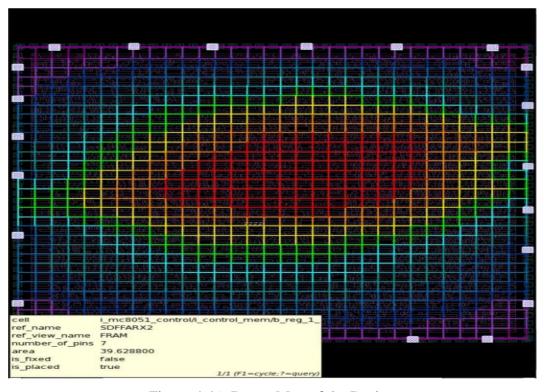

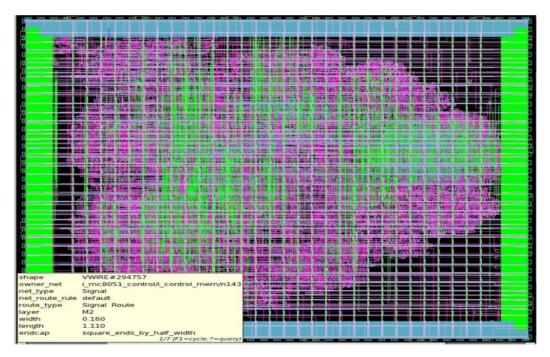

| Figure 4.49: Final Layout                                  | 72 |

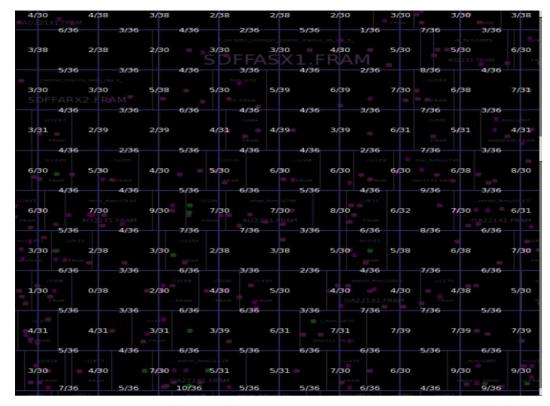

| Figure 4.50: Centre of the Layout                          | 73 |

| Figure 4.51: Final Timing Report                           | 73 |

| Figure 4.52: Final Area Report                             | 74 |

| Figure 4.53: Final Power Report                            | 74 |

| Figure 4.54: Status of Stream Out Process                  | 74 |

#### LIST OF SYMBOLS / ABBREVIATIONS

CAD Computer-Aided Design

CTS Clock Tree Synthesis

ddc Optimized Netlist File Format (include constraints)

def Scan Chain Information File Format

DRC Design Rule Checks

EDA Electronic Design Automation

GDSII Graphic Databese System II

GUI Graphical User Interface

HDL Hardware Description Language

IC Integrated Circuit

Intel Corp. Intel Corporation

IR Voltage (Current \* Resistance)

I/O Input and Output

LVS Layout Versus Schematic

MHz Mega Hz (Frequency)

MOSFET Metal-oxide-semiconductor Field-effect Transistor

PNS Power Network Synthesis

P/G Power and Ground

RTL Register Transfer Level

sdc Design Constraint Output File Format

SoC System-on-Chip

STA Static Timing Analysis

Synopsys, Inc. Synopsys Incorporate

TAT Turn-around Time

TLU+ RC Model File Format

VHDL VHSIC Hardware Description Language

VLSI Very-large-scale Integration

# LIST OF APPENDICES

| APPENDIX            | TITLE                                 | PAGE |

|---------------------|---------------------------------------|------|

| APPENDIX A: Project | Timeline                              | 81   |

| APPENDIX B: Synops  | sys Start-up File for Design Compiler | 82   |

| APPENDIX C: Synops  | sys Start-up File for IC Compiler     | 84   |

#### **CHAPTER 1**

#### INTRODUCTION

# 1.1 Background

Based on the report from the Semiconductor Industry Association (SIA) in 2007, the global sales of semiconductor reached at the level in term of billions dollar with the amount of 255.6 billion US dollar (Jiang et al., 2008). From the report, we know that semiconductor is profitable and it provided a very high profit margin for semiconductor based companies. In real life, computers, smartphones, home appliances, personal digital assistants devices and entertainment devices, rely on integrated circuit or IC chip to operate. (Jiang et al., 2008). So, semiconductor industry plays a significant role in our daily lives.

In this technology era, every field consist of relationships and formulae that are useful and beneficial for technology development (Ethan, 2006). The founder of Intel Corporation, Gordon Moore, predicted the density of the transistors incorporated in an IC will approximately double every two years. This prediction is known as Moore's Law and it is still valid until today (Intel Corp, no date). The foundry has been continuously inventing advanced IC process technology in approximately every 24 months by significant scaling down the Metal Oxide Field Effect transistors (MOSFETs) in order to improve chip performance and also to reduce chip area as stated by Moore's Law (Samar, 2013). Due to the continuous scaling down of MOSFETs, the dimensions of MOSFETs are gradually approaching their physical restriction. Consequently, the development of advanced semiconductor

technology according to Moore's Law is being slowed down recently (Samar, 2013). However, Moore's Law is still an influential concept in current semiconductor industry development (Ethan, 2006).

Process of developing an IC by packing millions of transistors into a single chip, with smaller die size, is known as Very-Large Scale Integration or VLSI (Kang *et al.*, 2015). As VLSI technology becomes advanced, a complex system can be embedded into a single chip, known as System-on-Chip (SoC) (Chang & Kim 2006). At the meantime, multi-core SoC can be implemented by recent technology.

In order to design a SoC, extremely long design turnaround time (TAT) is required (Ryota *et al.* 1985). The full-custom design approach requires even more TAT (Ryota *et al.* 1985). Because of this, Engineering Design Automation (EDA) tools are invented to overcome the problems. Shorter TAT in designing a complex SoC by using EDA tools (Ryota *et al.* 1985). EDA tools provide automatic design approaches for IC design which can minimize the required TAT (Ryota *et al.* 1985). For instance, the design approaches are auto place and route, gate-level optimization, STA, CTS and etc. Therefore, EDA tools are important in IC design industry.

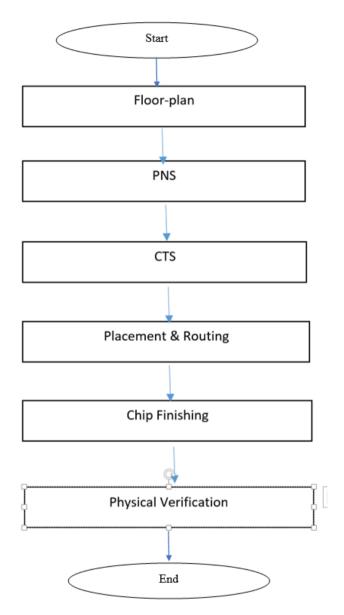

The VLSI design flow can be used as the guide for the project. The design flow of the project is shown in Figure 1.1. RTL stands for Register Transfer Level. In this stage, the behaviour and the function of the design are described in Hardware Description Language (HDL) format. For logic synthesis, it is a process of converting the RTL source codes into optimized gate level netlist (Kang *et al.*, 2015). For physical design, it is the process of converting the optimized gate-level netlist into geometrical representation of the design which is known as layout (Kang *et al.*, 2015). GSDII file, a binary file, consists of cell references and the geometry parameters of the cells (Steven, 1994). All labelled texts, geometric shapes of the cell and other information about the layout are represented by Graphical Database System (GDSII) file (Steven, 1994).

Figure 1.1: Design Flow for the project (Kang et al., 2015)

#### 1.2 Problem Statements

The problem statements of the project are stated below:

- For designing an IC from RTL to GDSII, longer TAT is required.

- Low performance of 8051 microcontroller is low due to the low clock frequency.

- Design cost for an IC is higher.

- Timing closure of the design becomes worse when increasing the clock frequency.

Before the EDA tools are invented, all designs are done from scratch. The designers need to draw logic gates of the design on the papers and then translate the logic gate into layout by drawing the layout on the papers. This is a time consuming process for IC design. Therefore, longer TAT is required for designing an IC without using EDA tools.

The older version of 8051 microcontroller has low clock frequency and hence causes low performance. Typically, the clock frequency of the older microcontroller is about 12 MHz (Intel Corp., n.d.). Since the clock frequency is lower, the performance of the chip is quite restricted. When the chip area is larger, the fabrication cost is also higher and hence the design cost of the IC will be increased,

After increasing the clock frequency, the timing closure of the design become worse and eventually the timing violations like setup violations and hold violations will appear.

# 1.3 Aims and Objectives

The objectives of the project are shown as follows:

- i) To complete the VLSI design flow from RTL to GDSII.

- ii) To reduce the design TAT by using EDA tools with design automation.

- iii) To reduce the design cost by chip-area optimization.

- iv) To improve the performance by increasing the clock frequency.

- v) To improve the timing closure after the clock frequency is increased.

In this project, I will go through the full IC design flow. I will go through logic synthesis, physical design, physical verification and others. EDA tools provide the design automations for IC design process which can reduce the design TAT. In order to reduce the design cost, the chip-area is reduced as small as possible. As mentioned earlier, the clock frequency of the original 8051 microcontroller is around 12 MHz. In this project, I will try to increase the frequency as high as possible in order to improve the performance of the chip. Some of the blocks like RAM and ROM are taken out from the design. The RAM and ROM blocks are not be implemented into layout. After increasing the frequency, timing violations will appear. Those violations will be fixed in order to improve the timing closure after the clock frequency has increased.

#### **CHAPTER 2**

#### LITERATURE REVIEW

# 2.1 VLSI Design Flow

VLSI design flow is a series of steps that is used to translate and synthesize the specifications of a system into a chip (Das, 2010). The design flow is shown in Figure 2.1. This VLSI design flow is known as top-down VLSI design flow (Das, 2010). To begin with, the flow starts with the system specifications. The specifications of the design such as speed, power and area are specified. The next phase is functional design. In this phase, the design is specified in the behavioural model and then translated into RTL (Das, 2010). After the system specification is done, the next phase is functional verification. In this phase, the design is checked in terms of functionality (Das, 2010). Further verification for RTL is done in order to check the syntax and functionality of the RTL (Das, 2010). If the functionality of the design does not meet the requirements, the designer will perform the functional design again in order to achieve the design requirements (Das, 2010). After the functional verification phase, the subsequent phase is logic design. In this phase, the designers design the logic networks of the system by following the functional descriptions of the design (Das, 2010). At the meantime, the I/O characteristic is used at the functional design level (Das, 2010). Basically the RTL is converted into logic-level representation in this phase. The logic-level networks are then stored as logic-level netlist (Das, 2010). Furthermore, the logic verification is used to verify the correctness of the netlist (Das, 2010). The following phases are circuit design and circuit verification. The logic-level netlist is translated into electronic network by using transistors (Das, 2010). Further verification is done for the circuit-level representation. Once the circuit design and verification are completed, the next step is physical design. The circuit-level netlist is translated into physical layout (Das, 2010). Further verification is done for physical layout such as DRC, LVS check and others (Das, 2010). The final step is fabrication and testing. The physical layout is converted into a finished silicon chip (Das, 2010). Further verifications are then done to test the functionality and characteristic of the chip (Das, 2010). These sequences of design flow illustrate the top-down design approach for the IC design (Das, 2010).

Figure 2.1: Top-down Very-large-scale Integration (VLSI) Design Flow (Das, 2010)

# 2.2 Digital Design Using VHDL

Usually, the functional descriptions and behavioural descriptions of the system are expressed in HDL. There are two popular HDL languages, namely VHDL and Verilog HDL (Das, 2010).

VHDL languages can be used to model a digital system at RTL (Das, 2010). In this level, the functional descriptions and behavioural descriptions of the system are coded into VHDL format. VHDL has 5 basic constructs, namely sequential statements, concurrent statement, netlist statements, timing specifications and waveform generation (Das, 2010).

The hardware abstraction of VHDL has two views, namely external view and internal view (Das, 2010). External view is represented by **Entity** (Das, 2010). Meantime, the internal view is represented by **Architecture**. **Entity** is used for only port specification design (Das, 2010). It models all input and output ports of the design (Das, 2010). On the other hands, **Architecture** representing the actual internal specifications of the hardware like logic functions and interconnects (Das, 2010). The relationship between input and output ports are represented by Architecture (Das, 2010).

Generally, four different architecture styles can be used for VHDL modelling (Das, 2010). Namely, structural modelling, behaviour modelling, dataflow modelling and mixed modelling (Das, 2010). In behavioural modelling, the behavioural representation in the form of truth table can be used for behavioural modelling style of the system (Das, 2010). Besides, the specifications of the system are described in the form of Boolean equations is known as dataflow modelling (Das, 2010). In structural modelling, the interconnections of the system which consists of basic building blocks and logic gates are described (Das, 2010).

## 2.3 Logic Synthesis

Logic synthesis is a process of translating the high-level description of the design in RTL into an optimized gate-level netlist (Das, 2010). Logic synthesis is a set of techniques that is used for VLSI design industry (Bernard *et al.*, 1989). Recently, CAD approach is popular for electronic system design (Das, 2010). Of course, logic synthesis can be done by using CAD approach.

## 2.3.1 Logic Synthesis Tools with Design Automation

Recently, several logic synthesis tools are being developed based on the CAD approach. Logic synthesis tools are the EDA software that provides design automations for IC designers (Das, 2010). Usually, the logic synthesis expressions are included into the algorithms of the tools (Bernard *et al.*, 1989). These expressions refer to automate design procedure that is used to generate gate-level Boolean networks for physical design (Bernard *et al.*, 1989).

Generally, logic synthesis tools provide design automations which are able to reduce design TAT significantly (Das, 2010). For instance, the design automation is automatic translating the RTL description of the design into gate-level netlist (Das, 2010). Besides, the tools provide automatic chip area, power and power optimization (Das, 2010).

Typically, a VLSI chip consists of hundreds or even thousands of logic gates. Consequently, manual synthesis at all levels becomes impractical due to huge number of logic gates (Das, 2010). Nevertheless, using EDA tools for logic synthesis is more convenient and practical.

Figure 2.2 shows the logic synthesis flow by using EDA tools. To begin with, the RTL description of the design like RTL codes in VHDL format is translated into un-optimized internal representation. Basically, the un-optimized internal

representation is a type of data structure that is used to store the information of the design (Das, 2010). Next, the logic optimization is performed by the tools based on the Karnaugh map optimization approach (Das, 2010). Before technology mapping and optimization, the design constraints and technology library are applied to the tools. Design constraints are known as design goals such as operating condition, chip area, clock frequency, clock uncertainty, load and others (Das, 2010). Technology library is also known as standard cell library. Standard cell library is a type of database library which consists of logic gate and macro cells like flip-flop, adder and multiplexer (Das, 2010). After that, technology mapping and optimization are performed by the tools. Generally, technology mapping is a process of connecting the selected elements from the standard cell library in such a way as to achieve the predefined synthesis goals and functionality of the design (Eugenio & Pablo, 1995). On the other hand, optimization is a process of applying the logic transformations to the design based on the design constraints (Eugenio & Pablo, 1995). Eventually, the optimized gate-level netlist is generated by the tools.

Figure 2.2: Logic Synthesis Flow by using Electronic Design Automation Tools (Chirag, 2012)

# 2.3.2 Synopsys Design Compiler

The popular synthesis tool is Design Compiler from Synopsys Inc. In the Synopsys synthesis product family, Design Compiler is the core synthesis engine. It consists of two user interface, known as dc\_shell; a command line interface and GUI (Thomas & William, 2010). Figure 2.3 shows the GUI of the Design Compiler. Figure 2.4 shows the dc\_shell user interface. Synopsys Design Compiler can be used to constrain a design for area and timing, apply synthesis techniques to achieve area and timing closure, analyse the results and generate design data that works with physical design or layout tools (Synopsys Inc, 2010).

Figure 2.3: Graphical User Interface of Synopsys Design Compiler (Yun & Ha, 2009)

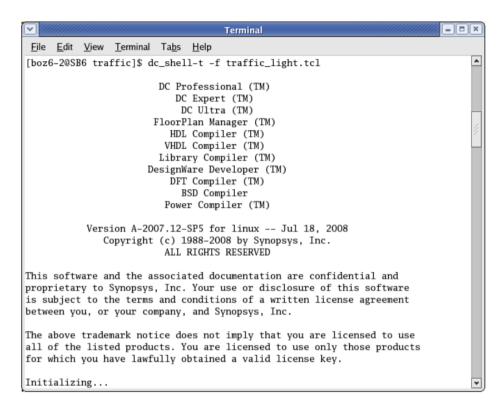

Figure 2.4: Synopsys Design Compiler dc\_shell user interface (Steven & Zhao, 2010)

# 2.4 Physical Design

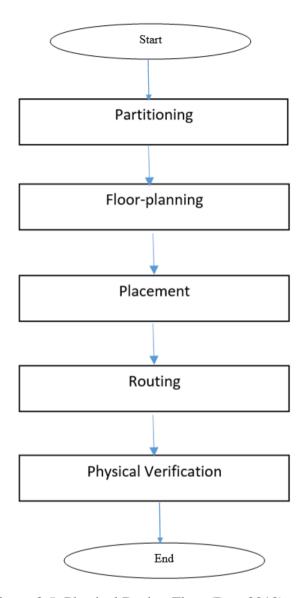

Physical design is a process of converting gate-level netlist into geometric representation which is known as layout (Das, 2010). The layout consists of standard cells, routings, clock trees, power nets and other information (Das, 2010). Figure 2.5 shows the physical design flow.

Figure 2.5: Physical Design Flow (Das, 2010)

## 2.4.1 Partitioning

A VLSI chip consists of thousands of logic gates. Due to the complexity of the design, the layout of the entire design cannot be handled at the same time. Normally, the complex design is partitioned into smaller subsystem in order to minimize the complexity of the design during physical design (Chen, 2009). The implementation of entire design cannot be performed at the same time due to the limitation on memory space and computation power (Jeffery *et al.*, 2009). Thus, partitioning plays an important role in physical design stage.

Generally, decomposing the design into a set of smaller subcircuits or blocks is known as partitioning (Jeffery *et al.*, 2009). After decomposition, each subcircuit or block can be designed simultaneously and independently. An interface specification that is used for connecting all the subcircuits or blocks is generated (Jeffery *et al.*, 2009). The interconnects that is used to connect the blocks or subsystems are required. The collection of those interconnects is known as netlist (Jeffery *et al.*, 2009).

There are a few factors that need to be considered for partitioning. Namely, size of the blocks or subcircuits, the number of blocks or subcircuits and the number of interconnects between the subcircuits or blocks (Jeffery et al., 2009).

The partitioning process for standard cell designs is non-hierarchical (Jeffery *et al.*, 2009). Generally, the partitioning algorithms is used to partition the circuit into a set of unconnected sub-circuits such that each sub-circuit corresponds to a cell in a standard cell design library (Jeffery *et al.*, 2009). The non-hierarchical form is used for standard cell designs in term of partitioning procedure (Jeffery *et al.*, 2009).

## 2.4.2 Floor-planning

In the floor-planning stage, the chip is planned in such a way to accommodate all design components like standard cells, macros, memory units and it's interconnects within a minimum area (Das, 2010). The area of the chip that is used for accommodate those design components can be calculated (Jeffery *et al.*, 2009). The interconnects of the chip and the location of the standard cells need to be determined in order to minimized of the chip area (Jeffery *et al.*, 2009).

#### 2.4.3 Placement

After the floor-planning stage, the area accommodated by each component of the chip and the number of terminals are defined (Jeffery *et al.*, 2009). The process of arranging the components of the chip on the specified area is known as placement (Jeffery *et al.*, 2009). The steps for placement include determining the position of each components on the chip, determining the minimum area arrangement for the components on the chip which can allows the completion of routing without any violations and lastly place those components on the chip according to defined positions (Jeffery *et al.*, 2009). After the placement, all of the components of the design like standard cells, macros and IPs are placed on to the defined core area accordingly with minimum area (Jeffery *et al.*, 2009).

In a standard cell library, the height of each standard cell is defined equally (Jeffery et al., 2009). This means that the standard cells have same height compared to others standard cells in the standard cell library (Jeffery et al., 2009). In standard cell design style, all cells are placed in rows by minimizing the heights of all the channels and the width of the widest row (Jeffery et al., 2009). The total area of the chip is the summation of required placement area and required routing area (Jeffery et al., 2009). The process of routing area estimation which determine the channel height, play an important role in determining the overall chip area (Jeffery et al.,

2009). The empty spaces over the standard cell rows are then used for routing (Jeffery *et al.*, 2009).

# 2.4.4 Routing

Routing is a process of determining the geometrical representation which is known as layout of all the nets of the chip (Jeffery *et al.*, 2009). This process is used for interconnecting the components on the chip based on the netlist (Jeffery *et al.*, 2009). The area which is not accommodated by the components is partitioned into rectangular regions known as channel and switchbox (Jeffery *et al.*, 2009). The channel and switchbox are utilized by the routers in order to complete the routing between the all components on the chip (Jeffery *et al.*, 2009). Further optimization can be done based on the constraints (Jeffery *et al.*, 2009).

Standard cell rows are determined with uniform lengths channels (Jeffery *et al.*, 2009). In order to minimize the height of the channel, all the nets in the channel must be routed (Jeffery *et al.*, 2009). Further optimization can be done based on the routing constraints (Jeffery *et al.*, 2009). For instance, the constraints are restricting length of the critical nets within some acceptable limits and minimizing the length of the longer nets (Jeffery *et al.*, 2009).

# 2.4.5 Physical Verification

Physical verification is a process of verifying the IC design for manufacturability and electrical connectivity rules (Rajesh *et al.*, 2014). The three major steps in physical verification are DRC, LVS checks and parasitic extraction (Chang *et al.*, 1999).

The physical verification can be done by automation (Rajesh *et al.*, 2014). The scripts required by the EDA tools to perform physical verification are generated by the algorithms when developing the layout and runset files of DRC and LVS

checks (Rajesh *et al.*, 2014). These files are then executed in the terminal command line in order to automate the physical verification process (Rajesh *et al.*, 2014). The result also are generated by automation (Rajesh *et al.*, 2014).

Design Rule Checker (DRC) is a process of analysing the design by a given set of design rules (Das, 2010). The DRC is performed in order to ensure that the design is compromised with a set of manufacturing process rules (Chang *et al.*, 1999). For instance, the rule can be the minimum space between adjacent lines (Chang *et al.*, 1999).

Basically, technology library which consists of a set of design rules is provided by the foundry (Rajesh *et al.*, 2014). The DRC can be done by the design automation that provided by EDA tools (Rajesh *et al.*, 2014).

On the other hand, Layout versus Schematic (LVS) check is a process of comparing the netlist derived from the layout with the original netlist (Chang *et al.*, 1999). Basically, the original netlist comes from design synthesis phase (Chang *et al.*, 1999). The netlist derived from layout is basically generated after the routing process is done (Chang *et al.*, 1999). Generally, the LVS check is done by the tools automatically.

Besides, parasitic extraction is a process of obtaining the parasitic elements of the design from the geometrical information and material properties of the design (Das, 2010). For instance, the parasitic elements are resistance, capacitance and inductance (Das, 2010). This process basically can be done by the design automation that provided by the tools. The tools will automatic obtaining the parasitic elements from the layout and generating the report for parasitic verification.

# 2.4.6 Tools for Physical Design

The EDA tools provide the design automations such as auto placement, auto routing, physical verification and others. The TAT for physical design can be reduced by using EDA tools.

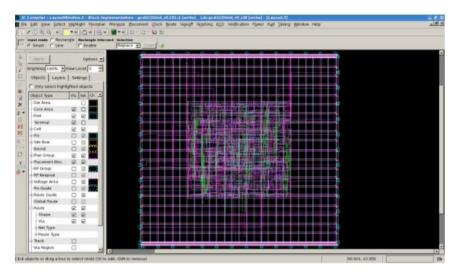

Synopsys IC Compiler can be used for hierarchical chip-level design planning known as floor-planning, placement, CTS, routing and physical verification (Synopsys Inc, 2007.). IC compiler takes an optimized gate-level netlist with design constraints file as the input and produces layout as an output (Derek, 2016). Figure 2.6 shows the graphical user interface (GUI) of the IC compiler.

Figure 2.6: Graphical User Interface of IC Compiler (Derek, 2016)

#### **CHAPTER 3**

#### **METHODOLOGY**

## 3.1 VLSI Design Methodology

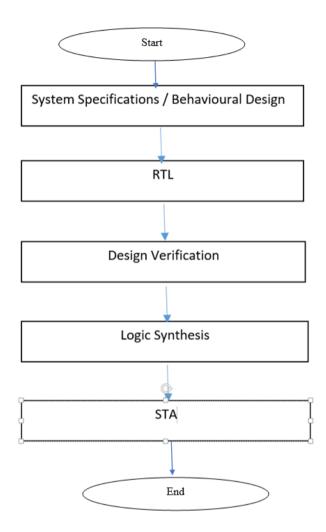

VLSI design process is expensive especially in the design phase and fabrication phases. Consequently, the absolute discipline in the design phase is critical and significant. A proven design methodology is required in order to ensure the design is succeed at the first attempt. Therefore, VLSI design methodology is important and critical in IC design industry. Figure 3.1 shows the design flow for front-end design. Figure 3.2 shows the design flow for back-end design.

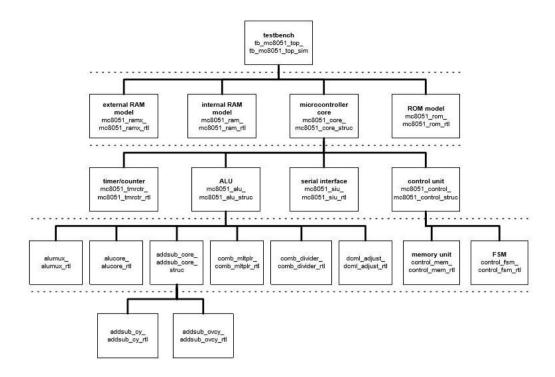

The front-end design process consists of system specifications / behavioural design, RTL design, design verification, logic synthesis and STA. In this project, the RTL source codes are retained from the Oregano System. The RTL codes are verified by the Oregano System. The system specifications / behavioural design, RTL design and design verification are done by the Oregano system. Therefore, the system specifications / behavioural design, RTL design and design verification methodology will not be taken for this project.

The back-end design is the design methodology for layout generation. Basically, the back-end design is known as physical design. In fact, physical design process consists of Floor-plan, PNS, CTS, placement & routing, STA, chip finishing, post-layout verification, physical verification and finally tape out. In this project, Synopsys IC Compiler is used for physical design. The methodology for physical design process will be discussed in following subsections.

Figure 3.1: Very-large-scale Integration (VLSI) Front-end Design Flow

Figure 3.2: Very-large-scale Integration (VLSI) Back-end Design Flow

# 3.1.1 Register Transfer Level (RTL) Design

The RTL codes are provided by the Oregano System. The syntax of the codes and functionality of the design are verified by the Oregano System.

The design is coded using the VHDL format. The designers coded the design separately. In this project, only the core of the design will be implemented. Since the RTL codes for the core are designed separately, thus the RTL codes need to be combined by according to design hierarchical level. Figure 3.2 shows the hierarchical level of the core unit. The codes are combined by following the hierarchical level of the design that is shown in Figure 3.2. Note that only mc8051\_core is implemented. Therefore, top hierarchy is mc8051\_core.

Figure 3.3: Hierarchical Level of the Core Unit (Oregano System, 2012)

# 3.1.2 Logic Synthesis

The RTL codes are imported to the EDA tool which is Design Compiler from Synopsys Inc. The RTL codes are then synthesized into optimized gate-level netlist based on the design constraints. The design constraints can be timing constraints and area constraints. The technology process of the logic gates, flip-flops and wire model is specified in the target cell library by the foundry. So, the target cell library must be provided for the tool in order to perform technology mapping and optimization. The gate-level netlist can be optimized for speed, performance, area and power through the design constraints.

### 3.1.3 Static Timing Analysis

STA is performed on fully synchronous designs to validate the timing performance of the design. The speed and timing constraints must be provided to the tool as an input for STA. For instance, the design constraints can be clock period, input delay, output delay, load capacitance, wire capacitance, wire load model, clock uncertainty and clock transition.

A wire load model is used for synthesis and STA in order to achieve early timing closure. Besides, the operating condition that provided by the foundry need to be specified in design constraints. STA checks all possible timing violation paths under worst case operating condition. The STA that is provided by the tool is quite efficient and accurate. Once the design is free form timing violations, next steps which is physical design will be carried on. The next section will discuss about the back-end design methodology for this project.

### 3.1.4 Floor-plan

In floor-planning stage, core utilization ratio is set to the appropriate value in order to give margins for routability. The utilization ratio is the ratio between height of the core area and the length of the core area. The extra space requirements for power networks and clock tree routing need to be taken into consideration during the setup of core utilization ratio. Usually, few iterations are required for the process.

The core utilization ratio setup is important for weighting the trade-off between the routability of the chip and chip area. Setting the core utilization ratio too high resulting the increasing of chip area and hence causes the design cost to increase. Besides, the timing closure for critical paths becomes worse due to long routing can be happened if the ratio is set too high.

### 3.1.5 Power Network Synthesis

There must be sufficient power and ground pins in order to drive up the chip to its operating voltage level. The sufficient power and ground nets can minimize the power the ground noise from interfering. Placement constraints script can be used to perform the placement of these power and ground pads strategically at each side of the chip. Ground bounce simulation is done to determine the sufficient pairs of power and ground pads for the chip.

If there are more than one power domain, the power distribution among these power domains is significant in floor-planning and placement phases. The tool synthesizes the power distribution networks of the chip based on the power budget specifications for each domain. The IR drop analysis can be done by using the tool. The purpose for IR analysis is to prevent the supply voltage drops below the designed range. In order to avoid the supply voltage drops below the designed range, the width of the power and ground buses must be designed by sufficient value. Adjustments can be applied to floor-plan and power networks by several iterations until the IR drop constraints are met.

### 3.1.6 Clock Tree Synthesis

The clock tree is synthesized by design synthesis close to an ideal clock for a fully synchronous design. During CTS, the tools will buffer the clock tree networks to a sufficient level of transition like fast rise and fall edges. Meantime, the tool tries to balance the clock branches so that clock skew is under controlled in order to prevent any timing violations. Clock skew control is not so important in clock tree buffers generation.

### 3.1.7 Placement and Routing

The standard cells of the design can be placed into core area by using the tool. The placement can be done either using manual placement or auto placement. For manual placement, the designer places the standard cells into core area by using drag and drop function on the GUI of the tool. In this case, the designer needs to decide the locations of the standard cell to place. Manual is insufficient for large design. It is impractical to place hundreds or thousands of cells into the core area manually. Generally, auto place is more sufficient and practical for large design even for small design. In order to use auto placement, the designer need to include the placement constraints and routing constraints into the tool in order to perform auto placement. The tool will place those standard cells into the core area sufficient based on the constraints. The tool will leave some space for routing based on the constraints. Consequently, the chip area can be optimized by using auto placement. Further optimization for placement can be done to improve routability.

It is impossible to route thousands to millions of nets on the chip. Thus, auto routing is provided by the tool in order to automate the routing process. The tool will find out the best possible ways to route the design by least number of DRC, timing and LVS violations. Those violations can be fixed by re-place the standards cells and re-route the signal and power nets. The re-place and re-route process might be taken in several iterations in order the clean those violations. The following subsection will discuss about the chip finishing.

### 3.1.8 Chip Finishing

Chip finishing is the additional steps required for the chip tape out preparation. The antenna check can be done by the tool based on the antenna rules that provided by foundry. The antenna violations are caused by the longer length of the interconnects with the same metal layers. This will cause damage to the chip due to the collected charges on the particular metal layers during fabrication. Therefore, the antenna

check must be performed before tape out. The antenna fixing can be done by the tool automatically. The tool breaks the long metal lines by inserting by inserting a next higher-level metal layer. Basically, this is known as layer-jumper approach. For top level metal, the protection diodes are added by the tool to fix the violations.

The fill cells are added into the remaining unused area in standard cell rows. The purpose of this process is to meet the continuity of the N-well and P-well and power buses. Additional metals and polys fill layers are added to the un-routed areas in order to establish the density requirements that set by the foundry. IO fill cells are added to the remaining empty space corresponding to the IO cells in order to complete the IO power ring of the chip which can provides ESD protection. Lastly, redundant vias are added wherever there are spaces to prevent the possibility of manufacturing issues. Some vias might become too narrow and might not be functioning properly.

### 3.1.9 Physical Verification

DRC can be performed by the tool to ensure the layout is met the design rule requirements that set by foundry. The DCR violations can be fixed by re-routing the violated nets. Basically, the fixing process can be done manually or automatically. For auto fix, the fixing script needs to be provided to the tool.

LVS is the process of checking the equivalence between the physical layout against the optimized gate-level netlist to ensure the logical descriptions of the design are not changed during the physical implementation process like placement, routing and others.

In the other hand, parasitic extraction is a process of calculating the capacitance, inductance and resistance for parasitic elements in the design. The tool will calculate those parameters by referring to the parasitic library that provided by the foundry.

Lastly, the tool generates the GDSII file that is used for fabrication.

# 3.2 Design Compiler

Synopsys Design Compiler consists of two user interface, known as dc\_shell command line interface and GUI. GUI is used for design purpose with graphical visualization. The dc\_shell command line is used to invoke the command for the compiler to perform specified tasks. Table 3.1 shows the some examples of the command that are used for Design Compiler. Table 3.2 shows the script files that are included into Design Compiler.

There are four main steps to use Synopsys Design Compiler to perform logic synthesis. The four main steps are known as data setup, technology mapping and optimization, design checking and post-synthesis output data. The following subsection will discuss the data setup methodology.

Table 3.1: Examples of Commands Used for Design Compiler

| Commands                          | Description                                  |  |  |

|-----------------------------------|----------------------------------------------|--|--|

| dc_shell –gui                     | Invoke Design Compiler                       |  |  |

| write -f ddc -hier -out           | Save the netlist as ddc format (used for     |  |  |

| mc8051_core.ddc                   | physical design)                             |  |  |

| report_design                     | Report operating condition and wire load     |  |  |

| report_timing                     | Generate timing report for STA               |  |  |

| check_timing                      | Summarize all timing paths                   |  |  |

| compile –scan –boundary –map high | Technology mapping and optimization with     |  |  |

|                                   | high effort                                  |  |  |

| report_constraint -all_violators  | Summarize violated constraints               |  |  |

| source mc8051_core.con            | Applied design constraint script to the      |  |  |

|                                   | compiler                                     |  |  |

| read_ddc mc8051_core.ddc          | Read ddc file into compiler                  |  |  |

| compile_ultra                     | Invoke powerful optimization algorithms      |  |  |

| write_sdc mc8051_core.sdc         | Save the constraints as sdc format for third |  |  |

|                                   | party tool                                   |  |  |

| write_verilog mc8051_core.v       | Save the netlist in Verilog format           |  |  |

| group_path                        | Group the timing path                        |  |  |

Table 3.2: Script Files that are Included into Design Compile

| Scripts            | Description                                                       |

|--------------------|-------------------------------------------------------------------|

| .synopsys_dc.setup | Used for data setup like library setup, search path setup, import |

|                    | design                                                            |

| mc8051_core.con    | Consists of design constrains in tcl command based                |

### 3.2.1 Data Setup

In this stage, all related library like target library, link library and symbol library need to be included into Design Compiler. The design also needs to be imported into Design Compiler. These steps can be done automatically by using a script file. Once the compiler is loaded, the script file is executed automatically by the compiler. All related libraries and search paths are set. The design is imported into compiler.

## 3.2.2 Technology Mapping and Optimization

Before performing mapping and optimization, the design constraints file must be applied to the Design Compiler. The design constraints can be coded into a script file by using tel command format. In order to instruct the compiler to perform mapping and optimization, the command is inserted into de\_shell command line interface. The compiler performs the technology and optimization automatically based on the libraries and design constraints respectively.

### 3.2.3 Design Checking

At this stage, design checking include STA and constraint check. The design checking process can be done by tool automatically. A series of commands is used to generate timing report, constraint report, timing path report and I/O report.

## 3.2.4 Post-synthesis Output Data

The optimized gate-level netlist is saved into several file format like ddc, and verilog format. The constraints are saved into sdc format. The scan chain information is

saved into def format. These all output data are then used for physical design in IC Compiler or third party tools.

# 3.3 IC Compiler

Synopsys IC Compiler consists of two user interface, known as icc\_shell command line interface and GUI. GUI is used for design purpose with graphical visualization. The icc\_shell command line is used to invoke the command for the compiler to perform specified tasks. Table 3.3 shows the examples of the command that are used for IC Compiler. Table 3.4 shows the script files that are included into IC Compiler.

There are six main steps to use Synopsys IC Compiler to perform logic synthesis. The six main steps are known as data setup, floor-planning, placement, CTS, routing and chip finishing. The following subsection will discuss the data setup methodology.

Table 3.3: Examples of Command that Used for IC Compiler

| Commands                     | Description                                          |

|------------------------------|------------------------------------------------------|

| initialize_floorplan         | Initialize floor-plan                                |

| derive_pg_connection         | Make logical P/G pin connection                      |

| create_pad_rings             | Create P/G pad rings                                 |

| set_dont_touch_placement     | Fix the placement (does not change in optimization)  |

| analyse_fp_rail              | Perform IR drop computation                          |

| check_physical_design        | Check the readiness of placement                     |

| check_physical_constraints   | Report the validity of the constraints               |

| place_opt                    | Perform timing-driven and congestion-driven          |

|                              | placement and logic optimization                     |

| create_placement_blockage    | Create placement blockage                            |

| psyopt                       | Performs Incremental logic optimization              |

| set_clock_tree_options       | Set blobal CTS options                               |

| check_clock_tree             | Verification on clock tree                           |

| clock_opt                    | Performs synthesis & balancing of individual clock   |

|                              | tree networks, timing & DRC optimization of non-     |

|                              | clock logic and routing of clock tree network        |

| report_clock_tree            | Analysing CTS result                                 |

| set_fix_hold                 | Enable hold time fixing                              |

| set_delay_calculation -      | Perform net delay calculation by using Arnoldi model |

| arnoldi                      |                                                      |

| set_route_zrt_detail_options | Enable concurrent antenna fixing during signal       |

| -antenna true                | detailed route                                       |

| route_opt                    | Initialize routing                                   |

| report_critical_area         | Analyse critical area                                |

| insert_zrt_redundant_vias    | Insert redundant vias                                |

| insert_metal_filler          | Insert metal fillers                                 |

| write_parasitics             | Parasitic extraction                                 |

| write_stream —cell           | Output netlist in GDSII format                       |

| mc8051_core.gdsii            |                                                      |

| save_mw_cel                  | Save the design cell                                 |

Table 3.4: Script Files that are Included into IC Compiler

| Script              | Description                                                  |

|---------------------|--------------------------------------------------------------|

| .synopsys_dc.setup  | Used for data setup, create design library and import design |

| opt_ctrl.tcl        | Timing and optimization controls                             |

| zic_timing.tcl      | Check zero-interconnect timing constraints                   |

| derive_pg.tcl       | Create logical P/G connections                               |

| ndr.tcl             | Define non-default clock routing rules                       |

| cts_setup.tcl       | Set CTS options                                              |

| antenna .tcl        | Set up antenna rule                                          |

| routing_setting.tcl | Some settings for routing                                    |

## 3.3.1 Data Setup

In data setup, the related libraries need to be included into IC Compiler like logic/timing library, physical library directories, technology file and RC model files. A design CEL need to be created in order to save the design during physical design. In order to perform physical design, the optimized gate-level netlist and design constraints files are imported into the compiler. The all steps can be done by using a series of commands. The all commands can be grouped into a script file known as .synopsys\_dc.setup. Once the tool is started up, the tool will executed the commands that stored in the script file line by line. Those all settings can be done automatically by using the script file.

### 3.3.2 Floor-planning

Floor-planning stage consists of four main steps. These five main steps must be taken in order to complete the design floor-plan. These five main steps are create starting floor-plan, virtual flat placement, analyse/optimize congestion and synthesis power network.

Firstly, the physical-only pad cells are created by the tool. The locations of the cell must be specified. Next, the initial floor-plan are initialized. The core and periphery area are created. The core parameters are defined by specific values. Then, the pad filler cells are inserted and power and ground pad rings are created.

These all steps can be done by using icc\_shell command line, scripts and GUI. The subsequent paragraph will discuss about the virtual flat placement.

There are two steps in virtual flat placement process. The two steps are setting placement strategy parameters and performing virtual placement. These steps can be done by using command lines. The subsequent paragraph will discuss about congestion analysis and optimization.

The congestion is analysed layer by layer. Then, standard cell placement constraints are applied to the compiler by using tcl command. Additional placement constraints can be added like placement blockage constraints. The "fp placement strategy" is modified by using command line. The congestion-driven placement is performed. The high effort congestion strategy is invoked by using script file if the congestion is not acceptable. If the congestion is still not acceptable, the floor-plan must be modified by editing top-level pads or ports, modifying core aspect ratio and size and modifying power grid structure. The subsequent paragraph will discuss about power network synthesis (PNS).

The logical power and ground connections must be defined. Power network constraints are applied before PNS. The constraints are coded into a script file. Then, the tool will perform PNS. If the maximum IR drop is not acceptable, the reconstraint and re-synthesize steps need to be taken. After the IR drop is acceptable,

the new floor-plan is created with added P/G pads. The P/G pins are connected by the tool. The power rails along the standard cell placement rows are created. IR drop map is used to analyse the power network. After that, power net placement blockages are applied and then performs placement legalization. Timing checking is required to check the design in term of timing performance. These all steps can be done by using commands or GUI.

#### 3.3.3 Placement

The placement can be done by referring to IC Compiler placement flow. The flow consists of placement setup & checks, placement & optimization and congestion & timing improvement.

In the placement setup and checks stage, the TLU+ files and timing & optimization controls script are re-applied to the compiler. The placement readiness is checked by using commands.

In the placement and optimization stage, the auto placement is activated by using commands. The tool will perform the placement and optimization based on the constraints.

Timing and congestion are analysed after the placement & optimization. If the timing violations or congestion are occurred, path grouping approach will be used for efficient optimization. After the paths are grouped by the clocks controlling their endpoints, the placement and optimization will be go through again. Basically, these can be done by using tcl commands.

### 3.3.4 Clock Tree Synthesis

CTS goals, timing constraints and timing control scripts are applied to the compiler before CTS is performed. Clock specifications are set and then optimizes the design for power. Basically, these can be done by using command line. The CTS is started by applying command to the tool. The certain analysis can be done by using CTS GUI. The CTS GUI consists of CTS browser, CTS schematic and clock arrival histogram. The timing report is generated in the command line terminal. Finally, the clock nets are routed by the tool.

# 3.3.5 Routing

The routing is performed by using command. The operations include global routing, track assignment, detail routing and concurrent optimization. Concurrent optimizations include timing, power and area optimizations. The concurrent antenna fixing during signal detailed routing is enable. The routing blockages are defined by using script. The redundant via will be inserted into the layout y using default via definitions from the technology file.

### 3.3.6 Chip Finishing

The critical area is reported by using the tool. The minimum jog length is controlled by using command. In order to fix the antenna violations by diode insertion approach, the diode insertion need to be turned on and then run incremental detail route. These can be done by using command. The filler cells in unused placement area are inserted by using script. There are two methods can be used for metal fill insertion that provided by the tool. First method is insert\_metal\_filler by IC Compiler and second method is signoff\_metal\_fill by Hercules based IC Compiler.

In final validation stage, the parasitic calculated can be done by using the compiler. The command is required. Lastly, writing the GDSII output can be done by using command. The tool will automatic write the output in the format of GDSII.

#### **CHAPTER 4**

#### **RESULTS AND DISCUSSIONS**

# 4.1 Logic Synthesis

In the logic synthesis stage, the RTL codes in VHDL format are translated into logic representation format known as the gate-level netlist. The logic optimization and STA are done in order to ensure that the timing, area, power and other constraints are met.

# 4.1.1 Design Compilation and Translation

Before using the Design Compiler, the .synopsys\_dc.setup file (script file) is created in order to automate the library setup, import design, compilation and design translation processes. The contents of the script file are shown in appendices. Once the Design Compiler is started up, the compiler executes the instructions of the script file. Figure 4.1 shows the result of the library setup by using the script file. In this case, the link library is saed90nm\_max.db. The target library is saed90nm\_max.db. The symbol library is saed90nm.sdb. These libraries consist of the details of standard cells, macros, interconnects, technology processes, parasitic, timing and others.

Figure 4.1: Result of Automated Library Setup

After libraries setup, the next part is loading design. By applying the script file, the design is loaded into the compiler automatically. The design is in RTL code format (VHDL). The design is translated and compiled into unmapped and not optimized netlist. Figure 4.2 and Figure 4.3 showed the results of the loading design and translation and compilation respectively. From the results, the loading of the design into Design Compiler is successful. Besides, the compilations of the design such as mc8051\_alu, mc8051\_control, mc8051\_siu, mc8051\_tmrctr, addsub\_core, alumux, alucore, comb\_multiplier, comb\_divider, decimal\_adjustment, control\_mem and control\_fsm are successful. After translation and compilation, the current design is mc8051\_core.

After compilation, the *link* command is used to link the design to the specified libraries in 3 order to tell the compiler to use the specified libraries for the entire design. The standard cells and other information from the libraries are used for the design during design synthesis. Figure 4.4 showed the result from the compiler for the linking process.

Loading vhdl file '/home/student/Desktop/FYP\_updated/synthesis/rtl/mc8051\_core.vhd'Running PRESTO HDLC

Figure 4.2: Result of Loading Design

Presto compilation completed successfully. dc\_shell> Current design is 'mc8051\_core'. Current design is 'mc8051 core'.

Figure 4.3: Results of Compilation

Figure 4.4: Result of Linking Process

Before proceeding to the next stage, libraries checking is a important task. In order to ensure that the used libraries are correct, the *list\_libs* command is used. In this case, the used libraries are corrects. In order to prevent the redesign process, libraries checking process is important. Therefore, libraries checking process is necessary before gate-level optimization and mapping process. Redesigning process is required if the used libraries are wrong. Besides, the libraries checking process also helps the design to ensure that the libraries are applied to the compiler. If no libraries are applied, the compiler will use the built-in libraries. The built-in libraries are not suitable for the design because the libraries do not have any physical design data and eventually cause the physical design cannot be carried out. The designer need to repeat the design synthesis by using suitable libraries for the design. This is vary time consuming. So, it is important to check the libries before logic mapping and optimization. The result of the libraries checking is shown in Figure 4.5. In this case, the applied libraries are saed90nm\_max.db and saed90nm.sdb. The libraries gtech.s5db, gtech.db and standard.sldb are the built-in libraries.

Figure 4.5: Result of the Libraries Checking

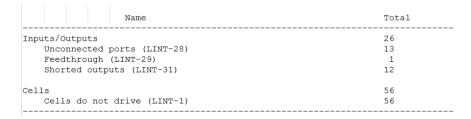

### 4.1.2 Checking Design

Before the mapping and optimization process, the design is checked. The result is shown in Figure 4.6. From the result, there were 26 problems on I/O ports and 56 problems on standard cells. The unconnected port is known as floating port. This is to say that the I/O ports are opened. No signal nets are connected to those particular ports. Some modules like ROM and RAM are removed from the design during RTL stage. The ports that are used to connect the ROM and RAM with the main modules are opened since the ROM and RAM are removed. On the other hand, the amount of feedthrough is 1. Feedthrough is the shorted net within a module or block. The input port of that particular module or block is connected directly to the output port of that particular module or block. It is different compared to the shorted output. Shorted output is the output port of the module or block connected directly to the input port of another module or block by a net. By referring to the RTL source code, the shorted connections can be found. Thus, the problem that causes the shorted connections is the name for both ports are different. The last issue is the cells do not drive any nets. The output ports of the cells are not connected by any nets. This issue also known as floating ports. All these problems can be solved automatically by the tool during mapping and optimization process. The tool will remove the unconnected ports during the mapping and optimization process. Besides, the tool will add buffers to the shorted nets and feedthrough nets during mapping and optimization process. Lastly, the tool will remove the cells that do not drive any nets. The nets that connect the output ports of the modules or blocks to the cells also will be removed by the tool.

Figure 4.6: Design Issue

# 4.1.3 Static Timing Analysis before Mapping and Optimization

The STA result of the design is calculated by the tool. The tool consists of built-in static timing analyser. Static timing analyser is used to guide optimization decisions during mapping and optimization process and generate timing and timing related reports. The tool breaks the design into individual timing paths and the delay of each path is calculated. Then, all path delays are checked against timing constraints to determine if the constraints have been met. The tool analyses each timing path at least twice for single-cycle max-delay timing. The STA result is shown in Figure 4.7. The tool calculates the data arrival time of the design. Data arrival time is the time that the signal arrive at the input pin of the sequential elements like flip-flops. In this case, the data arrival time is about 20198.58 ns. In order to avoid timing violations, the data required time must be greater than 20198.58 ns. Data required time is the sum of the clock period with clock network delay minus the sum of the clock uncertainty with library setup time. For example, the data required time is 20200.00 ns (assume the propagated clock signal is ideal; no clock network delay, library setup time and uncertainty). The frequency of the clock is 1 / 20200 ns = 49.5 kHz. The design only can works on 49.5 kHz or below. The smaller clock frequency causes the low performance of the design. The clock frequency will be improved later on. In this case, the slack is not calculated before the timing constraints are not applied.

```

Operating Conditions: WORST Library: saed90nm max

Wire Load Model Mode: enclosed

Startpoint: reset (input port)

Endpoint: ram en o (output port)

Path Group: (none)

Path Type: max

Des/Clust/Port Wire Load Model

Library

mc8051_core ForQA saed90nm_max control_mem ForQA saed90nm max

Incr

Path

input external delay

reset (in)

i_mc8051_control/reset (mc8051_control)

i_mc8051_control/i_control_mem/reset (control_mem)

i_mc8051_control/i_control_mem/I_333/Z (GTECH_NOT) 20198.55 20198.55 r

i_mc8051_control/i_control_mem/B_244/Z (GTECH_BUF) 0.00 20198.55 r

i mc8051 control/i control mem/ram en o (control mem)

- 0.00 20198.55 r

0.00

i_mc8051_control/ram_en_o (mc8051_control)

20198.55 r

ram en o (out)

0.02

20198.58 r

data arrival time

20198.58

(Path is unconstrained)

```

Figure 4.7: Static Timing Analysis Report before Mapping and Optimization

# 4.1.4 Area of the Design before Mapping and Optimization

Before the mapping and optimization process, the design area is checked. The tool provides the automation in calculating the area of the design. The report that generated by the tool is shown in Figure 4.8. Based on the report, the total area of the design is 104984.540474 µm². The design consists of 156 ports and 367 nets. The total area of the 367 nets is 5369.718050 µm². The design consists of 89 cells (non-combinational cells) and 85 combinational cells. The total area of the cells is the sum of combinational cell area with the non-combinational cell which is 99614.822424 µm² in this case. The macros or black boxes do not exist in the design. Moreover, the design has 85 inverters/buffers. Thus, the total design area is the sum of the cells area with the nets area.

The design is quite large. The area of the design can be reduced during mapping and optimization process with specific design constraints.

```

Library(s) Used:

saed90nm max (File: /home/student/Desktop/FYP updated/synthesis/lib/saed90nm max.db)

Number of ports:

156

Number of nets:

367

Number of cells:

Number of combinational cells:

85

Number of sequential cells:

Number of macros/black boxes:

0

Number of buf/inv.

Number of references:

77138.842108

Combinational area:

Buf/Inv area:

30517.862722

Noncombinational area:

22475.980316

Macro/Black Box area:

0.000000

Net Interconnect area:

5369.718050

Total cell area:

99614.822424

104984.540474

Total area:

```

Figure 4.8: Area of the Design before Mapping and Optimization

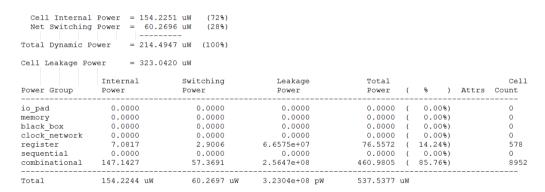

### 4.1.5 Power Analysis before Mapping and Optimization

Power analysis is important for the design. Without power analysis, we do not know how much of the switching power, leakage power and internal power of the design. Every chip must be driven by a power source in order to make it functional. Thus, power analysis is important for the design.