Design and Implementation of a 32-bit Lite Version ARM ISA CPU

By

Tan Beng Liong

#### A REPORT

#### SUBMITTED TO

Universiti Tunku Abdul Rahman

in partial fulfillment of the requirements

for the degree of

BACHELOR OF INFORMATION TECHNOLOGY (HONS)

## COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus)

JAN 2017

# UNIVERSITI TUNKU ABDUL RAHMAN

|                            |                            | ic Session:                                      |

|----------------------------|----------------------------|--------------------------------------------------|

|                            |                            | APITAL LETTER)                                   |

|                            | ation is a property of the |                                                  |

|                            |                            | pies of this dissertation for academic purposes. |

|                            |                            | Verified by,                                     |

| Author's signa             |                            |                                                  |

| Author's signa<br>Address: |                            | Verified by,                                     |

Design and Implementation of a 32-bit Lite Version ARM ISA CPU

By

Tan Beng Liong

#### A REPORT

#### SUBMITTED TO

Universiti Tunku Abdul Rahman

in partial fulfillment of the requirements

for the degree of

BACHELOR OF INFORMATION TECHNOLOGY (HONS)

## COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus)

JAN 2017

# **DECLARATION OF ORIGINALITY**

I declare that this report entitled "Design and Implementation of a 32-bit Lite Version ARM ISA CPU" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other award.

| Signature | : |  |

|-----------|---|--|

|-----------|---|--|

Name : \_\_\_\_\_

Date : \_\_\_\_\_

# **ACKNOWLEDGEMENTS**

I would like to thank to Mr. Mok Kai Ming for giving me the opportunities to contribute in this project which help me improve my understanding toward the processor design skill.

Beside thank to University Tunku Abdul Rahman for provide the facilities and comfortable environment to all students to complete their project.

# ABSTRACT

This project is a processer design with Verilog HDL for academic purpose. The processor is built in pipelined stage and divided to 5 stages which are instruction fetch (IF), instruction decode (ID), instruction execution (EX), memory (MEM) and write back (WB). It contain the methodology, design hierarchy, connection between each blocks and pin description for each blocks. The processor is built based on ARM instruction structure architecture (ISA). To understand the how the instructions work, an ARM assembly stimulator, ARMSim which is free simulator developed by University of Victoria is downloaded, the ARMSim also used to verify the output of the designed Verilog module by comparing the register file and memory content.

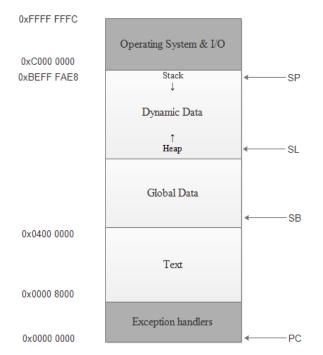

The instruction format and addressing mode of each type of instructions in ARM is studied. The data path of the processor is designed according to the addressing modes of the instructions need to implement to the design. However the arithmetic logic unit (ALU) and barrel shifter block which can perform add, subtract, logical shift (LSL and LSR), arithmetic shift right (ASR) and rotate right (ROR) is designed. For memory cache the address of each segment is refer to the memory map stated in Digital Design and Computer Architecture ARM edition by Sarah L. Harris and David Money Harris. Hazard problem in the pipelined register is solved by implement extra blocks instead of using NOP to achieve a better performance. After designed the Verilog module verification is carry out to make sure the processor work.

The verification is done by using 2 converted ARM assembly program with ARMSim, as stated above the content of both register file and memory cache need to be same. First program used is to test the all instruction implemented worked individually however another is converted from c program to verify that the instructions can worked with each other.

# **TABLE OF CONTENTS**

| Contents                                              |      |

|-------------------------------------------------------|------|

| DECLARATION OF ORIGINALITY                            | I    |

| ACKNOWLEDGEMENTS                                      | 11   |

| ABSTRACT                                              | III  |

| TABLE OF CONTENTS                                     | IV   |

| LIST OF FIGURES                                       | VIII |

| LIST OF TABLES                                        | XI   |

| LIST OF ABBREVIATIONS                                 | XIII |

| Chapter 1 – Introduction                              | 1    |

| 1.1 Project Background                                | 1    |

| 1.2 ARM's History                                     | 1    |

| 1.3 Problem Statement & Motivation                    |      |

| Chapter2 – Literature Review                          | 4    |

| 2.0 ISA (Instruction Set Architecture) of ARM         | 4    |

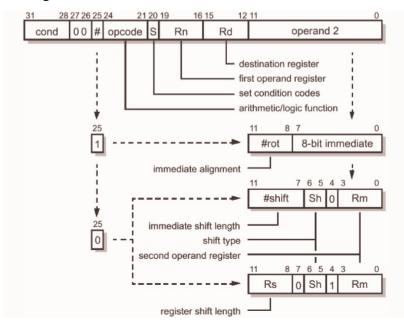

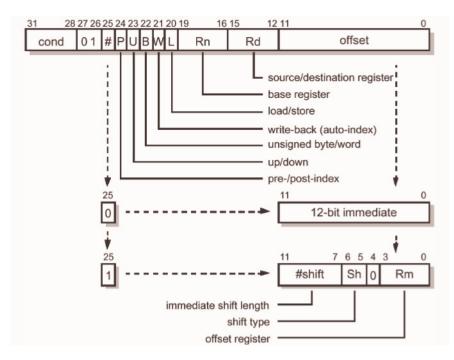

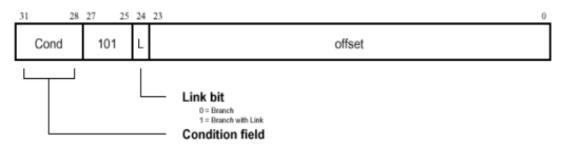

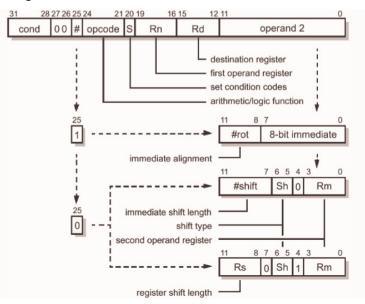

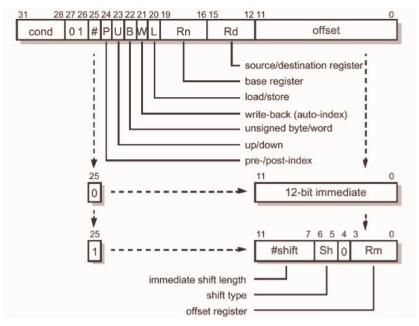

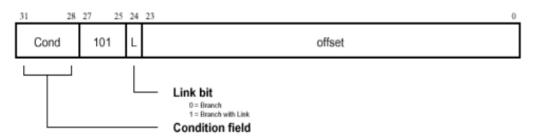

| 2.0.1 Instruction Format                              | 6    |

| 2.0.2 Condition Encode Instruction                    | 8    |

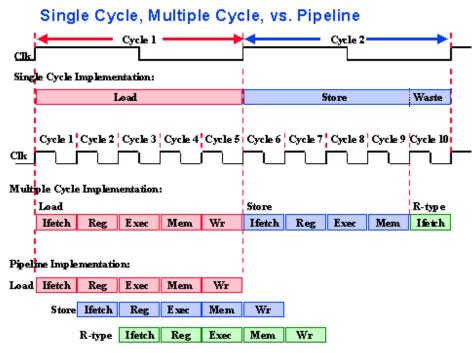

| 2.1 Single cycle, multi-cycle and pipelined processor | 9    |

| 2.2 Benchmarking                                      | 11   |

| 2.2.1 Amber Core                                      | 11   |

| 2.2.2 Storm core                                      | 13   |

| 2.2.3 ARM7 core                                       | 14   |

| 2.2.4 ARM9 core                                       | 15   |

| 2.2.5 ARM10TDMI                                       | 16   |

| 2.2.6 ARM11 Core                                      | 17   |

| Chapter 3 – Project Objective                         | 19   |

| 3.1 Project Scope                                     | 19   |

| 3.2 Objective                                         | 19   |

| 3.3 Significance and Impacts                          | 20   |

| Chapter 4 - Methodology and Technologies Involved     | 21   |

| 4.1 Design Methodology                                |      |

| 4.2 Universal Design Methodology                    |                              |

|-----------------------------------------------------|------------------------------|

| 4.3 Development Tools                               |                              |

| Icarus Verilog                                      |                              |

| 4.4 Design Hierarchy                                |                              |

| 4.5 Implementation Issues and Challenges            |                              |

| 4.6 Schedule and timeline                           |                              |

| Chapter 5 – System Specification                    |                              |

| 5.1 Feature                                         |                              |

| 5.2 Naming Convention                               |                              |

| 5.3 RISC32 processor                                |                              |

| 5.3.1 Processor Interface                           |                              |

| 5.3.2 I/O Pin Description                           |                              |

| 5.4 System Register                                 |                              |

| 5.4.1 General Purpose Register                      |                              |

| 5.4.2 Special Purpose Register                      |                              |

| 5.5 Instruction Format                              |                              |

| 5.6 Addressing Mode                                 |                              |

| 5.7 Instruction Set and Description                 |                              |

| 5.8 Memory Map                                      |                              |

| 5.9 Operating Procedure                             |                              |

| Chapter 6 – Microarchitecture Specification         |                              |

| 6.1 Design hierarchy                                |                              |

| 6.2 Unit level functional partitioning              |                              |

| 6.3 Unit block level partitioning                   | Error! Bookmark not defined. |

| Chapter 7 – Data path of CRISC (Unit & Block level) |                              |

| 7.1 Feature                                         |                              |

| 7.2.1 Block diagram of udp (Data path)              |                              |

| 7.2.2 Data path block level hierarchy               |                              |

| 7.2.3 Block level partition of udp                  | Error! Bookmark not defined. |

| 7.3 Register file (brf)                             |                              |

| 7.3.1 Functionality                                 |                              |

| 7.3.2 Block Diagram                                 |                              |

| 7.3.3 Functional table                              |                              |

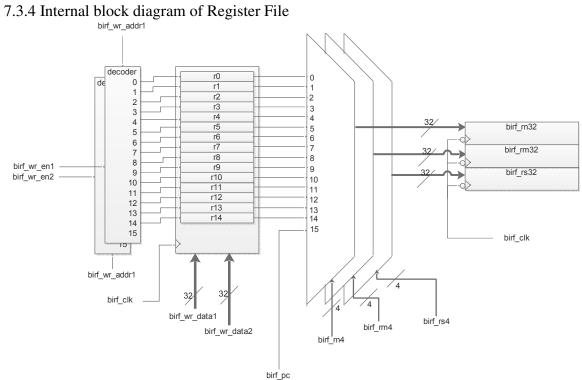

| 7.3.4 Internal block diagram of Register File       | 58                           |

| 7.4 Arithmetic Logic Block with shift (balb_shift)     |                              |

|--------------------------------------------------------|------------------------------|

| 7.4.1 Functionality                                    |                              |

| 7.4.2 Block Diagram                                    |                              |

| 7.4.3 Functional table                                 | Error! Bookmark not defined. |

| 7.4.4 Internal block diagram of ALB                    | Error! Bookmark not defined. |

| 7.4.5 Test plan                                        |                              |

| 7.4.6 Simulation result                                |                              |

| 7.5 Data forwarding control (bfw_ctrl)                 |                              |

| 7.5.1 Functionality                                    |                              |

| 7.5.2 Forwarding Block Function Tables                 |                              |

| 7.5.3 Block diagram                                    |                              |

| 7.6 Interlock control (bitl_ctrl)                      |                              |

| 7.6.1 Functionality                                    |                              |

| 7.6.2 Block diagram                                    |                              |

| 7.6.3 Functional table                                 | 77                           |

| Chapter 8 – Control Path of CRISC (Unit & Block level) |                              |

| 8.1 Control Path unit (ucp)                            |                              |

| 8.1.1 Functionality                                    |                              |

| 8.1.2 Control Path's Unit interface – (Block diagram)  |                              |

| 8.1.3 Block partitioning in ucp                        |                              |

| 8.1.4 Block level partition diagram                    |                              |

| 8.1.5 Functional table                                 | Error! Bookmark not defined. |

| 8.2 Main Control Block (bmain_ctrl)                    |                              |

| 8.2.1 Functionality                                    |                              |

| 8.2.2 Block diagram                                    |                              |

| 8.2.3 Functional table                                 | Error! Bookmark not defined. |

| 8.3 Instruction Control Block (binstr_ctrl)            |                              |

| 8.3.1 Functionality                                    |                              |

| 8.3.2 Block diagram                                    |                              |

| 8.3.3 Functional table                                 | Error! Bookmark not defined. |

| Chapter 9 – Memory Cache unit (ucache)                 |                              |

| 9.1 Functionality                                      | 05                           |

| •                                                      |                              |

| Chapter 10 – UART unit                              | 97 |

|-----------------------------------------------------|----|

| 10.1 UART address                                   | 97 |

| 10.2 Operating procedure                            | 97 |

| 10.3 uuart functionalities and pin description      | 99 |

| 10.4 bclkctr functionalities and pins description10 | 03 |

| 10.5 brx functionalities and pins description       | 05 |

| 10.6 btx functionalities and pins description10     | 08 |

| 10.7 UART address decoder                           | 11 |

| Chapter 11 – Verification Specification 12          | 12 |

| 11.1 Verification for crisc                         | 12 |

| 11.2 Test Program for RISC 32                       | 13 |

| 11.2.1 Test program 1 12                            | 14 |

| 11.2.2 Verification for test program 1 for RISC3212 | 17 |

| 11.2.3 Test program 2 12                            | 21 |

| 11.2.4 Verification on test program 2               | 23 |

| 11.3 Verification on UART and core interaction      | 24 |

| Chapter 12 – Conclusion                             | 25 |

| References12                                        | 26 |

| Appendix12                                          | 27 |

# LIST OF FIGURES

|               | LIST OF FIGURES                                                 | _    |

|---------------|-----------------------------------------------------------------|------|

| Figure Number | Title                                                           | Page |

| Figure 2.1    | Data-processing instruction format                              | 5    |

| Figure 2.2    | Memory instruction format                                       | 6    |

| Figure 2.3    | Branch instruction format                                       | 6    |

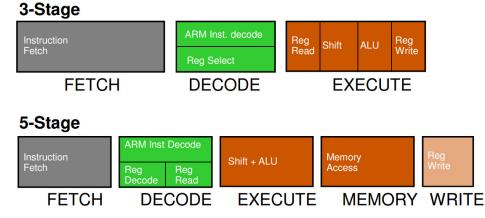

| Figure 2.4    | Single cycle, multicycle vs pipeline processor                  | 9    |

| Figure 2.5    | 3-Stages and 5-Stages pipeline                                  | 10   |

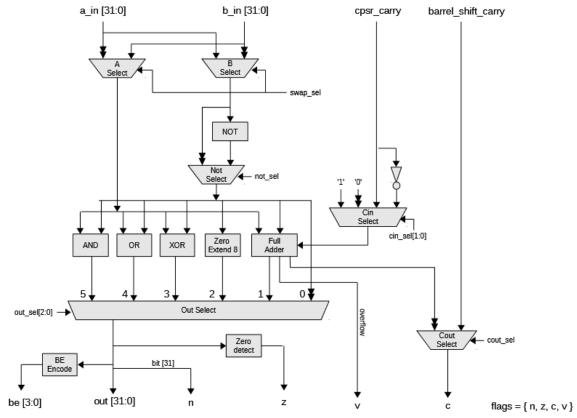

| Figure 2.6    | Design of ALU in Amber 23                                       | 11   |

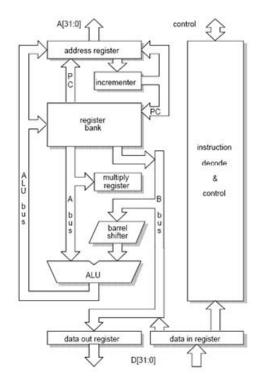

| Figure 2.7    | Data path of ARM7                                               | 14   |

| Figure 2.8    | Data path of ARM9                                               | 15   |

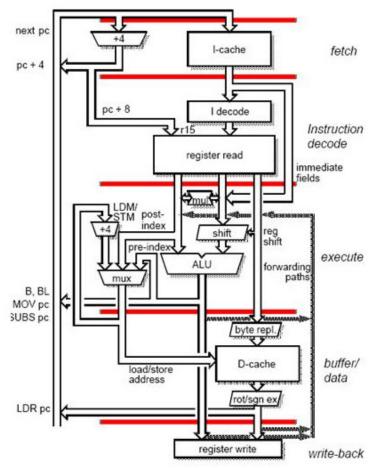

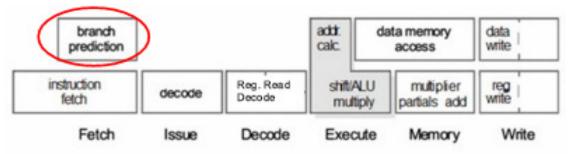

| Figure 2.9    | Pipelined stage of ARM10DTMI                                    | 16   |

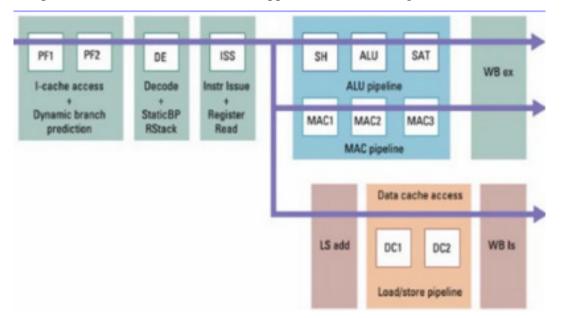

| Figure 2.10   | Pipelined stage of ARM11                                        | 17   |

| Figure 2.11   | Grouped pipelined stage of ARM 11                               | 17   |

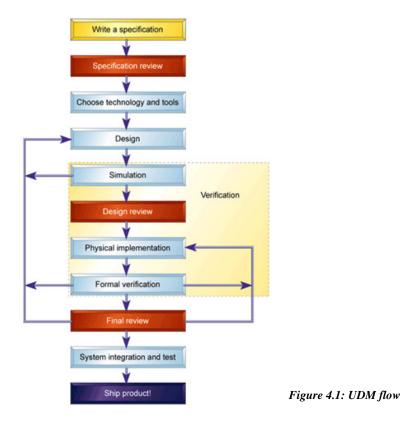

| Figure 4.1    | UDM flow                                                        | 21   |

| Figure 4.2    | Pipeline stage of instruction in different cycle(1)             | 25   |

| Figure 4.3    | Pipeline stage of instruction in different cycle(2)             | 25   |

| Figure 4.4    | Pipeline stage of instruction in different cycle(3)             | 25   |

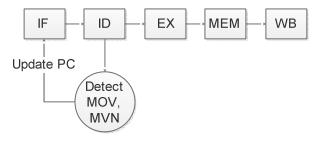

| Figure 4.5    | MOV and MVN detector                                            | 26   |

| Figure 4.6    | ALU to be design and implement                                  | 27   |

| Figure 5.1    | Block diagram for RISC32 processor                              | 31   |

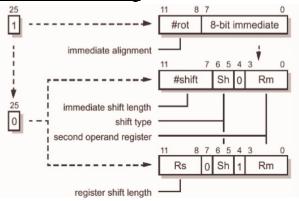

| Figure 5.2    | Data-processing instruction format                              | 33   |

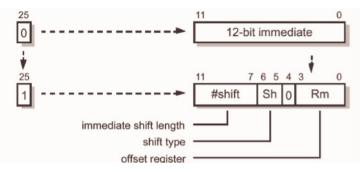

| Figure 5.3    | Memory instruction format                                       | 33   |

| Figure 5.4    | Branch instruction format                                       | 34   |

| Figure 5.5    | Immediate addressing                                            | 36   |

| Figure 5.6.1  | Register addressing (1)                                         | 37   |

| Figure 5.6.2  | Register addressing (2)                                         | 37   |

| Figure 5.7    | Base addressing                                                 | 37   |

| Figure 5.8    | Register indexed displacement addressing with register scaling  | 38   |

| Figure 5.9    | Register indexed displacement addressing with immediate scaling | 38   |

| Figure 5.10   | Pseudodirect addressing                                         | 39   |

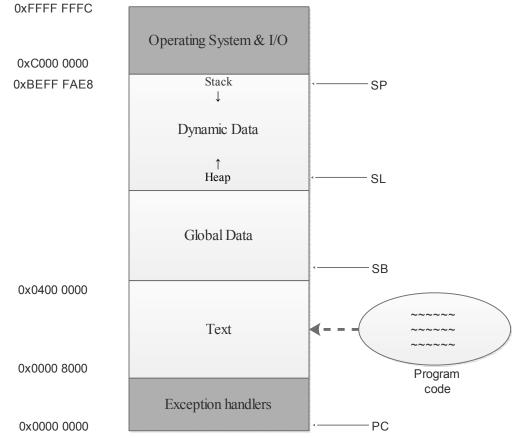

| Figure 5.11   | Memory map                                                      | 44   |

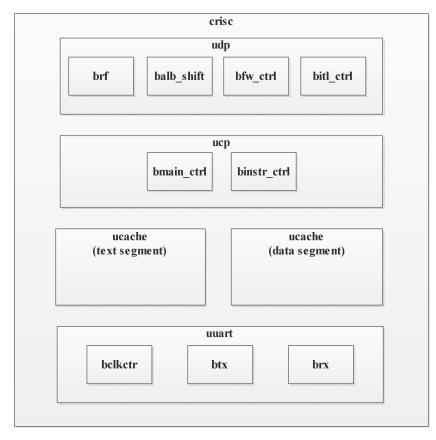

| Figure 6.1    | crisc architecture and micro-architecture partitioning          | 46   |

| Figure 6.2    | Unit level functional partition                                 | 47   |

| Figure 6.3    | Unit block level functional partition                           | 48   |

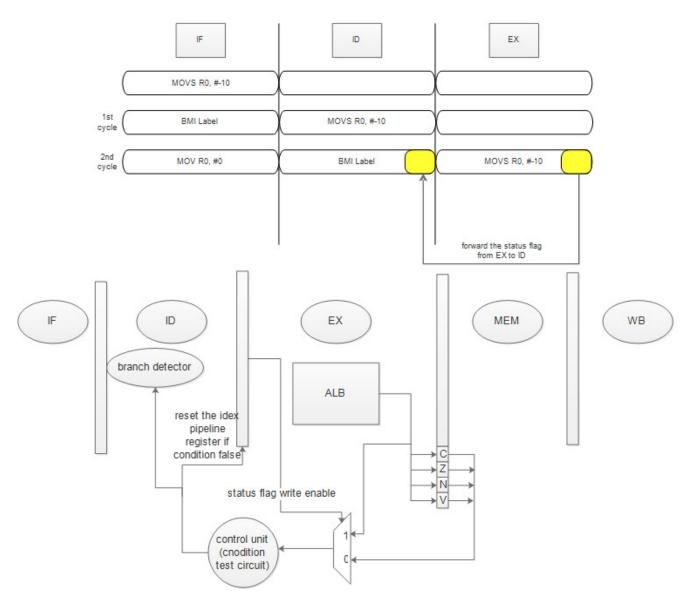

| Figure 7.1    | Solution for status flag problem                                | 50   |

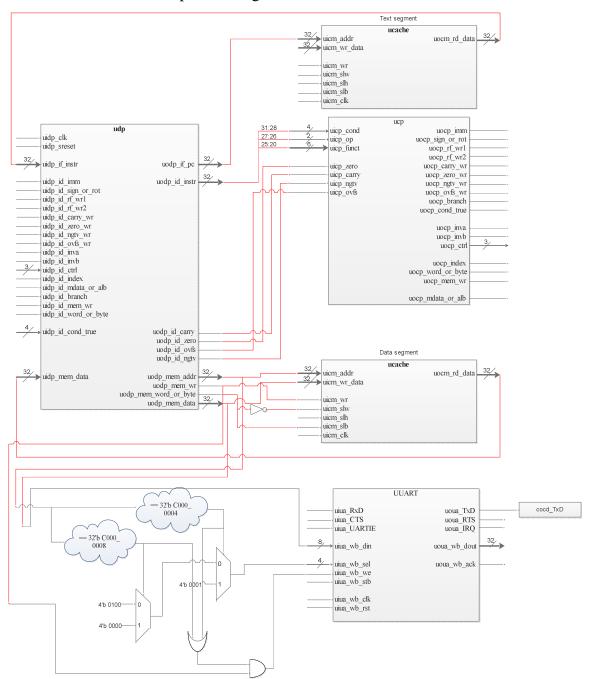

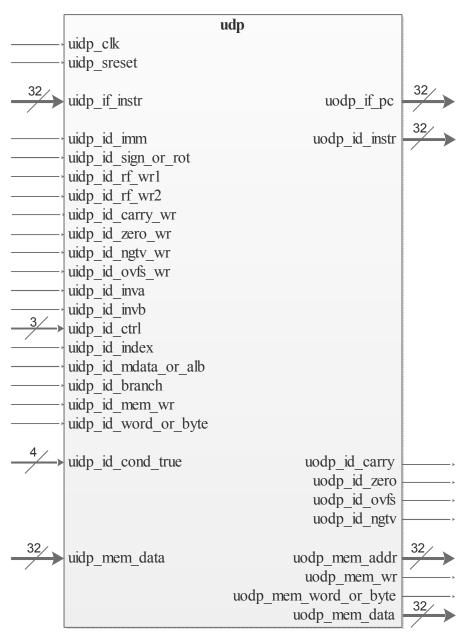

| Figure 7.2    | Block diagram of data path                                      | 51   |

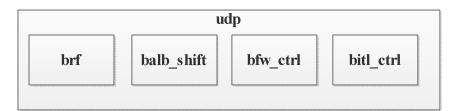

| Figure 7.3    | Partition of data path unit                                     | 57   |

| Figure 7.4                                                                                                                                                                                                                                                                    | Connection between block in data path unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

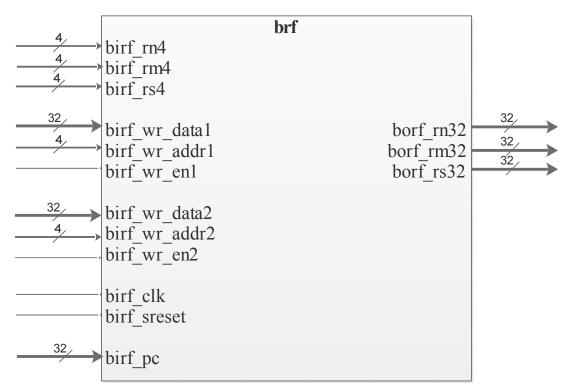

| Figure 7.5                                                                                                                                                                                                                                                                    | Block diagram of brf (register file)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59                                                                                                                                                                                                                         |

| Figure 7.6                                                                                                                                                                                                                                                                    | Design of register file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                                                                                                                         |

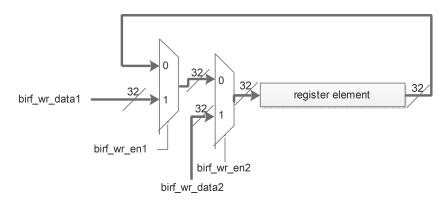

| Figure 7.7                                                                                                                                                                                                                                                                    | Single element of register file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                                                                                                                                                                         |

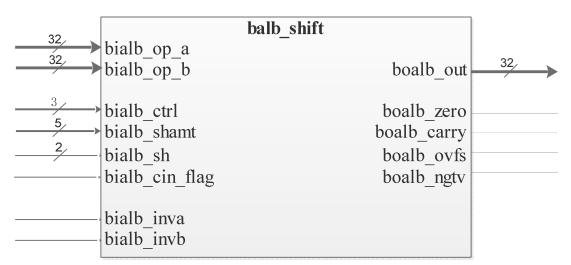

| Figure 7.8                                                                                                                                                                                                                                                                    | Block diagram of balb_shift (ALU and shifter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64                                                                                                                                                                                                                         |

| Figure 7.9                                                                                                                                                                                                                                                                    | Design of ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                                                                                                                                                         |

| Figure 7.10                                                                                                                                                                                                                                                                   | Design of barrel shifter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69                                                                                                                                                                                                                         |

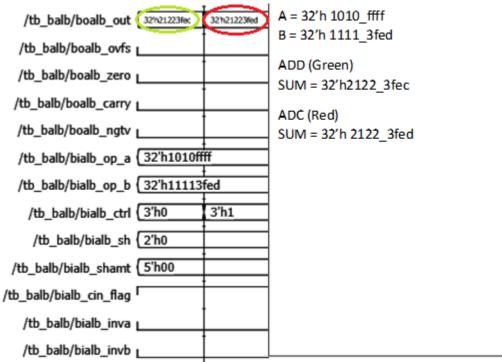

| Figure 7.11                                                                                                                                                                                                                                                                   | Simulation result (1) – addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72                                                                                                                                                                                                                         |

| Figure 7.12                                                                                                                                                                                                                                                                   | Simulation result $(2)$ - subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72                                                                                                                                                                                                                         |

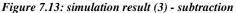

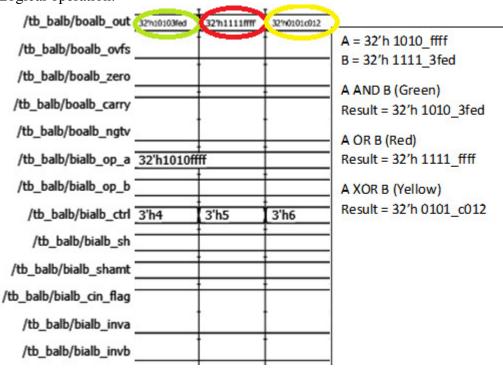

| Figure 7.13                                                                                                                                                                                                                                                                   | Simulation result $(3)$ – subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73                                                                                                                                                                                                                         |

| Figure 7.14                                                                                                                                                                                                                                                                   | Simulation result $(4) - \log i cal$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                                                                                                                                                         |

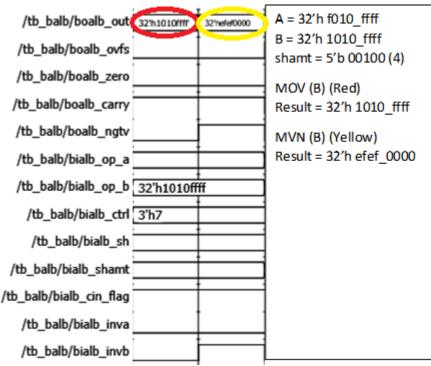

| Figure 7.15                                                                                                                                                                                                                                                                   | Simulation result $(5) - \text{shift/ rotate}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74                                                                                                                                                                                                                         |

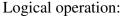

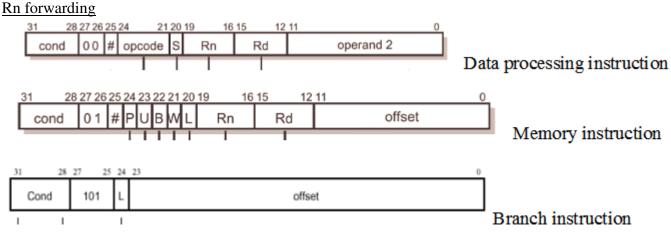

| Figure 7.16                                                                                                                                                                                                                                                                   | Instruction format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                                                                                                                                                         |

| Figure 7.17                                                                                                                                                                                                                                                                   | Data processing instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75                                                                                                                                                                                                                         |

| Figure 7.18                                                                                                                                                                                                                                                                   | Memory instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76                                                                                                                                                                                                                         |

| Figure 7.19                                                                                                                                                                                                                                                                   | Block diagram of bfw_ctrl (forwarding control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                                                                                                                                         |

| Figure 7.20                                                                                                                                                                                                                                                                   | Block diagram of bitl_ctrl (interlock control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83                                                                                                                                                                                                                         |

| 1 15ule 7.20                                                                                                                                                                                                                                                                  | block diagram of ont_out (merioek control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 05                                                                                                                                                                                                                         |

| Figure 8.1                                                                                                                                                                                                                                                                    | Block diagram of control path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                                                                                                                                                                                                                         |

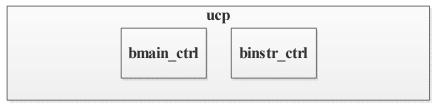

| Figure 8.2                                                                                                                                                                                                                                                                    | Partitioning in ucp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91                                                                                                                                                                                                                         |

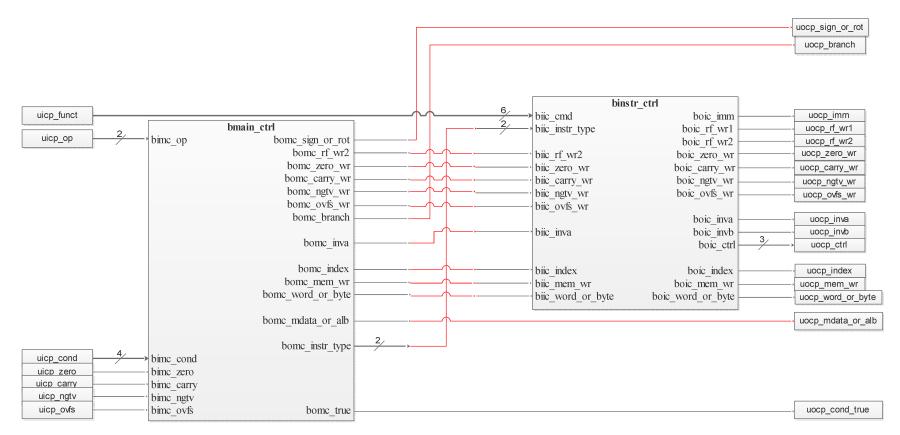

| Figure 8.3                                                                                                                                                                                                                                                                    | Internal connection between block in ucp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92                                                                                                                                                                                                                         |

| Figure 8.4                                                                                                                                                                                                                                                                    | Block diagram of main control block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 96                                                                                                                                                                                                                         |

| Figure 8.5                                                                                                                                                                                                                                                                    | Block diagram of binstr_ctrl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 103                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                            |

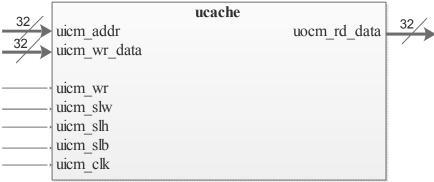

| Figure 9.1                                                                                                                                                                                                                                                                    | Block diagram of ucache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 110                                                                                                                                                                                                                        |

| -                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                            |

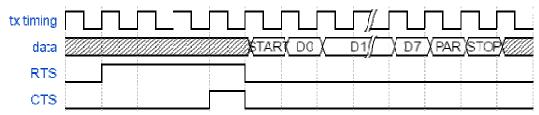

| Figure 10.1                                                                                                                                                                                                                                                                   | Transmission of data by UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 112                                                                                                                                                                                                                        |

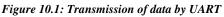

| Figure 10.1<br>Figure 10.2                                                                                                                                                                                                                                                    | Transmission of data by UART<br>UART data transfer protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112<br>113                                                                                                                                                                                                                 |

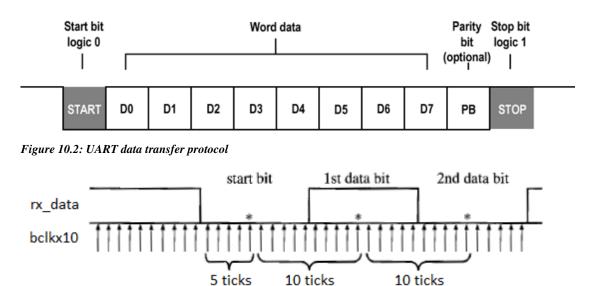

| Figure 10.1<br>Figure 10.2<br>Figure 10.3                                                                                                                                                                                                                                     | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 112<br>113<br>113                                                                                                                                                                                                          |

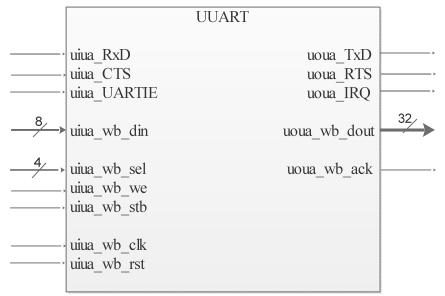

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4                                                                                                                                                                                                                      | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart                                                                                                                                                                                                                                                                                                                                                                                                                        | 112<br>113<br>113<br>114                                                                                                                                                                                                   |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5                                                                                                                                                                                                       | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart                                                                                                                                                                                                                                                                                                                                                                                        | 112<br>113<br>113<br>114<br>118                                                                                                                                                                                            |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6                                                                                                                                                                                        | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr                                                                                                                                                                                                                                                                                                                                                            | 112<br>113<br>113<br>114<br>118<br>119                                                                                                                                                                                     |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7                                                                                                                                                                         | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr                                                                                                                                                                                                                                                                                                                          | 112<br>113<br>113<br>114<br>118<br>119<br>121                                                                                                                                                                              |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8                                                                                                                                                          | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx                                                                                                                                                                                                                                                                                                  | 112<br>113<br>113<br>114<br>118<br>119<br>121<br>122                                                                                                                                                                       |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9                                                                                                                                           | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller                                                                                                                                                                                                                                                              | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> </ul>                                                                                            |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10                                                                                                                           | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx                                                                                                                                                                                                                                      | 112<br>113<br>113<br>114<br>118<br>119<br>121<br>122<br>124<br>125                                                                                                                                                         |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11                                                                                                           | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller                                                                                                                                                                                                  | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> </ul>                                                                  |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10                                                                                                                           | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx                                                                                                                                                                                                                                      | 112<br>113<br>113<br>114<br>118<br>119<br>121<br>122<br>124<br>125                                                                                                                                                         |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11                                                                                                           | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller                                                                                                                                                                                                  | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> </ul>                                                                  |

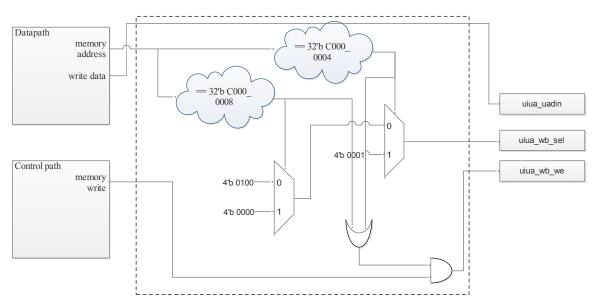

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11<br>Figure 10.12                                                                                           | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller<br>Circuit for CPU-UART address decoder                                                                                                                                                          | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> <li>128</li> </ul>                                                     |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11<br>Figure 10.12                                                                            | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller<br>Circuit for CPU-UART address decoder<br>Memory map & program code segment                                                                                                                     | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> <li>128</li> <li>129</li> </ul>                                        |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11<br>Figure 10.12<br>Figure 11.1<br>Figure 11.2                                              | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller<br>Circuit for CPU-UART address decoder<br>Memory map & program code segment<br>Test program 1 result (1)                                                                                        | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> <li>128</li> <li>129</li> <li>134</li> </ul>                           |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11<br>Figure 10.12<br>Figure 11.1<br>Figure 11.2<br>Figure 11.3                                              | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller<br>Circuit for CPU-UART address decoder<br>Memory map & program code segment<br>Test program 1 result (1)<br>Test program 1 result (2)                                                           | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> <li>128</li> <li>129</li> <li>134</li> <li>134</li> </ul>              |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.11<br>Figure 10.12<br>Figure 11.1<br>Figure 11.2<br>Figure 11.3<br>Figure 11.4                               | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller<br>Circuit for CPU-UART address decoder<br>Memory map & program code segment<br>Test program 1 result (1)<br>Test program 1 result (2)<br>Test program 1 result (3)<br>Test program 1 result (4) | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> <li>128</li> <li>129</li> <li>134</li> <li>134</li> <li>135</li> </ul> |

| Figure 10.1<br>Figure 10.2<br>Figure 10.3<br>Figure 10.4<br>Figure 10.5<br>Figure 10.6<br>Figure 10.7<br>Figure 10.7<br>Figure 10.8<br>Figure 10.9<br>Figure 10.10<br>Figure 10.10<br>Figure 10.12<br>Figure 11.1<br>Figure 11.2<br>Figure 11.3<br>Figure 11.4<br>Figure 11.5 | Transmission of data by UART<br>UART data transfer protocol<br>UART data receiving protocol<br>Block diagram of uuart<br>Internal connection of uuart<br>Block diagram of bclkctr<br>Internal connection of bclkctr<br>Block diagram of brx<br>State diagram for brx controller<br>Block diagram of btx<br>State diagram for btx controller<br>Circuit for CPU-UART address decoder<br>Memory map & program code segment<br>Test program 1 result (1)<br>Test program 1 result (2)<br>Test program 1 result (3)                              | <ul> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>118</li> <li>119</li> <li>121</li> <li>122</li> <li>124</li> <li>125</li> <li>127</li> <li>128</li> <li>129</li> <li>134</li> <li>135</li> <li>135</li> </ul> |

| Figure 11.8  | Test program 1 result (7)                 | 136 |

|--------------|-------------------------------------------|-----|

| Figure 11.9  | Test program 1 result (8)                 | 136 |

| Figure 11.10 | Test program 1 result (9)                 | 136 |

| Figure 11.11 | Test program 1 result (10)                | 137 |

| Figure 11.12 | Test program 2 result (1) – factorial (5) | 140 |

| Figure 11.13 | Test program 2 result (2) – factorial (4) | 140 |

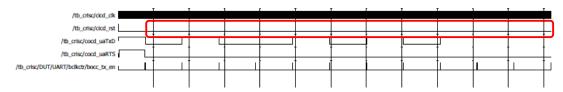

| Figure 11.14 | Waveform result(1)                        | 141 |

| Figure 11.15 | Waveform result(2)                        | 141 |

| Figure 11.16 | Transmitter FIFO content                  | 141 |

# LIST OF TABLES

| Table Number | Title                                           | Page |

|--------------|-------------------------------------------------|------|

| Table 1.1    | List of ARM microarchitectures                  | 2    |

|              |                                                 |      |

| Table 2.1    | Instruction set of ARM                          | 4    |

| Table 2.2    | Condition encoding                              | 8    |

| Table 2.3    | Pin description of Amber's ALU                  | 12   |

| Table 2.4    | Comparison among Amber 23, Amber 25 and         | 13   |

|              | Strom core                                      |      |

| Table 2.5    | Comparison among ARM 7, ARM 9, ARM 10 &         | 18   |

|              | ARM11                                           |      |

| Table 4.1    | Comparison among Development Tools              | 23   |

| Table 4.2    | Pin description for ALU to be design            | 27   |

| Table 4.3    | Gantt Chart for project 1 & 2                   | 28   |

|              |                                                 |      |

| Table 5.1    | RISC32 features                                 | 29   |

| Table 5.2    | Naming convention                               | 30   |

| Table 5.3    | RISC32 Input pins description                   | 31   |

| Table 5.4    | RISC32 Output pins description                  | 31   |

| Table 5.5    | Register file                                   | 32   |

| Table 5.6    | Status flag register                            | 32   |

| Table 5.7    | Encoded immediate value                         | 35   |

| Table 5.8    | Data-processing instruction set and description | 40   |

| Table 5.9    | Operand 2 for data processing instruction       | 41   |

| Table 5.10   | Memory instruction set and description          | 41   |

| Table 5.11   | Source 2 for memory instruction                 | 43   |

| Table 5.12   | Branch instruction set and description          | 43   |

| Table 5.13   | Condition encoding                              | 44   |

| Table 6.1    | Formation of a design hierarchy for crisc       | 46   |

|              | microprocessor through top down design          | 10   |

|              | meroprocessor unough top down design            |      |

| Table 7.1    | Status flag problem                             | 50   |

| Table 7.2    | Input pins description for data path unit       | 51   |

| Table 7.3    | Output pins description for data path unit      | 55   |

| Table 7.4    | General register                                | 59   |

| Table 7.5    | Input pins description of brf                   | 60   |

| Table 7.6    | Output pins description of brf                  | 61   |

| Table 7.7    | Functional table for write enable signal        | 62   |

| Table 7.8    | Functional table for address pin                | 62   |

| Table 7.9    | Input pins description of balb_shift            | 64   |

| Table 7.10   | Output pins description of balb_shift           | 66   |

| Table 7.11   | Functional table for ALU                        | 67   |

| Table 7.12   | Functional table for barrel shifter             | 67   |

| Table 7.13<br>Table 7.14 | Test plan for balb_shift<br>ARM assembly instruction            | 70<br>77 |

|--------------------------|-----------------------------------------------------------------|----------|

| Table 7.15               | Functional table for forwarding block                           | 79       |

| Table 7.16               | Input pins description of bfw_ctrl                              | 80       |

| Table 7.17               | Output pins description of bfw_ctrl                             | 82       |

| Table 7.18               | Input pins description of bitl_ctrl                             | 83       |

| Table 7.19               | Output pins description of butl_ctrl                            | 84       |

| Table 7.20               | Functional table of bitl_ctrl                                   | 85       |

| Table 8.1                | Input pins description of ucp                                   | 86       |

| Table 8.2                | Output pins description of ucp                                  | 88       |

| Table 8.3                | Functional table for ucp (data-processing instruction)          | 93       |

| Table 8.4                | Functional table for ucp (memory instruction)                   | 94       |

| Table 8.5                | Functional table for ucp (program flow instruction)             | 94       |

| Table 8.6                | Relationship between condition mask and status flag             | 95       |

| Table 8.7                | Input pin description of main control block                     | 96       |

| Table 8.8                | Output pin description of main control block                    | 98       |

| Table 8.9                | Status flag for each condition mask                             | 101      |

| Table 8.10               | Functional table for bmain_ctrl                                 | 102      |

| Table 8.11               | Input pins description of binstr_ctrl                           | 103      |

| Table 8.12               | Output pins description of binstr_ctrl                          | 105      |

| Table 8.13               | Functional table of binstr_ctrl (Data-processing instruction)   | 108      |

| Table 8.14               | Functional table of binstr_ctrl (Memory instruction)            | 109      |

| Table 8.15               | Functional table of binstr_ctrl (Program flow                   | 109      |

|                          | instruction)                                                    |          |

| Table 9.1                | Input pins description of ucache                                | 110      |

| Table 9.2                | Output pins description of ucache                               | 111      |

| Table 10.1               | Address for UART register and FIFO                              | 112      |

| Table 10.2               | Input pins description for uuart                                | 114      |

| Table 10.3               | Output pins description for uuart                               | 116      |

| Table 10.4               | Input pins description for bclkctr                              | 119      |

| Table 10.5               | Output pins description for bclkctr                             | 120      |

| Table 10.6               | Input pins description for brx                                  | 122      |

| Table 10.7               | Output pins description for brx                                 | 123      |

| Table 10.8               | Input pins description for btx                                  | 125      |

| Table 10.9               | Output pins description for btx                                 | 127      |

| Table 11.1               | Test program 1 (without data dependency, interlock and hazard.) | 131      |

| Table 11.2               | Test program 2 with data dependency, interlock and hazard       | 138      |

# LIST OF ABBREVIATIONS

| RISC | Reduced instruction set computing            |

|------|----------------------------------------------|

| CISC | Complex instruction set computing            |

| GUI  | Graphic based user interface                 |

| ISA  | Instruction set architecture                 |

| IP   | Intellectual property                        |

| GPIO | General purpose input/output                 |

| IF   | Instruction fetch (pipeline stage)           |

| ID   | Instruction decode (pipeline stage)          |

| EX   | Execute (pipeline stage)                     |

| MEM  | Memory (pipeline stage)                      |

| WB   | Write back (pipeline stage)                  |

| ALU  | Arithmetic logic unit                        |

| RTL  | Register transfer level                      |

| I/O  | Input / output                               |

| PC   | Program counter                              |

| UART | Universal asynchronous receiver/ transmitter |

|      |                                              |

# Chapter 1 – Introduction

## 1.1 Project Background

ARM is a computer processors developer company with reduced instruction set computing (RISC) architectures. A RISC-based processor requires lesser transistors than CISC (complex instruction set computing) processor such as x86 processors in most of personal computer. This means reduces in cost, heat produced and power use can be achieving which is importance factor for light, portable and battery-powered devices such as smartphone, laptops, tablet and embedded systems. Most of the cores introduced by ARM support a 32-bits address space except ARMv8-A architectures support 64-bits. ARM licenses their design to companies that incorporate those core designs into their own products.

#### 1.2 ARM's History

ARM is a British company start at 1980 with the name of Acorn Computer at first. Its first product was a coprocessor module for BBC Micro series of computers. Then they start relatively simple MOS Technology 6502 processor in1981. But the 6502 processor is not strong enough for GUI (graphics based user interface), so ARM decides to design their own processor after studies all the lacking of existing processors. Sophie Wilson developed the instruction set and in 1983, the official Acorn RISC Machine with cooperation with VSLI Technology as silicon partner. Then the ARM2 was introduced which enable lower power consumption, but better performance than Intel 80286. And ARM continue introduce ARM3 and ARM6. ARM 3 had better performance than ARM2. But ARM 6, result of cooperation between Apple and ARM manage to remained essentially same size with ARM2 with further better performance; ARM2 had 30,000 transistors, while ARM6 had 35,000.

| 32       32       32       32       32       32 | ARM1<br>ARM2, ARM250, ARM3<br>ARM6, ARM7<br>ARM8                                                                                                                                                                                                     |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32                                              | ARM6, ARM7                                                                                                                                                                                                                                           |

| -                                               | ,                                                                                                                                                                                                                                                    |

| 32                                              | ARM8                                                                                                                                                                                                                                                 |

|                                                 |                                                                                                                                                                                                                                                      |

| 32                                              | ARM7TDMI, ARM9TDMI, SecurCore SC100                                                                                                                                                                                                                  |

| 32                                              | ARM7EJ, ARM9E, ARM10E                                                                                                                                                                                                                                |

| 32                                              | ARM11                                                                                                                                                                                                                                                |

| 32                                              | ARM Cortex-M0, ARM Cortex-M0+, ARM Cortex-<br>M1, SecurCore SC000                                                                                                                                                                                    |