# THE DEVELOPMENT OF AN EXCEPTION SCHEME FOR 5-STAGE PIPELINE RISC PROCESSOR

BY

Goh Jia Sheng

# A REPORT

# SUBMITTED TO

Universiti Tunku Abdul Rahman

in partial fulfilment of the requirements

for the degree of

BACHELOR OF INFORMATION TECHNOLOGY (HONS)

COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus)

JAN 2019

# UNIVERSITI TUNKU ABDUL RAHMAN

| Title:                           |                                                                                 |

|----------------------------------|---------------------------------------------------------------------------------|

| Title:                           |                                                                                 |

| 1 itle:                          |                                                                                 |

|                                  |                                                                                 |

|                                  |                                                                                 |

|                                  | Academic Session:                                                               |

| I                                |                                                                                 |

|                                  | (CAPITAL LETTER)                                                                |

| declare that I allow thi         | is Final Year Project Report to be kept in                                      |

|                                  | ul Rahman Library subject to the regulations as follows:                        |

|                                  | s a property of the Library.                                                    |

|                                  |                                                                                 |

| 2                                | owed to make copies of this dissertation for academic purposes.                 |

| 5                                | owed to make copies of this dissertation for academic purposes.                 |

| ý                                | owed to make copies of this dissertation for academic purposes.                 |

| ,<br>,                           | owed to make copies of this dissertation for academic purposes.                 |

|                                  |                                                                                 |

| 5                                | owed to make copies of this dissertation for academic purposes.<br>Verified by, |

|                                  |                                                                                 |

|                                  |                                                                                 |

| (Author's signature)             |                                                                                 |

| (Author's signature)             | Verified by,                                                                    |

|                                  | Verified by,<br>(Supervisor's signature)                                        |

| (Author's signature)<br>Address: | Verified by,<br>(Supervisor's signature)                                        |

| (Author's signature)<br>Address: | Verified by,<br>(Supervisor's signature)                                        |

# THE DEVELOPMENT OF AN EXCEPTION SCHEME FOR 5-STAGE PIPELINE RISC PROCESSOR

BY

Goh Jia Sheng

# A REPORT

# SUBMITTED TO

Universiti Tunku Abdul Rahman

in partial fulfilment of the requirements

for the degree of

# BACHELOR OF INFORMATION TECHNOLOGY (HONS)

# COMPUTER ENGINEERING

Faculty of Information and Communication Technology (Perak Campus)

JAN 2019

# **DECLARATION OF ORIGINALITY**

I declare that this report entitled "THE DEVELOPMENT OF AN EXCEPTION SCHEME FOR 5-STAGE PIPELINE RISC PROCESSOR" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other award.

| Signature | : |  |

|-----------|---|--|

| Name      | : |  |

|           |   |  |

| Date      | : |  |

# **ACKNOWLEDGEMENTS**

I would like give my deepest appreciation to my project supervisor, Mr. Mok Kai Ming for providing me an opportunity to involve in the Computer Architecture development. Thank you for your patience and invaluable guidance and suggestion throughout this project.

Next, I would like to thanks my family members for giving me endless support and encouragement throughout my undergraduate study. Furthermore, I would like to thanks my course mates and friends who has supported me throughout the entire project.

Finally, I appreciate all the guidance and support that provided by people that I mentioned above. All the supports and helps have contributed to the accomplishment of this project.

# ABSTRACT

Exception classified into two types, which are the internal exception and external exception. Normally, we called internal exception as trap and External exception as interrupt. Exception makes the 5-stage pipeline processor more complicated because the exception is difficult to handle in pipeline processor due the overlapping instruction characteristics. The exception will cause abnormal program flow, and when exception occur, we need to provide some operation to overcome the problem. The IoT SoC processor will used for this project purpose. Up-to-date, the processor has a few I/O modules integrated namely the UART, GPIO and SPI. It also has a co-processor and programmable interrupt controller to handle the exceptions. The handling of the exceptions was half-planned, however, not up to a high confidence level. Therefore, this project is initiated to develop an exception handling scheme to handle the multiple interrupt (including nested interrupts) occurrence. Interrupt can occur at any time, and the timing to capture the data is critical. For example, when the UART and SPI received the data at the same time, both module will raise the interrupt flag concurrently. Therefore, we need a plan to schedule which one need to be serve first. The situation is further complicated when the multiple nested interrupts and traps occurs concurrently. With the availability of the exception-handling scheme, it is straightforward to resolve the conflicts among the mentioned exceptions. In addition, it will be easier to plan ahead to integrate new devices without having to worry about buggy exception handling.

# **TABLE OF CONTENTS**

| COVER PAGEi                                           |

|-------------------------------------------------------|

| REPORT STATUS DECLARATION FORMii                      |

| TITLE PAGEiii                                         |

| DECLARATION OF ORIGINALITY iv                         |

| ACKNOWLEDGEMENTSv                                     |

| ABSTRACTvi                                            |

| TABLE OF CONTENTSvii                                  |

| LIST OF FIGURESx                                      |

| LIST OF TABLES                                        |

| LIST OF ABBREVIATIONSxiii                             |

| Chapter 1 Introduction 1                              |

| 1.1 Background Information1                           |

| 1.1.1 RISC                                            |

| 1.1.2 MIPS                                            |

| 1.1.3 Exception                                       |

| 1.1.4 Interrupt                                       |

| 1.1.5 Trap                                            |

| 1.2 Project Motivation                                |

| 1.3 Problem Statement                                 |

| 1.4 Project Scope                                     |

| 1.5 Project Objectives                                |

| 1.6 Impact and significance7                          |

| Chapter 2 Literature Review                           |

| 2.1 Exception                                         |

| 2.2 Characteristic of exception                       |

| 2.3 Precise exception Vs Imprecise exception          |

| 2.4 Exception handler Scheme for MIPS14               |

| 2.4.1 Coprocessor 0                                   |

| 2.4.2 BadVaddr register 14                            |

| 2.4.3 Count Register and Compare Register 14          |

| 2.4.4 Status Register                                 |

| 2.4.5 Cause Register                                  |

| 2.4.6 EPC Register                                    |

| 2.4.7 Instruction associate with exception handling17 |

| 2.4.8 Step-by-step how MIPS handle Exception          |

| 2.5 Nested Exception                                       |     |

|------------------------------------------------------------|-----|

| 2.6 Exception handler scheme for ARM processor             |     |

| 2.6.1 Processor Mode for ARM                               |     |

| 2.6.2 ARM Exception                                        |     |

| 2.6.3 Entering and exiting an exception handler.           | 22  |

| 2.6.4 ARM Interrupt handling schemes                       |     |

| Chapter 3 Proposed Methods / Technologies Involved         |     |

| 3.1 General Work Flow                                      |     |

| 3.2 Design Tools                                           |     |

| 3.3 System Overview                                        |     |

| 3.4 Timeline                                               |     |

| Chapter 4 System Specification                             |     |

| 4.1 System Overview                                        |     |

| 4.2 MIPS ISA                                               |     |

| 4.2.1 Instruction Format                                   |     |

| 4.2.2 Addressing modes                                     |     |

| 4.2.3 Instruction Supported                                | 41  |

| 4.3 Functional View of the RISC32 Pipeline Processor       |     |

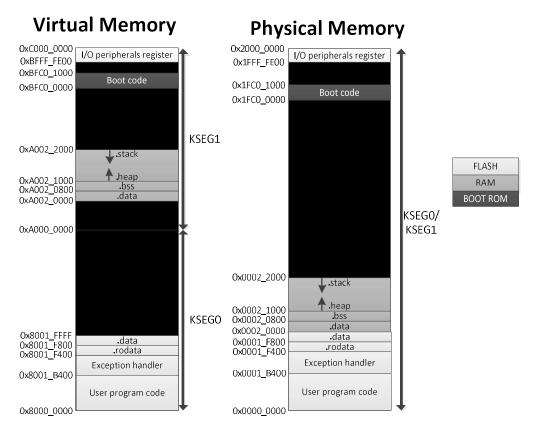

| 4.4 Memory Map                                             | 44  |

| 4.5 RISC32 Pipeline Processor Hierarchy.                   | 46  |

| Chapter 5 Analysis of the I/O system                       |     |

| 5.1 I/O System                                             |     |

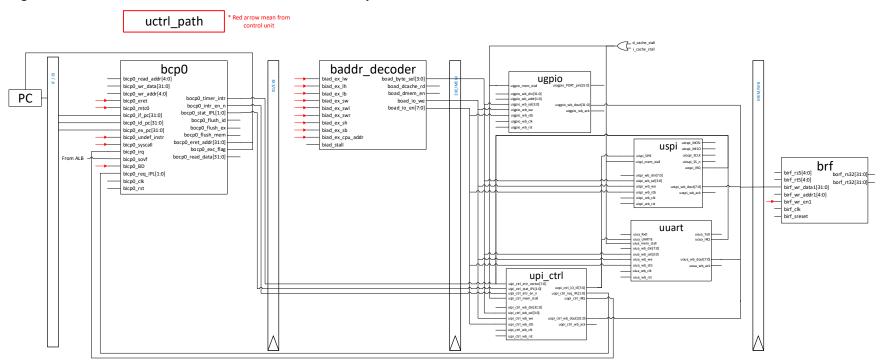

| 5.2 Micro-architecture for I/O system.                     | 49  |

| 5.3 Co-processor 0                                         | 50  |

| 5.4 Exception event                                        | 53  |

| 5.5 Priority for Exception Event                           | 54  |

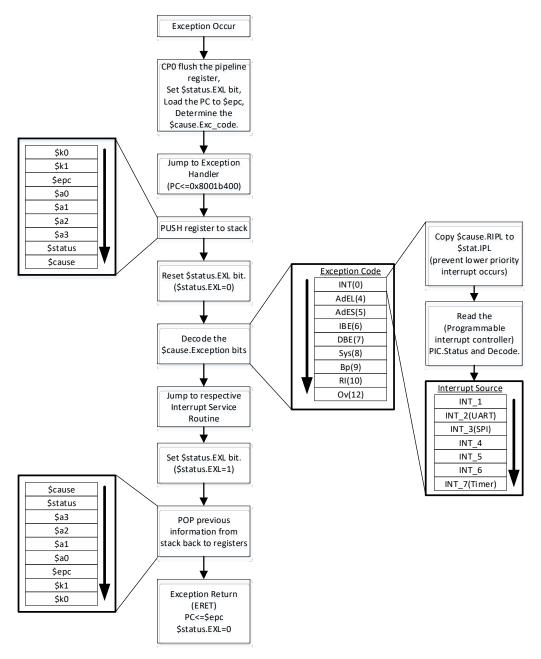

| 5.6 Exception Handler Scheme                               | 55  |

| Chapter 6 Verification Specification                       | 57  |

| 6.1 Test cases                                             | 57  |

| 6.2 MIPS assembly code                                     | 59  |

| 6.3 Simulation Result                                      |     |

| 6.4 Test Bench                                             | 103 |

| Chapter 7 Synthesis on FPGA                                | 106 |

| 7.1 Pin Allocation                                         | 106 |

| 7.2 Setting up the Test Environment for Functionality Test | 108 |

| Chapter 8 Conclusion & Future Enhancement                  | 111 |

| 8.1 Conclusion                                             | 111 |

| 8.2 Future Enhancement | 112 |

|------------------------|-----|

| References             | 113 |

# **LIST OF FIGURES**

| Figure Number | Title                                                   | Page |

|---------------|---------------------------------------------------------|------|

| Figure 1.1    | MIPS five-stage pipelining                              | 2    |

| Figure 2.1    | Different architecture use different names to represent | 9    |

|               | common exception event.                                 |      |

| Figure 2.2    | MIPS terminology to differentiate type of exception     | 9    |

|               | event.                                                  |      |

| Figure 2.3    | Exception event and its characteristics.                | 11   |

| Figure 2.4    | Coprocessor 0's registers and its usage.                | 14   |

| Figure 2.5    | Status Register.                                        | 15   |

| Figure 2.6    | Cause Register.                                         | 16   |

| Figure 2.7    | Exception code                                          | 16   |

| Figure 2.8    | Exceptions that may occur in the MIPS pipeline.         | 18   |

| Figure 2.9    | Flow chart for handle an exception.                     | 19   |

| Figure 2.10   | ARM Processor Mode                                      | 21   |

| Figure 2.11   | ARM processor exceptions and associated modes           | 22   |

| Figure 2.12   | Exception priority levels for ARM.                      | 22   |

| Figure 2.13   | Non-nested interrupt handling                           | 23   |

| Figure 2.14   | Nested interrupt handling                               | 24   |

| Figure 2.15   | Re-entrant interrupt handling                           | 25   |

| Figure 2.16   | Prioritized Simple interrupt handling                   | 26   |

| Figure 2.17   | Prioritized Standard interrupt handling                 | 27   |

| Figure 3.1    | Design flow of the project                              | 30   |

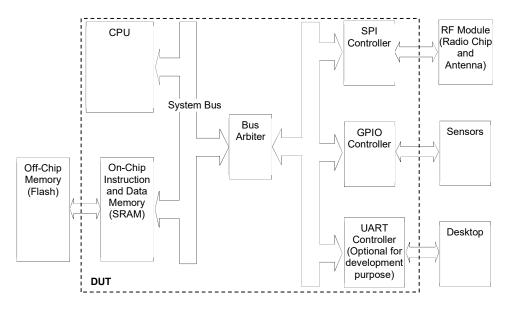

| Figure 3.2    | Block diagram of the IoT SoC Processor                  | 33   |

| Figure 3.3    | Gantt Chart For FYP1 and FYP2                           | 35   |

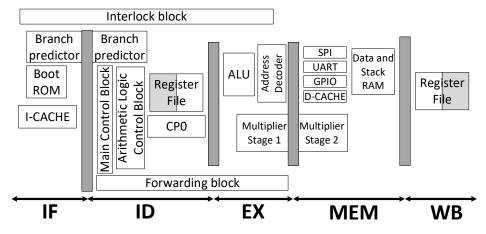

| Figure 4.1    | Architecture of the IoT SoC Processor.                  | 36   |

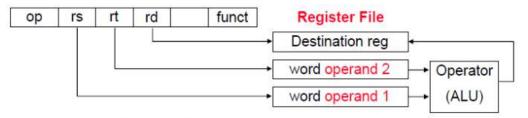

| Figure 4.2    | Instruction Format                                      | 38   |

| Figure 4.3    | Register Addressing mode                                | 38   |

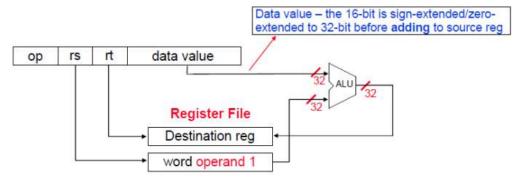

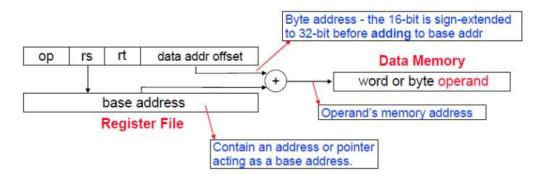

| Figure 4.4    | Immediate Addressing mode                               | 39   |

| Figure 4.5    | Base Addressing mode                                    | 39   |

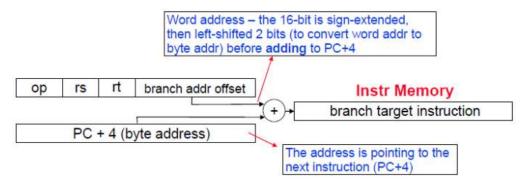

| Figure 4.6    | PC-Relative Addressing mode                             | 40   |

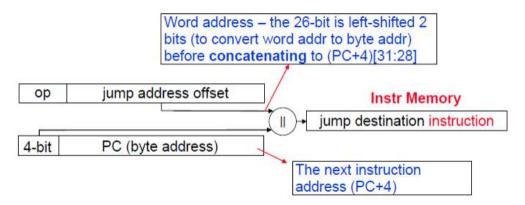

| Figure 4.7    | Pseudo-Direct Addressing mode                           | 40   |

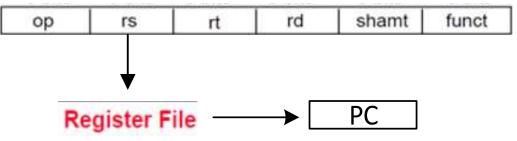

| Figure 4.8  | Register Direct Addressing mode         | 40  |

|-------------|-----------------------------------------|-----|

| Figure 4.9  | Functional view of the RISC32 processor | 43  |

| Figure 4.10 | Memory Map                              | 44  |

| Figure 5.1  | Micro-architecture for I/O system       | 49  |

| Figure 5.2  | Flow of the Exception Handler           | 55  |

| Figure 5.3  | Nested interrupt Handling Scheme        | 56  |

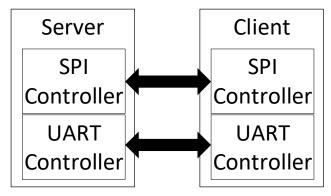

| Figure 6.1  | Connection between server and client    | 58  |

| Figure 7.1  | Test Environment set up                 | 108 |

| Figure 7.2  | Functionality of the LED Pin Connected  | 109 |

# LIST OF TABLES

| Table Number | Title                                                  | Page |

|--------------|--------------------------------------------------------|------|

| Table 3.1    | Comparison between simulation tools.                   | 31   |

| Table 3.2    | Hardware features of the IoT SoC Processor             | 33   |

| Table 4.1    | Hardware features of the IoT SoC Processor.            | 37   |

| Table 4.2    | Instruction Supported                                  | 42   |

| Table 4.3    | Memory map description                                 | 44   |

| Table 4.4    | RISC32 processor hierarchy.                            | 46   |

| Table 5.1    | Details for exception event                            | 50   |

| Table 5.2    | Conventional usage of CP0 registers                    | 51   |

| Table 5.3    | Details of the Status register                         | 52   |

| Table 5.4    | Details of the Cause register                          | 52   |

| Table 5.5    | Exception event and its characteristics for RISC32 IoT | 53   |

|              | Processor                                              |      |

| Table 5.6    | Priority for Exception Event                           | 54   |

| Table 7.1    | Pin allocation on ARTY Artix-7 FPGA Development        | 106  |

|              | Board                                                  |      |

# LIST OF ABBREVIATIONS

| ALU  | Arithmetic and Logic Unit                          |

|------|----------------------------------------------------|

| CP0  | Core Processor 0                                   |

| FIQ  | Fast Interrupt Request                             |

| FPGA | Field Programmable Gate Array                      |

| HDL  | Hardware Description Language                      |

| ΙΟΤ  | Internet of Things                                 |

| IRQ  | Interrupt Request                                  |

| ISR  | Interrupt Service Routine                          |

| MIPS | Microprocessor without Interlocked Pipelined Stage |

| RISC | Reduced Instruction Set Computing                  |

| RTL  | Register Transfer Level                            |

| SOC  | System-On-Chip                                     |

## **Chapter 1 Introduction**

#### 1.1 Background Information

# 1.1.1 RISC

RISC is short for Reduced Instruction Set Computing that developed and introduced by IBM in 1980 and coined by David Patterson. John Cocke of IBM Research in Yorktown, New York, originated the RISC concept in 1974 by proving that about 20% of the instructions in a computer did 80% of the work. Therefore, RISC using simple and small instruction set hence less hardware needed, so the system can operate at higher speeds and low-power consumption, and this makes the processor easier to build and test. RISC has four philosophy (Mok, 2009):

- Fixed instruction lengths.

- Load-store instruction sets.

- Limited number of addressing modes.

- Limited number of operations.

## 1.1.2 MIPS

MIPS short for Microprocessor without Interlocked Pipelined Stage is the Microprocessor based on the Reduced Instruction Set Computer (RISC) architecture. MIPS initiated in 1981 by a team led by John L. Hennessy and come out conclusion in the year 1984. Recently, MIPS implement in the digital home, networking, embedded system, Internet of things and mobile applications. At the pass, MIPS used in video game consoles such as Sony PlayStation, PlayStation and PlayStation Portable. The MIPS ISA based on a 32-bit word. MIPS support 32-bit addressing (word-addressed). MIPS is a load-store architecture that means it can perform load and store operation between memory and registers and ALU operation between registers. MIPS is a modular architecture it contains coprocessors 0(CP0) which handle the exception and coprocessors 1(CP1) which handle the floating-point operation (Mok, 2009). The details of MIPS architecture and relative information can found in a book, which name Computer Organization and Design: The Hardware/ Software Interface (Patterson and Hennessy, 2008). MIPS processors operate by breaking instruction execution cycle into multiple small independent stages and this technic call pipelining. Figure 1.1 shown the MIPS 5-stage pipelining

|                     | Clock number |    |    |     |     |     |     |     |    |

|---------------------|--------------|----|----|-----|-----|-----|-----|-----|----|

| Instruction number  | 1            | 2  | 3  | 4   | 5   | 6   | 7   | 8   | 9  |

| Instruction i       | IF           | ID | EX | MEM | WB  |     |     |     |    |

| Instruction $i + 1$ |              | IF | ID | EX  | MEM | WB  |     |     |    |

| Instruction $i + 2$ |              |    | IF | ID  | EX  | MEM | WB  |     |    |

| Instruction $i + 3$ |              |    |    | IF  | ID  | EX  | MEM | WB  |    |

| Instruction $i + 4$ |              |    |    |     | IF  | ID  | EX  | MEM | WB |

Figure 1.1: MIPS five-stage pipelining (Patterson & Hennessy, 2002, p.A-7)

The instruction execution is divided to 5 stages, IF ("Instruction Fetch"), ID ("Instruction Decode"), EX ("Instruction Execution"), MEM ("Memory access") and WB ("Write Back").

- IF: Send the program counter (PC) to instruction memory, fetch the instruction from the instruction memory/instruction cache (I-cache) and update the PC by adding 4 (instruction is 4 bytes).

- ID: Decodes the instruction and read the corresponding register for CPU use.

- EX: Performs an arithmetic or logical operation.

- MEM: Write or Read a data from the data memory (D-cache) only the instruction load and store will use this stage.

- WB: store the value obtained from an operation back to the register file.

# 1.1.3 Exception

Exception is an event other than branches or jump that change the normal flow of instruction execution (Patterson & Hennessy, 2008, p.384). Exception was classify into two type, which are synchronous exception and asynchronous exception. Asynchronous exception is the exception that occurs with no relation to the program executed such as I/O requests while synchronous exception is exception that occurs at the same place every time the program executed with the same data and memory allocation, example for synchronous exception are arithmetic overflow, undefined instruction, and page fault. (Patterson & Hennessy, 2002, p.A-40)

# 1.1.4 Interrupt

An interrupt is an external event that changes the normal flow of instruction execution (Patterson & Hennessy, 2008, p.384). Interrupts are the asynchronous exception. Example for the Asynchronous event is I/O device request, power failure and Hardware malfunction. The asynchronous exception usually handled after the completion of the current instruction, which makes them easier to handle. Coprocessor 0 (CP0) system control coprocessor will handle these interrupts.

# <u>1.1.5 Trap</u>

The trap is an internal event that changes the normal flow of instruction execution. The trap is the synchronous exception. Example for the synchronous event is invoked operating system, tracing instruction execution, breakpoint, arithmetic overflow, page fault, misaligned memory accesses, memory protection violations and using undefined instruction.

Chapter 1 Introduction

### **1.2 Project Motivation**

A 32-bit 5-stage pipeline RISC soft-core can be advantageous in creating a core-based environment to assist research and development work in the area of developing Intellectual Properties (IP) cores. However, there are limitations in obtaining such workable core-based design environment

- Microchip design companies designed microprocessor as Intellectual Property or IP for commercial purpose. The microprocessor IP includes information on the entire design process for the front-end (modelling and verification) and back-end (physical design) integrated circuit (IC) design. These are trade secrets of a company and certainly not made available in the market at an affordable price for research purpose.

- Several freely available microprocessor cores can found in internet, most of them can found at OpenCores (http://www.opencores.org/). Unfortunately, these processors do not implement the entire MIPS Instruction Set Architecture (ISA) and lack comprehensive documentation. This makes them unsuitable for reuse and customization.

- The verification specification for a freely available RISC microprocessor core that is available on the Internet is not well developed and incomplete. Therefore, without a good verification specification, the verification process will be slow and hence, will slow down the overall design process.

- The lack of well-developed verification specifications for these microprocessor cores will inevitably affect the physical design phase. A design needs functionally proven before the physical design phase can proceed smoothly. Otherwise, if the front-end design has to be changed, the physical design process has to be re-design.

This project will aim to provide solutions to the above problems by creating a 32-bit RISC core-based development environment to assist research work in the area of softcore and application specific hardware modelling. In the RISC32 project, the project divided into several units based on MIPS architecture.

#### 1.3 Problem Statement

Currently, a team from FICT has designed an IoT SoC processor based on a subset of the MIPS ISA. The processor supports three type of communication interface, which are the UART, SPI and GPIO. The UART, SPI and GPIO have integrated into the IoT processor using I/O mapped technique. The individual test cases for each I/O have been conducted but have not gone through thorough multiple and nested exception verification and there are lack of well-defined exception handler scheme to manipulate the multiple interrupt occurrence and traps. Exception makes the 5-stage pipelining processor more complicated because the exception is hard to be handled in pipeline processor due the overlapping instruction characteristics (Patterson & Hennessy, 2002, p.A-37). The exception causes the instruction to stop executing in the middle of execution. To handle Exception, first, we need to detect the exception, what is the cause, when it occurs, how to handle it and what to do after exception. For 5-stage pipeline processor, handling exception is more difficult when multiple exceptions occur at the same time (clock cycle). Fortunately, the cause of exception can be determine based on the stage where by an instruction cause exception. On the other hand, if the multiple exceptions occur in same time, we need to come up with a plan to determine which exception we need to serve first to ensure smooth running of the program. The exception will also occur out-of-order that means out of the instruction execution order, this makes exception more difficult to handle. After handling the exception, there is two alternative, which is terminate the program or return to the program. When returning to the program, the problem is where the program needs to restart at the user program, the branch delay slot also makes a return from the exception to the user program more complicated. When the exception was in execution, there is possibly another exception occurs, this also known as a nested exception. The main purpose for this project is to develop an exception scheme to handle various type of exception in order to ensure future reliable I/Os integration and smooth running of the user program.

# 1.4 Project Scope

The project scope includes the development of an exception handler scheme for interrupt conflict and the nested interrupt resolution. The exception scheme also needs to be verified its functionality through simulation by write the test code to trigger the interrupt individually. After that, trigger the multiple I/O interrupt and trap make sure the exception scheme well function. In addition, physical synthesis the RISC32 IoT processor on FPGA board will conducted to verify the correctness of the exception scheme.

# 1.5 Project Objectives

The Project Objectives are as shown below:

- To develop an exception scheme for RISC32 IOT processor.

- To develop a test bench to verify the exception handle and Interrupt Service Routine (ISR) code.

- To synthesize the RISC32 IoT Processor and carry out physical tests on the I/O function.

Chapter 1 Introduction

# 1.6 Impact and significance

As a summary of the problem statement, there is a lack of well-developed and wellfounded 32-bit RISC microprocessor core-based development environment. The development environment refers to the availability of the following:

- A well-developed design document, which includes the chip specification, architecture specification and micro-architecture specification.

- A fully functional well-developed 32-bit RISC architecture core in the form of synthesis-ready RTL written in Verilog HDL.

- A well-developed verification environment for the 32-bit RISC core. The verification specification should contain suitable verification methodology, verification techniques, test plans, test bench architectures etc.

- A complete physical design in Field Programmable Gate Array (FPGA) with documented timing and resource usage information.

With the available of well-defined exception handler scheme, it can build up high confident level to extend the IoT SoC processor. It can allow us to add-on extra communication interface on processor. For instance, integration of ADC (analogue to digital converter) to the processor without having to worry about the data conflicting. Consequently, the research work could be done easier and speed up significantly.

# **Chapter 2 Literature Review**

# 2.1 Exception

Exception is an event other than branch or jump that change the normal flow of instruction execution. The type of exception are listed below :- (Patterson & Hennessy, 2002, pp.A-38-A39)

- I/O device request

- Invoking an operating system service from a user program

- Tracing instruction execution

- Breakpoint (programmer-requested interrupt)

- Integer arithmetic overflow

- FP arithmetic anomaly

- Page fault (not in main memory)

- Misaligned memory accesses (if alignment is required)

- Memory protection violation

- Using an undefined or unimplemented instruction

- Hardware malfunctions

- Power failure

Different Architecture using different terminology to describe the exception. Figure2.1 show the different name for the common exception event.

| Exception event                                                 | IBM 360                                                      | VAX                                                                                                                                   | Motorola 680x0                                               | Intel 80x86                                            |

|-----------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|

| I/O device request                                              | Input/output<br>interruption                                 | Device interrupt                                                                                                                      | Exception (level 07<br>autovector)                           | Vectored interrupt                                     |

| Invoking the operating<br>system service from a<br>user program | Supervisor call interruption                                 | Exception (change mode supervisor trap)                                                                                               | Exception<br>(unimplemented<br>instruction)—<br>on Macintosh | Interrupt<br>(INT instruction)                         |

| Tracing instruction execution                                   | Not applicable                                               | Exception (trace fault)                                                                                                               | Exception (trace)                                            | Interrupt (single-<br>step trap)                       |

| Breakpoint                                                      | Not applicable                                               | Exception<br>(breakpoint fault)                                                                                                       | Exception (illegal<br>instruction or<br>breakpoint)          | Interrupt<br>(breakpoint trap)                         |

| Integer arithmetic<br>overflow or underflow;<br>FP trap         | Program interruption<br>(overflow or<br>underflow exception) | Exception (integer<br>overflow trap or<br>floating underflow<br>fault)                                                                | Exception<br>(floating-point<br>coprocessor errors)          | Interrupt (overflow<br>trap or math unit<br>exception) |

| Page fault<br>(not in main memory)                              | Not applicable<br>(only in 370)                              | Exception (translation<br>not valid fault)                                                                                            | Exception (memory-<br>management unit<br>errors)             | Interrupt<br>(page fault)                              |

| Misaligned memory<br>accesses                                   | Program interruption<br>(specification<br>exception)         | Not applicable Exception<br>(address error)                                                                                           |                                                              | Not applicable                                         |

| Memory protection violations                                    | Program interruption<br>(protection exception)               | Exception (access<br>control violation<br>fault)                                                                                      | Exception<br>(bus error)                                     | Interrupt<br>(protection<br>exception)                 |

| Using undefined<br>instructions                                 | Program interruption<br>(operation exception)                | Exception (opcode<br>privileged/reserved<br>fault) Exception (illegal<br>instruction or break-<br>point/unimplemented<br>instruction) |                                                              | Interrupt (invalid<br>opcode)                          |

| Hardware<br>malfunctions                                        | Machine-check interruption                                   | Exception (machine-<br>check abort)                                                                                                   | Exception (bus error)                                        | Not applicable                                         |

| Power failure                                                   | Machine-check interruption                                   | Urgent interrupt                                                                                                                      | Not applicable                                               | Nonmaskable<br>interrupt                               |

Figure 2.1 Different architecture use different names to represent common exception event. IBM and Intel using interrupt for every exception event. Motorola using exception while Vax using both interrupt and exception. (Patterson & Hennessy, 2002, p.A-40).

In MIPS, it classify type of exception event into external and internal. External exception event name interrupt while internal exception event name exception. Figure 2.2 show that the exception event for MIPS terminology.

| Type of event                                 | From where? | MIPS terminology       |  |

|-----------------------------------------------|-------------|------------------------|--|

| I/O device request                            | External    | Interrupt              |  |

| Invoke the operating system from user program | Internal    | Exception              |  |

| Arithmetic overflow                           | Internal    | Exception              |  |

| Using an undefined instruction                | Internal    | Exception              |  |

| Hardware malfunctions                         | Either      | Exception or interrupt |  |

Figure 2.2 MIPS terminology to differentiate type of exception event. (Patterson & Hennessy, 2008, p.385).

Chapter 2 Literature Review

#### 2.2 Characteristic of exception

Exception can be classify based on its characteristic. Figure 2.3 show the exception event and its characteristics. The five main independent characteristic are (Patterson & Hennessy, 2002, pp.A-40-A-41):

# Synchronous Vs Asynchronous

Asynchronous exception is the exception that occurs with no relation to the program executed such as I/O requests while synchronous exception is exception that occurs at the same place every time the program executed with the same data and memory allocation, example for synchronous exception are arithmetic overflow, undefined instruction, and page fault. Asynchronous usually handle after the current instruction complete execute.

# User requested Vs Coerced

User requested event is the user request it to happen, for instance, "syscall". User requested actually not really exception because it is predictable but the only method to create the event is to cause exception. Coerced exception is an unpredictable event that not under the user control.

## User maskable Vs user nonmaskable

If the exception can disable by user program the event is user maskable event. Otherwise, it is nonmaskable event.

## Within Vs between instructions

If the exception event occur and stop the current executing instruction in the pipeline then the event is classify "within". If the exception event allow the current executing instruction to complete, then only serve the exception event then the event id classify "between".

## Resume Vs Terminate

After handling the exception event, there are two alternative way, which is return to the user program, or terminate the current program.

# Chapter 2 Literature Review

| Exception type                                     | Synchronous vs.<br>asynchronous | User request<br>vs. coerced | User<br>maskable vs.<br>nonmaskable | Within vs.<br>between<br>instructions | Resume vs<br>terminate |

|----------------------------------------------------|---------------------------------|-----------------------------|-------------------------------------|---------------------------------------|------------------------|

| I/O device request                                 | Asynchronous                    | Coerced                     | Nonmaskable                         | Between                               | Resume                 |

| Invoke operating system                            | Synchronous                     | User request                | Nonmaskable                         | Between                               | Resume                 |

| Tracing instruction execution                      | Synchronous                     | User request                | User maskable                       | Between                               | Resume                 |

| Breakpoint                                         | Synchronous                     | User request                | User maskable                       | Between                               | Resume                 |

| Integer arithmetic overflow                        | Synchronous                     | Coerced                     | User maskable                       | Within                                | Resume                 |

| Floating-point arithmetic<br>overflow or underflow | Synchronous                     | Coerced                     | User maskable                       | Within                                | Resume                 |

| Page fault                                         | Synchronous                     | Coerced                     | Nonmaskable                         | Within                                | Resume                 |

| Misaligned memory accesses                         | Synchronous                     | Coerced                     | User maskable                       | Within                                | Resume                 |

| Memory protection violations                       | Synchronous                     | Coerced                     | Nonmaskable                         | Within                                | Resume                 |

| Using undefined instructions                       | Synchronous                     | Coerced                     | Nonmaskable                         | Within                                | Terminate              |

| Hardware malfunctions                              | Asynchronous                    | Coerced                     | Nonmaskable                         | Within                                | Terminate              |

| Power failure                                      | Asynchronous                    | Coerced                     | Nonmaskable                         | Within                                | Terminate              |

Figure 2.3 Exception event and its characteristics. (Patterson & Hennessy, 2002, p.A-42).

#### 2.3 Precise exception Vs Imprecise exception

Precise exception

Precise exception means that when the exception occurred, the instruction causes the exception (instruction victim) will be recorded. There are able to draw a line between the instruction before the instruction victim and the instruction after the instruction victim. Beside, all the instruction before the instruction victim will executed while all the instruction after the instruction victim will flushed out from pipeline. This method make programmer work more easy because they can ignore the timing effect of the CPU implementation.

The feature provided with precise exception are (Sweetman, 2007, pp.107-108):

- Unambiguous proof of guilt: After the exception, exception will return to the user program by load the value from EPC register into PC. EPC will always point to the instruction that cause the exception. However, EPC also will point to the preceding branch instruction if the BD in cause register was set.

- Exceptions appear in instruction sequence: For pipeline processor, multiple exception will occur in the same time in different stage of execution. For instance, the load instruction (lw) cause the Memory Translation exception in the MEM stage (4<sup>th</sup> stage of the pipeline) and at the same time, a later instruction hit an exception in the ID stage (2<sup>nd</sup> stage of the pipeline), this will cause the out of order exception. The later instruction arise the exception earlier than the prior one. To avoid this problem, an exception detected early but no perform the operation immediately, the exception event just marked and passed until end of the MEM stage.

- Subsequent instructions nullified: Because of pipelining, instructions following the victim instruction have been started and inside pipeline. However, MIPS guarantee that, the instruction following the victim instruction will not have effect toward the register file or CPU and return to the user program just like exception no occur.

## Imprecise exception

The imprecise exception mean that when the exception occur we cannot precisely tell where we need to return after exception. For instance: (Patterson & Hennessy, 2002, p.A-54).

- 1. DIV.D F0,F2,F4

- 2. ADD.D F10,F10,F8

- 3. SUB.D F12,F12,F14

ADD.D and SUB.D expected to complete before the DIV.D because DIV.D need more cycle to complete compare to ADD.D and SUB.D. This also known as out-of-order completion. Suppose SUB.D cause an arithmetic exception at the point where ADD.D completed but DIV.D has not completed. This result in imprecise exception because it cannot precisely tell that where should return after the exception.

Another example (Zjueducn, n.d., p.13)

- 1. Mult r1,r2,r3 ;Multiply take 10 cycles

- 2. Add r10,r11,r12 ;Add take 5 cycle

Add will complete before the multiply. If the multiply cause an arithmetic exception, but add has already update the value in r10. This result imprecise exception.

In general, Imprecise exception always involve when there are instruction take multiple cycle to complete For instance, instruction involve in floating point, multiply and divide. Imprecise exception are harder to handle compare to precise exception.

# 2.4 Exception handler Scheme for MIPS

# 2.4.1 Coprocessor 0

In MIPS, there have two Coprocessor, which are Coprocessor 0 and Coprocessor 1. In this project, we are more interesting in Coprocessor 0. Coprocessor 0 also known as system control coprocessor, it handle the exception and interrupt by records the information that correspond exception event. Coprocessor 0 has its own registers files. Figure 2.4 shown the coprocessor 0's registers and its usage.

| Register | Register |                                                                    |

|----------|----------|--------------------------------------------------------------------|

| name     | number   | Usage                                                              |

| BadVAddr | 8        | memory address at which an offending memory reference occurred     |

| Count    | 9        | timer                                                              |

| Compare  | 11       | value compared against timer that causes interrupt when they match |

| Status   | 12       | interrupt mask and enable bits                                     |

| Cause    | 13       | exception type and pending interrupt bits                          |

| EPC      | 14       | address of instruction that caused exception                       |

| Config   | 16       | configuration of machine                                           |

Figure 2.4 coprocessor 0's registers and its usage. (Patterson & Hennessy, 2008, p.B-33).

## 2.4.2 BadVaddr register

BadVaddr Register will store the referenced memory location's address if the instruction that caused exception made a memory access.

## 2.4.3 Count Register and Compare Register

Count Register act as a timer, increment at a fixed period. When the value in the Count Register count until the value in the Compare register, it will raise a hardware interrupt.

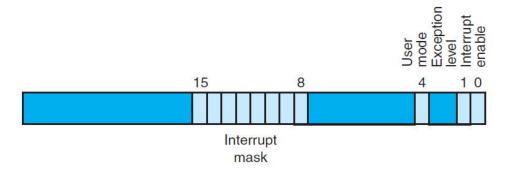

## 2.4.4 Status Register

Status Register used to indicate the exception details. Figure 2.5 show the Status

Register and its field.

It made up by 4 field:

• Interrupt Mask (Status Register[15:8])

-There are 6 bit for hardware and 2 bit for software interrupt level

-Mask bit = 1, when the interrupt is enable.

-Mask bit=0, when the interrupt is disable.

- Interrupt occur when both interrupt mask (Status Register) and Interrupt Pending (Cause Register) was asserted.

- When interrupt raise, correspond Interrupt pending bit will asserted but it will not be served when the Interrupt Mask disable.

• User Mode /Kernel mode(Status Register[4])

Status Register [4] =0, the processor running in kernel mode.

Status Register [4] =1, the processor running in user mode.

• Exception Level (Status Register[1])

-Normally 0.

-Set to 1 when exception event happen.

- To prevent the multi-level exception by prevent other exception event changing the EPC value.

- Should reset after finish exception.

• Interrupt Enable (Status Register[0])

Status Register [0] = 1, interrupt enable.

Status Register [0] = 0, interrupt disable.

Figure 2.5: Status Register. (Patterson & Hennessy, 2008, p.B-35)

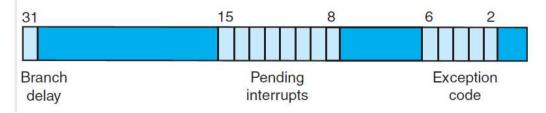

#### 2.4.5 Cause Register

Cause register is use to determine the causes for the exception. Figure 2.6 show that the Cause register and its field.

- Branch Delay(Cause Register[31])

- Cause Register [31] = 1, when the exception occur inside in branch/jump instruction.

- EPC store the branch/jump instruction instead of the instruction cause the exception.

-exception handler must look at EPC+4 for the offending instruction.

• Pending interrupt (Cause Register[15:8])

-Pending bit = 1, when the exception occur but no serve.

-mainly use to handle multiple exception occur at a same time.

• Exception Code (Cause Register[6:2])

-use the indicate the causes of exception

-the exception code shown in Figure 2.7.

| Number | Name | Cause of exception                                  |  |

|--------|------|-----------------------------------------------------|--|

| 0      | Int  | interrupt (hardware)                                |  |

| 4      | AdEL | address error exception (load or instruction fetch) |  |

| 5      | AdES | address error exception (store)                     |  |

| 6      | IBE  | bus error on instruction fetch                      |  |

| 7      | DBE  | bus error on data load or store                     |  |

| 8      | Sys  | syscall exception                                   |  |

| 9      | Bp   | breakpoint exception                                |  |

| 10     | RI   | reserved instruction exception                      |  |

| 11     | CpU  | coprocessor unimplemented                           |  |

| 12     | Ov   | arithmetic overflow exception                       |  |

| 13     | Tr   | trap                                                |  |

| 15     | FPE  | floating point                                      |  |

Figure 2.7: Exception code (Patterson & Hennessy, 2008, p.B-35).

#### 2.4.6 EPC Register

- Store the instruction address that causes the exception occur.

- If BD (Cause Register [31] was set, when the exception occur, the branch / jump, instruction was load into EPC Register instead the instruction cause exception.

## 2.4.7 Instruction associate with exception handling

Some instruction are dedicated build to access the Register in CP0, because CP0 does not implement ALU unit to carry out the operation, so, the data need to move to the CPU for compute and move it back to CP0. The instruction and its function are list below:- (Sweetman, 2007, p.55).

| mtc0 <register cpu="" in="">, &lt; destination in CP0&gt;</register> | #move data from CPU to CP0 |

|----------------------------------------------------------------------|----------------------------|

| mfc0 < register in CPU >, < source in CP0>                           | #move data from CP0 to CPU |

| eret                                                                 | # return from exception    |

When the bit 4(user mode/ kernel mode) in the status register was set, it means that the program is in user mode, it can use all the general-purpose register in CPU for data transfer. However, when enter the exception handler, normally the program execute in kernel mode, register k0 and k1 reserved for kernel usage. For instruction "eret", it return form exception by load the EPC value into PC.

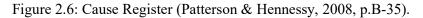

## 2.4.8 Step-by-step how MIPS handle Exception

1. Determine which instruction that cause the exception. For MIPS, there are multi instruction in the pipeline processor within a single clock cycle. At different pipeline stage, it will arise different exception. The detail shown in Figure 2.8:

# Pipeline stage Problem exceptions occurring

| IF  | Page fault on instruction fetch; misaligned memory access; memory protection violation |  |

|-----|----------------------------------------------------------------------------------------|--|

| ID  | Undefined or illegal opcode                                                            |  |

| EX  | Arithmetic exception                                                                   |  |

| MEM | Page fault on data fetch; misaligned memory access; memory protection violation        |  |

| WB  | None                                                                                   |  |

Figure 2.8: Exceptions that may occur in the MIPS pipeline. (Patterson & Hennessy, 2002, p.A-44).

- 2. Stop the offending instruction and let the prior instruction finished

- 3. Flush the offending instruction and the all instruction inside the pipeline stage.

- 4. Load PC value into EPC, for determine the cause or return from exception.

- 5. Load the 0x80000180 into PC. 0x80000180 is the single entry point for all exceptions in MIPS architecture.

- 6. Determine the cause by using the information inside Cause Register.

- 7. Pass the work to Operating system, Operating system will handle the case. In other word, jump to the interrupt service routine. OS will handle the cases by :

- Terminate the program and display the reason.

- -undefined instruction

- -hardware failure

- -arithmetic overflow

- Perform the desired task and return to program from exception

- -I/O device request

- -system service call

- 8. Return from exception by load EPC+4 into PC.

The flow of the handle the exception shown in the Figure 2.9.

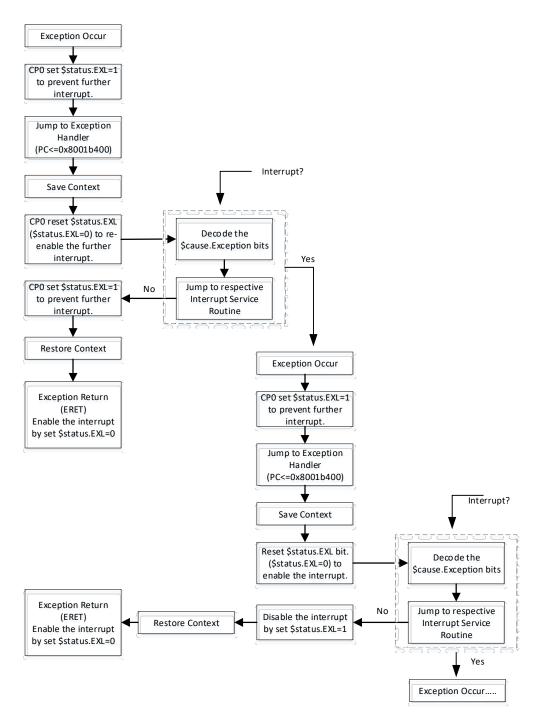

Figure 2.9 Flow chart for handle an exception.

For above solution, it look completely fine but it only can handle one level exception, which means that it cannot interrupt when inside the exception handler. Sometime we need to interrupt when interrupt is serving this also known as multi-level exception or Nested Exception.

## 2.5 Nested Exception

Nested Exception is the permit for other exception to occur when the system are serving an exception. When exception occur, CP0 will write to the cause register, status register and the EPC. For nested exception, value in the cause register, status register and EPC was expected to be overwrite (Sweetman, 2007, pp.114-115). To support the nested exception, we need to store the value in cause register, status register and EPC value inside the stack. However, interrupt will also occur when copying the value to the stack. To solve this problem, we need to disable all interrupt when copying the value to the stack. We can implement the Interrupt Priority Level (IPL) by control the masking value of Status register to disable the further interrupt. However, the interrupt resource was limited, interrupt have a chance to occur when changing the value in Status Register causes the Status Register to be overwrite. This problem also known as the Race Condition. To solve this problem, we need to make the program mutual exclusion by using the software way, which is semaphores, to allow atomic changes of Status register.

# 2.6 Exception handler scheme for ARM processor

# 2.6.1 Processor Mode for ARM

The ARM processor internally has seven different modes of operation, which are, User mode, FIQ mode, IRQ mode, Supervisor mode, Abort mode, Undefined mode, System mode. The following figure summarizes the seven modes.

| Processor Mode   | Description Normal program execution mode |  |

|------------------|-------------------------------------------|--|

| User (usr)       |                                           |  |

| FIQ (fiq)        | Fast data processing mode                 |  |

| IRQ (irq)        | For general purpose interrupts            |  |

| Supervisor (svc) | A protected mode for the operating system |  |

| Abort (abt)      | When data or instruction fetch is aborted |  |

| Undefined (und)  | For undefined instructions                |  |

| System (sys)     | Operating system privileged mode          |  |

Figure 2.10 ARM Processor Mode

For user mode, it used for normal program execution. FIQ mode used for interrupts requiring fast response for instance data transfer with DMA. IRQ mode used for general-purpose interrupts for example I/O interrupt. Supervisor mode used when operating system support needed. Abort mode used when data or instruction fetch have aborted. Undefined mode used when undefined instruction fetched. System mode is the Operating system privilege mode for users.

# 2.6.2 ARM Exception

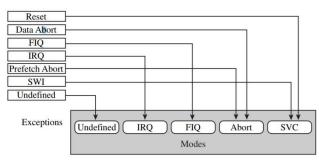

ARM have support few type of exception, which are Fast Interrupt Request, Interrupt Request, Software interrupt (SWI) and Reset, Prefetch Abort and Data Abort and Undefined Instruction. Figure 2.11 summaries the type of exception support by ARM. Figure 2.12 shown the priority level for ARM exception.

Figure 2.11 ARM processor exceptions and associated modes. (Sloss, Symes&Wright, 2004, p.319).

| Exceptions             | Priority | I bit | Fbit |

|------------------------|----------|-------|------|

| Reset                  | 1        | 1     | 1    |

| Data Abort             | 2        | 1     | _    |

| Fast Interrupt Request | 3        | 1     | 1    |

| Interrupt Request      | 4        | 1     | _    |

| Prefetch Abort         | 5        | 1     | —    |

| Software Interrupt     | 6        | 1     | —    |

| Undefined Instruction  | 6        | 1     | _    |

Figure 2.12 Exception priority levels for ARM. (Sloss, Symes&Wright, 2004, p.319).

## 2.6.3 Entering and exiting an exception handler.

Sloss, Symes and Wright (2004) list out the step of ARM processor to handle an exception. First, preserve the address of the next instruction, copy the Current Program Status Register (CPSR) to Saved Program Status Register (SPSR) and the Program counter to the Link Register (LR). Next, force the CPSR mode bits to a value depending on the raised exception, force the Program counter (PC) to fetch the next instruction from the exception vector table. Now the handler is running in the mode associated with the raised exception. When handler is done, the CPSR restored from the saved SPSR. PC restored with the value of (LR – offset) and the offset value depends on the type of the exception. Last, clear the interrupt disable flags if they were set.

### 2.6.4 ARM Interrupt handling schemes

Sloss, Symes and Wright (2004) has introduce some interrupt handling scheme, which are, non-nested interrupt handling, nested interrupt handling, re-entrant interrupt handling, prioritized simple interrupt handling, prioritized standard interrupt handling, prioritized direct interrupt handling and prioritized grouped interrupt handling.

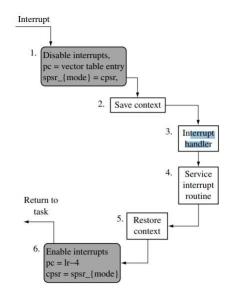

#### Non-nested interrupt handling

This non-nested interrupt handling is the simplest scheme, it only allow one interrupt occur in concurrently. Once the processor received an interrupt, it will disable other interrupt and save the current context into SPSR. After that, jump to the exception handler to identify the interrupt source and jump to appropriate Interrupt service routine (ISR). After service the interrupt, restore the context from SPSR and re-enable the interrupt. The flow chart for non-nested interrupt handling shown in figure below.

Figure 2.13 Non-nested interrupt handling. (Sloss, Symes&Wright, 2004, p.334). These non-nested interrupt handling scheme are not suitable for complex embedded system which has multiple interrupt occurrences and it has high interrupt latency but it is easy to implement and debug.

### Nested interrupt handling

The scheme can support multiple interrupt in the same time. This achieved by reenabling interrupts before the interrupt has fully served. This feature will increases the complexity of the system but improves the latency. The scheme should be designed carefully to ensure the context saving and restoration from being interrupted. The goal of nested handling is to respond to interrupts quickly. The flow chart for nested interrupt handling shown in figure below.

Figure 2.14 Nested interrupt handling. (Sloss, Symes & Wright, 2004, p.337). The disadvantage of scheme is that it does not differentiate interrupts by priorities, so lower priority interrupt can block higher priority interrupts, it will cause deadlock. The advantage is it can handle multiple interrupt in the same time and improve latency.

### <u>Re-entrant Interrupt Handling</u>

The difference between this scheme and the nested interrupt handling is re-enable interrupts earlier on the re-entrant interrupt handler compare to the nested interrupt handling. This can reduce interrupt latency. The external interrupt is clear before re-enabling interrupts to protect the system from infinite interrupt sequence. This is done by a using a mask in the interrupt controller. By using this mask, prioritizing interrupts is possible but this handler is more complex. The flow chart for Re-entrant interrupt handling shown in figure below.

Figure 2.15 Re-entrant interrupt handling. (Sloss, Symes & Wright, 2004, p.343). The advantage of this scheme are it can handle multiple interrupt with the differing priority level and it provide low latency but the scheme will be more difficult to build.

#### Prioritized Simple Interrupt handling

In this scheme, the handler will associate a priority level with a particular interrupt source. A higher priority interrupt will take precedence over a lower priority interrupt. (Sloss, Symes&Wright, 2004, p.319). Handling prioritization can done by means of software or hardware. In case of hardware prioritization, the handler is simpler to design because the interrupt controller will give the interrupt signal of the highest priority interrupt requiring service. However, on the other side, the system needs more initialization code at start-up since priority level tables have to construct before the system switched on. When an interrupt signal raised, a fixed amount of comparisons will be compare with the available set of priority levels. The flow chart for Prioritized Simple interrupt handling shown in figure below.

Figure 2.16 Prioritized Simple interrupt handling. (Sloss, Symes & Wright, 2004, p.348).

The advantage for this scheme is it can handles prioritized interrupts and low interrupt latency. The low priority interrupt cannot take the precedence over the higher priority interrupt, with this feature, it solve the deadlock problem. The disadvantage for this scheme is the time taken to get to a low-priority service routine is same, as high-priority service routine and it cannot support multiple interrupt occurrence. Chapter 2 Literature Review

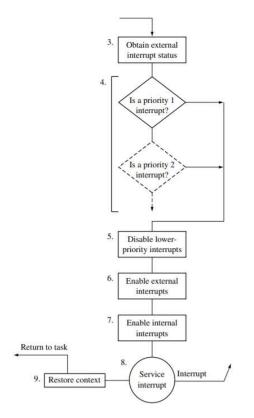

### Prioritized Standard Interrupt Handling

This scheme is the alternative of prioritized simple interrupt handler. It has the advantage of low interrupt latency for higher priority interrupts than the lower priority interrupt. The flow chart for Prioritized Simple interrupt handling shown in figure below.

Figure 2.17 Prioritized Standard interrupt handling. (Sloss, Symes & Wright, 2004, p.353).

### Prioritized Direct Interrupt Handling

There are two different between the prioritized direct interrupt handler and the prioritized standard interrupt handler. Some of the processing move to the individual ISR from the handler. Each individual ISR have the responsible to mask out the lower priority interrupt. This type of handler is relatively simple since the masking done by the individual ISR, but there are code duplication in each individual ISR since each interrupt service routine have to mask out the lower-priority interrupt that is same operation.

### Prioritized Grouped Interrupt Handler

This handler designed to handle large amount of interrupts by grouping interrupts together and forming a subset that can have a priority level. This way of grouping reduces the complexity of the handler since it does not scan through every interrupt to determine the priority. If the prioritized grouped interrupt handler is well design, it will improve the overall system response times dramatically, on the other hand if it is badly design such that interrupts are not group well, and then some important interrupts will dealt as low priority interrupts and vice versa. The most complex and possibly critical part of such scheme is the decision on which interrupts should be group together. The advantage for this scheme are can handle a large number of interrupts, and reduces the response time since the time taken to determine the priority level is shorter but it is difficult to group the interrupt.

### **Chapter 3 Proposed Methods / Technologies Involved**

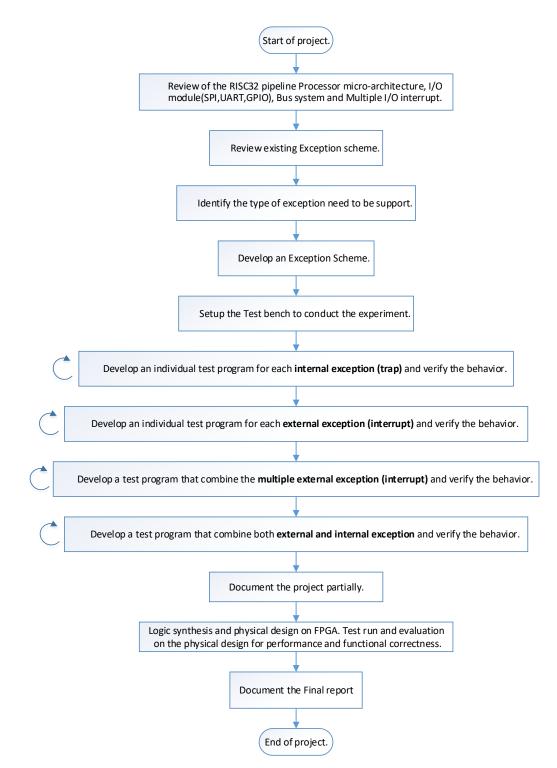

### 3.1 General Work Flow

The basic approach to develop an exception scheme is to identify type of the exception need to be support. After that, develop an Exception scheme that can handle multiple interrupt. Next, set up the test benches by using Verilog HDL to verify the exception scheme. Simple verification can done by trigger the I/Os interrupt and exception individually. After the IoT processor has passed through the individual test, a definitive exception-handling scheme can be derive from the combination of the various type of exception. If the scheme not functioning well, the exception scheme needs to redesign and go through the process again. If the scheme works correctly, then the work can be document. Next, the IoT processor is ready to synthesize onto an FPGA board for physical tests to conclude the earlier laid down experiments / tests. The Design Flow shown in Figure 3.1.

#### Chapter 3 Proposed Methods / Technologies Involved

Figure 3.1 Design flow of the project

# 3.2 Design Tools

Since this project will be using Verilog HDL to model the test bench to verify the functionality, we will be discussing commonly used design software that can support Verilog HDL. Some simulator are shows in Table 3.1:

| Simulator        | ModelSim        | VCS                              | Quartus II      |

|------------------|-----------------|----------------------------------|-----------------|

| Company          | Graphics        | SYNOPSYS*<br>Predictable Success |                 |

| Language         | VHDL-2002       | VHDL-2002                        | VHDL-2002       |

| Supported        |                 |                                  |                 |

|                  | V2001           | V2001                            | V2001           |

|                  |                 |                                  |                 |

|                  | SV2005          | SV2005                           | SV2005          |

| Platform         | -Windows        | Linux                            | -Windows XP/7/8 |

| Supported        | XP/Vista/7/8/10 |                                  | -Linux          |

|                  | -Linux          |                                  |                 |

| Availability for | YES (Student    | No                               | No              |

| free             | Edition only)   |                                  |                 |

Table 3.1 Comparison between simulation tools. (Mentor Graphics, n.d.), (Synopsys,n.d.), (Altera, n.d.).

Based on the comparison above, it is clear that ModelSim from Mentor Graphic is the best choice as a simulation tool for this project because they offer free license (180 days) for Student Edition. There will some limitation for the student edition but it is sufficient for this project. However, the other two simulation tools provide better feature compare to ModelSim but the price is too expensive, it is not affordable for a student. ModelSim also provided freely in the computer laboratory by Universiti Tunku Abdul Rahman.

#### Mentor Graphics ModelSim PE Student Edition 10.4a (Mentor Graphics, n.d.)

ModelSim PE Student Edition 10.4a is the latest version and it offers a free license for academic purpose. It supports VHDL and Verilog HDL designs but not mixed and it has a friendly GUI with TCL interface. Since it is free, so the free version has no customer support, but there are a lot of learning resources are available on the internet and a forum for discussion.

### PC Spim

PC Spim is a simulator that provides a MIPS environment to simulate MIPS programs. It supported almost the entire MIPS assembly language and a build-in simple debugger. In this project, the test code, boot loader, interrupt service routine and exception handler will write in MIPS assembly language and simulated with PC spim before load into the RISC32 IoT processor.

#### Xilinx Vivado Design Suite- HLx Editions (Xilinx.com, n.d.)

Xilinx Vivado used for synthesis and analysis of HDL designs. It allow the developer to synthesize their designs on to FPGA board, analysis RTL schematic diagrams, run the simulation, perform timing analysis, and load the bit stream to the target device. The FPGA board that used in this project is Arty A7: Artix-7 FPGA Development Board.

#### Arty A7: Artix-7 FPGA Development Board (Digilent, n.d.)

Arty is a ready-to-use development board and designed based on the Artix-7<sup>™</sup> FPGA from Xilinx. It contain 256MB DDR3L and 16MB Quad-SPI Flash. For peripheral, Arty supported by the UARTs, SPIs, IICs, and an Ethernet MAC. It also contain 4 Pmod connector for expansion the connection. There are also some interaction and sensory devices such as 4 Switches, 4 Buttons, 1 Reset Button, 4 LEDs and 4 RGB LEDs.

# 3.3 System Overview

The Figure 3.2 shown the block diagram of the IoT SoC Processor and Table 3.2 shown hardware features of the IoT SoC Processor

Figure 3.2 Block diagram of the IoT SoC Processor

| CPU Structure           | Pipeline                                         |

|-------------------------|--------------------------------------------------|

| Instruction cycle       | 5, overlapping                                   |

| CPU features            | Control unit                                     |

|                         | Data-path unit                                   |

|                         | Branch predictor (64 entries 4 ways associative) |

|                         | Pipeline registers                               |

|                         | Hazard circuitry                                 |

|                         | Interlock circuitry                              |

|                         |                                                  |

| Memory features         | 4kBytes boot ROM, 128kBytes user access flash,   |

|                         | 8kBytes RAM (Data & Stack), 1kBytes I-cache,     |

|                         | 32Bytes d-cache, 512Bytes Memory Mapped I/O      |

|                         | Register                                         |

| Communication interface | UART, SPI, 32 GPIO pins                          |

| features                |                                                  |

Table 3.2 Hardware features of the IoT SoC Processor

The figure above shows the system overview of this project. RISC32 IoT processor made up of 3 major part, which are, Central processing Unit (CPU), memory system and I/O System. The IoT processor based on pipeline architecture with build-in coprocessor 0 and Programmable interrupt controller to handle the exception. The CPU is compatible to the 5-stage 32-bit MIPS Instruction Set Architecture (ISA).

Memory unit will used to store the system code, user program and data. The I/O register mapped to the memory unit because I/O mapped technique used.

The I/O System of IoT Processor consist of SPI controller, GPIO controller, and UART controller. These controllers will responsible for data transmission between IoT processor and the external device, for example, sensors, wireless modules, personal computers.

The bus system will connect between CPU and I/O devices. Any data transmission between the CPU and the I/O device will pass through the bus system.

## 3.4 Timeline

Figure below show the Gantt chart for FYP 1 and FYP2.

| GANTT                                                       |            |          | 2018                        | 2019               |

|-------------------------------------------------------------|------------|----------|-----------------------------|--------------------|

| Name                                                        | Begin date | End date | May Jun Jul Aug Sep Oct Nov | Dec Jan Feb Mar Ap |

| Literature Review                                           | 5/28/18    | 7/6/18   | ,                           |                    |

| RISC32 pipeline Processor micro-architecture                | 5/28/18    | 6/11/18  |                             |                    |

| <ul> <li>I/O module (SPI, UART, and GPIO)</li> </ul>        | 6/12/18    | 6/21/18  |                             |                    |

| Bus system and Multiple I/O interrupt                       | 6/22/18    | 6/29/18  |                             |                    |

| <ul> <li>Existing exception scheme</li> </ul>               | 7/2/18     | 7/6/18   | 0                           |                    |

| Design and develop the Exception Scheme                     | 7/9/18     | 7/20/18  | ×                           |                    |

| Identify the type of exception need to be support.          | 7/9/18     | 7/9/18   | I                           |                    |

| Develop an Exception Scheme                                 | 7/9/18     | 7/20/18  |                             |                    |

| Verification for the Design by simulation                   | 7/23/18    | 8/3/18   | <b>T</b>                    |                    |

| Set up the Testing environment                              | 7/23/18    | 7/23/18  | 1                           |                    |

| Develop Test Program for                                    | 7/23/18    | 8/3/18   |                             |                    |

| <ul> <li>individual internal exception(trap)</li> </ul>     | 7/23/18    | 7/24/18  | 1                           |                    |

| individual external exception (interrupt)                   | 7/25/18    | 7/27/18  | 0                           |                    |

| <ul> <li>multiple external exception (interrupt)</li> </ul> | 7/30/18    | 8/2/18   | 0                           |                    |

| both external and internal exception                        | 8/3/18     | 8/3/18   | L                           |                    |

| Documentation and Presenntation FYP1                        | 8/6/18     | 8/31/18  |                             |                    |

| Document Final Year Project 1                               | 8/6/18     | 8/17/18  |                             |                    |

| Present Final Year Project 1                                | 8/20/18    | 8/31/18  |                             |                    |

| Logic synthesis and physical design on FPGA                 | 2/1/19     | 3/22/19  |                             | <b></b>            |

| Integration of the exception scheme to the RISC processor   | 2/1/19     | 2/27/19  |                             |                    |

| • Analysing the performance and functional correctness      | 2/11/19    | 3/22/19  |                             |                    |

| Documentation and Presenntation FYP1                        | 3/25/19    | 4/19/19  |                             |                    |

| <ul> <li>Document Final Year Project 2</li> </ul>           | 3/25/19    | 4/5/19   |                             |                    |

| Present Final Year Project 2                                | 4/8/19     | 4/19/19  |                             |                    |

Figure 3.3 Gantt chart For FYP1 and FYP2.

### **Chapter 4 System Specification**

#### 4.1 System Overview

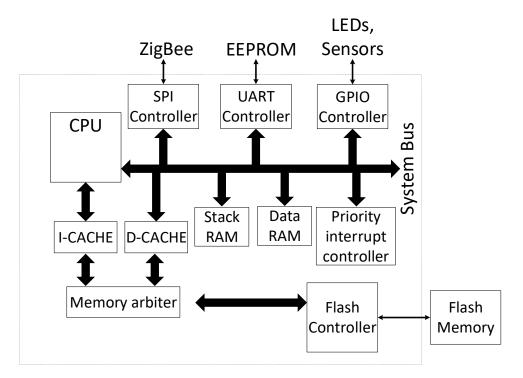

The IoT SoC processor is made up by 3 major parts, which are, Central Processing Unit (CPU), memory system and I/O system. The CPU is the subset of the 5-stage pipeline 32-bit MIPS Instruction Set Architecture (ISA). It supports up to 50 instructions, included arithmetic, logical, data transfer, program control and system instruction classes. The memory system consists of a 2-level memory hierarchy. First level consists of cache, Boot ROM and Data and Stack RAM and second level consists of Flash memory. The I/O system consists of GPIO controller, SPI controller, UART controller and Priority Interrupt controller. The I/O system integrated with CPU through Wishbone B4 standard bus interface (OpenCores, 2010). GPIO, SPI and UART controllers are used to data transfer with the external devices, for example, sensors, wireless modules, personal computers etc. The Priority Interrupt controller used as an external interrupt controller to handle multiple interrupt occurrences based on priority level. It collaborate with coprocessor 0 to handle the exception. Figure 4.1 shows the architecture of the IoT SoC Processor.

Figure 4.1: Architecture of the IoT SoC Processor.

| CPU Structure           | Pipeline                                         |

|-------------------------|--------------------------------------------------|

| Instruction cycle       | 5, overlapping                                   |

| CPU features            | Control unit                                     |

|                         | Data-path unit                                   |

|                         | Branch predictor (64 entries 4 ways associative) |

|                         | Pipeline registers                               |

|                         | Hazard circuitry                                 |

|                         | Interlock circuitry                              |

|                         |                                                  |

| Memory features         | 4kBytes boot ROM, 128kBytes user access flash,   |

|                         | 8kBytes RAM (Data & Stack), 1kBytes i-cache,     |

|                         | 32Bytes d-cache, 512Bytes Memory Mapped I/O      |

|                         | Register                                         |

| Communication interface | UART, SPI, 32 GPIO pins                          |

| features                |                                                  |

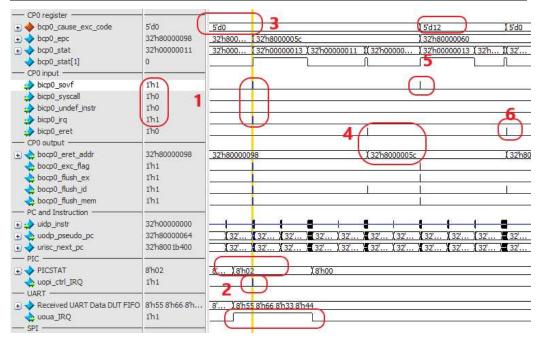

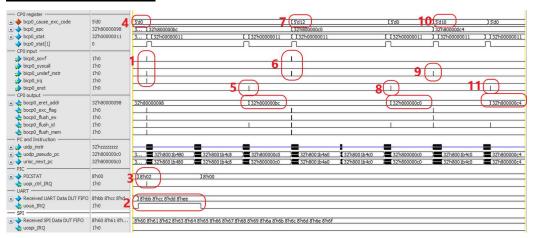

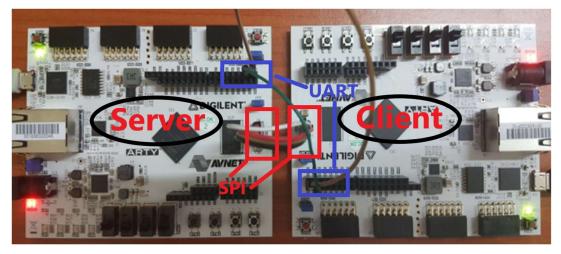

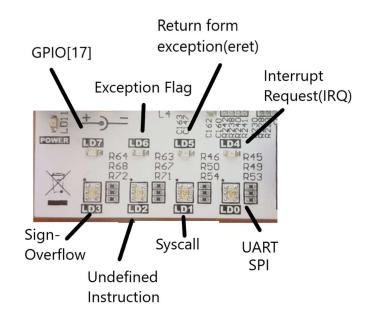

Table 4.1: Hardware features of the IoT SoC Processor.