# DESIGN OF A FLOATING POINT UNIT FOR 32-BIT 5 STAGE PIPELINE PROCESSOR

BY LOW WAI HAU

## A REPORT

SUBMITTED TO

Universiti Tunku Abdul Rahman in partial fulfillment of the requirements

for the degree of

BACHELOR OF COMPUTER ENGINEERING (HONS)

Faculty of Information and Communication Technology (Kampar Campus)

JAN 2020

## UNIVERSITI TUNKU ABDUL RAHMAN

## REPORT STATUS DECLARATION FORM

| Fitle: <u>Design of A Floa</u>       | ating Point Unit for 32-Bit 5 Stage Pipeline          |

|--------------------------------------|-------------------------------------------------------|

| Processor                            |                                                       |

| Aca                                  | ademic Session: JAN 2020                              |

|                                      | LOW WAI HAU                                           |

|                                      | (CAPITAL LETTER)                                      |

| declare that I allow this Final Year | Project Report to be kept in                          |

| Universiti Tunku Abdul Rahman I      | Library subject to the regulations as follows:        |

| 1. The dissertation is a property    | of the Library.                                       |

| 2. The Library is allowed to mak     | se copies of this dissertation for academic purposes. |

| LOW WAI HAU (Author's signature)     | Verified by, (Supervisor's signature)                 |

|                                      | (10)                                                  |

| Address:                             |                                                       |

| 1059, Jalan Seksyen 1/1,             |                                                       |

| Bandar Barat,                        | MOK KAI MING                                          |

| ,                                    |                                                       |

| 31900 Kampar.                        | Supervisor's name                                     |

|                                      | Supervisor's name  Date: 24 April 2020                |

# DESIGN OF A FLOATING POINT UNIT FOR 32-BIT 5 STAGE PIPELINE PROCESSOR

BY LOW WAI HAU

# A REPORT

SUBMITTED TO

Universiti Tunku Abdul Rahman

in partial fulfillment of the requirements

for the degree of

BACHELOR OF COMPUTER ENGINEERING (HONS)

Faculty of Information and Communication Technology (Kampar Campus)

JAN 2020

#### **DECLARATION OF ORIGINALITY**

I declare that this report entitled "**DESIGN OF A FLOATING POINT UNIT FOR 32-BIT 5 STAGE PIPELINE PROCESSOR**" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other reward.

Signature : LOW WAI HAU

Name : <u>LOW WAI HAU</u>

Date : <u>24 APRIL 2020</u>

#### ACKNOWLEDGEMENTS

First of all, I would like express deepest gratitude to my supervisor, Mr. Mok Kai Ming who has been providing me guidance with patience throughout the planning and development of this project.

I would also like to thank my family members for the support and encouragement throughout my undergraduate years. Nevertheless, I would like to thank all my fellow course mates and friends who supported me throughout the entire course of this project. All the supports and helps contribute to the accomplishment of this project.

#### **ABSTRACT**

This project is about the design of a Floating Point Unit (FPU), integrate the FPU into RISC32 processor and synthesize the FPU design on Field Programmable Gate Array (FPGA). The standalone FPU has been modeled by a senior student in Universiti Tunku Abdul Rahman, Liu Hing Yun. However, there was no integration test made on the FPU to the processor and the aforesaid FPU can only perform operation on single precision numbers. Hence, this project is required to develop a FPU which can perform operation on both single and double precision numbers.

The development project will start by studying the algorithm of addition on floating point numbers. The addition algorithm is then implemented in the FPU so that the FPU can perform addition on floating point numbers. Also, a dedicated register file is developed for FPU to store 32-bits or 64-bits of data.

This project will use top down design methodology: system specification, architecture level and microarchitecture level development. Microarchitecture level will perform unit partitioning of the system and block partitioning of the units. RTL modelling using Verilog will be performed on each block following the units and eventually the complete system. Verification will be made to determine functionality correctness of FPU.

The project will integrate the FPU into the RISC32 pipeline processor and the verification will be carried out to prove the functionality of FPU. In the end of this project, the FPU will be synthesized on FPGA.

## TABLE OF CONTENTS

| TITLE PAGE                                                  | i   |

|-------------------------------------------------------------|-----|

| DECLARATION OF ORIGINALITY                                  | ii  |

| ACKNOWLEDGEMENTS                                            | iii |

| ABSTRACT                                                    | iv  |

| TABLE OF CONTENTS                                           | v   |

| LIST OF FIGURES                                             | ix  |

| LIST OF TABLES                                              | xi  |

| LIST OF ABBREVIATIONS                                       | xii |

| CHAPTER 1: INTRODUCTION                                     | 1   |

| 1-1 Background Information                                  | 1   |

| 1-1-1 Floating Point Unit                                   | 1   |

| 1-1-2 MIPS                                                  | 2   |

| 1-2 Motivation and Problem Statement                        | 3   |

| 1-2-1 Motivation                                            | 3   |

| 1-2-2 Problem Statement                                     | 4   |

| 1-3 Project Scope                                           | 5   |

| 1-4 Project Objectives                                      | 5   |

| 1-5 Impact, Significance and Contribution                   | 5   |

| 1-6 Report Organization                                     | 6   |

| CHAPTER 2 LITERATURE REVIEW                                 | 7   |

| 2-1 Previous Works Done by Other Engineers/Researchers      | 7   |

| 2-2 Floating Point Number                                   | 10  |

| 2-2-1 Single Precision Floating Point Number Representation | 11  |

| 2-2-2 Double Precision Floating Point Number Representation | 11  |

| 2-3 Rounding                                                | 12  |

| 2-4 Arithmetic on Floating Point Numbers                    | 13  |

| 2-4-1 Addition operation                                    | 13  |

| 2-5 Floating Point Pipeline                                 | 15  |

| CHAPTER 3: PROPOSED METHOD AND APPROACH                     | 17  |

| 3-1 Design Methodology                                      | 17  |

| 3-1-1 Micro-Architecture Specification                      | 18  |

|                                                             | V   |

| 3-1-2 RTL Modeling and Verification                                          | 18 |

|------------------------------------------------------------------------------|----|

| 3-2 Design Tools                                                             | 19 |

| 3-2-1 ModelSim                                                               | 19 |

| 3-2-2 PC Spim                                                                | 20 |

| 3-2-3 Xilinx Vivado                                                          | 20 |

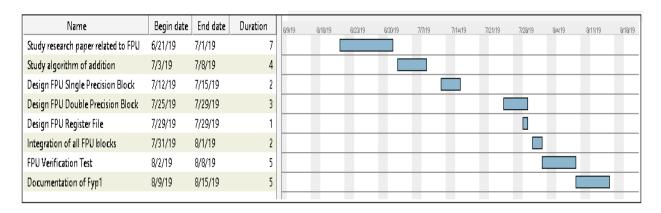

| 3-3 Grantt Chart                                                             | 20 |

| CHAPTER 4 SYSTEM SPECIFICATION                                               | 21 |

| 4-1 System Feature                                                           | 21 |

| 4-1-1 System Functionality                                                   | 22 |

| 4-2 Operating Procedure                                                      | 23 |

| 4-3 Naming Convention                                                        | 23 |

| 4-4 System Interface                                                         | 24 |

| 4-4-1 Input Pin Description                                                  | 24 |

| 4-4-2 Output Pin Description                                                 | 25 |

| 4-5 Memory Map                                                               | 26 |

| 4-5-1 Memory Map Description                                                 | 28 |

| 4-6-1 General Purpose Register                                               | 29 |

| 4-6-2 Special Purpose Register                                               | 29 |

| 4-6-3 Program Counter Register                                               | 30 |

| 4-6-4 CP0 Register                                                           | 30 |

| 4-6-5 FP Register                                                            | 30 |

| 4-7 Instruction Formats and Addressing Modes                                 | 31 |

| 4-7-1 Basic Instruction Formats                                              | 31 |

| 4-7-2 FP Instruction Formats                                                 | 31 |

| 4-7-3 Addressing Modes                                                       | 32 |

| 4-8 Supported Instructions Set                                               | 36 |

| CHAPTER 5: MICROARCHITECTURE SPECIFICATION                                   | 39 |

| 5-1 Design Hierarchy and Partitioning.                                       | 39 |

| 5-2 Microarchitecture of RISC32 processor                                    | 42 |

| 5-2-1 Interface of FP Register File and Extended Pipeline with Datapath Unit | 43 |

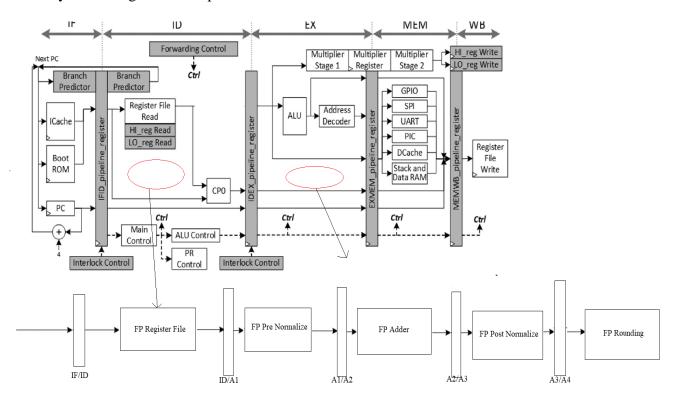

| 5-3 Datapath Unit                                                            | 44 |

| 5-3-1 Datapath Unit Interface                                                | 44 |

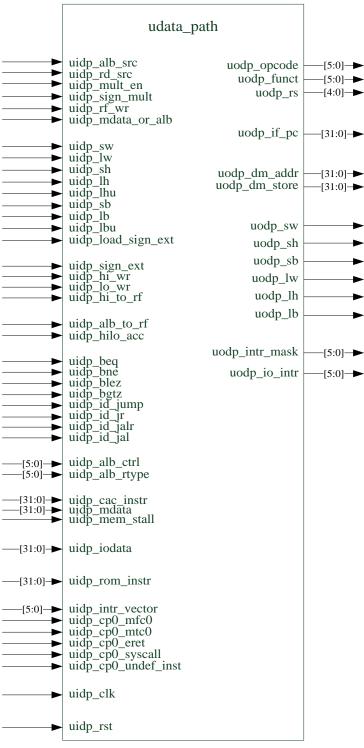

| 5-3-2 FPU Register File Block                    | 45 |

|--------------------------------------------------|----|

| 5-3-2-1 Functionality                            | 45 |

| 5-3-2-2 FPU Register File Block Interface        | 45 |

| 5-3-2-3 Input Pin Description                    | 46 |

| 5-3-2-4 Output Pin Description                   | 47 |

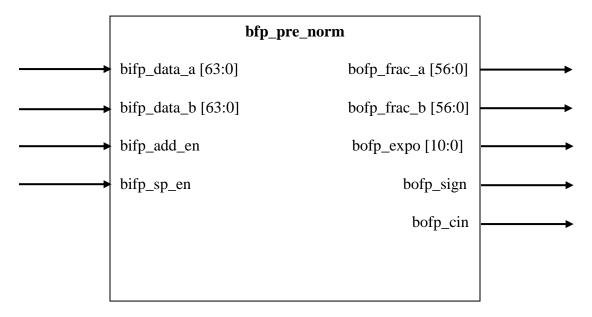

| 5-3-3 FP Pre Normalize Block                     | 48 |

| 5-3-3-1 Functionality                            | 48 |

| 5-3-3-2 FP Pre Normalize Block Interface         | 48 |

| 5-3-3-3 Input Pin Description                    | 49 |

| 5-3-3-4 Output Pin Description                   | 49 |

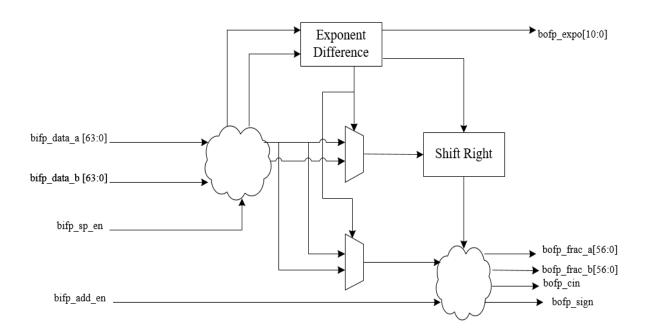

| 5-3-3-5 FP Pre Normalize Internal Block Diagram  | 50 |

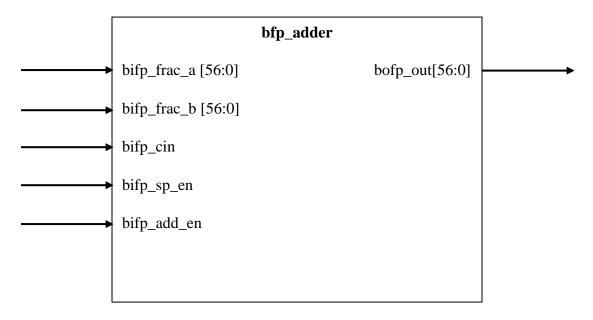

| 5-3-4 FP Adder Block                             | 51 |

| 5-3-4-1 Functionality                            | 51 |

| 5-3-4-2 FP Adder Block Interface                 | 51 |

| 5-3-4-3 Input Pin Description                    | 52 |

| 5-3-4-4 Output Pin Description                   | 52 |

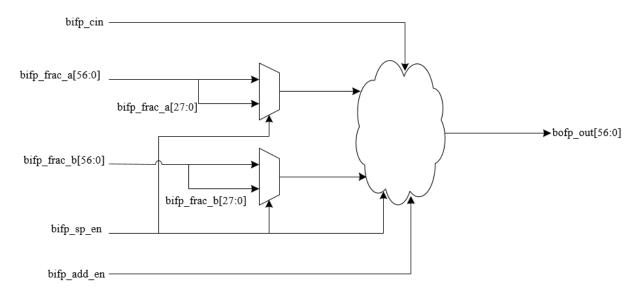

| 5-3-4-5 FP Adder Internal Block Diagram          | 53 |

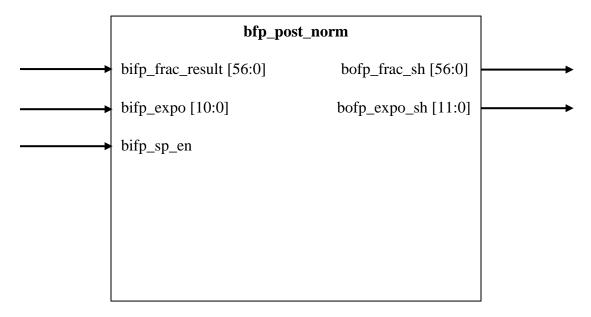

| 5-3-5 FP Post Normalize Block                    | 54 |

| 5-3-5-1 Functionality                            | 54 |

| 5-3-5-2 FP Post Normalize Block Interface        | 54 |

| 5-3-5-3 Input Pin Description                    | 55 |

| 5-3-5-4 Output Pin Description                   | 55 |

| 5-3-5-5 FP Post Normalize Internal Block Diagram | 56 |

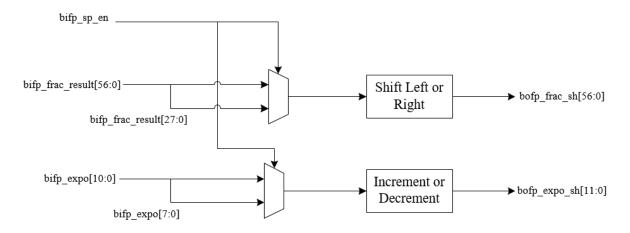

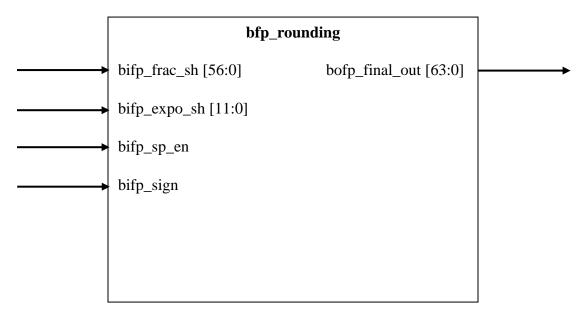

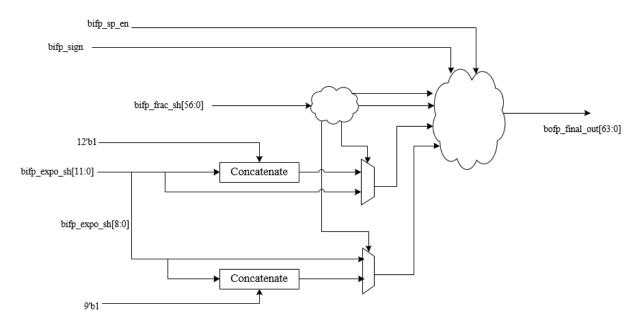

| 5-3-6 FP Rounding Block                          | 57 |

| 5-3-6-1 Functionality                            | 57 |

| 5-3-6-2 FP Rounding Block Interface              | 57 |

| 5-3-6-3 Input Pin Description                    | 58 |

| 5-3-6-4 Output Pin Description                   | 58 |

| 5-3-6-5 FP Rounding Block Internal Diagram       | 59 |

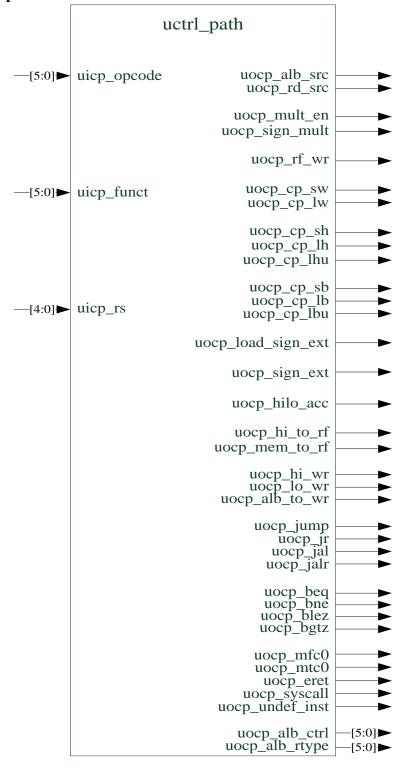

| 5-4 Controlpath Unit                             | 60 |

| 5-4-1 Controlpath Unit Interface                 | 60 |

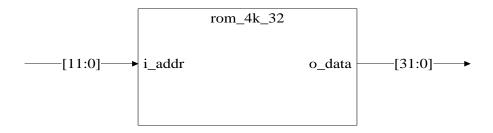

| 5-5 Rom Unit                                     | 61 |

| 5-5-1 Rom Unit Interface                                               | 61 |

|------------------------------------------------------------------------|----|

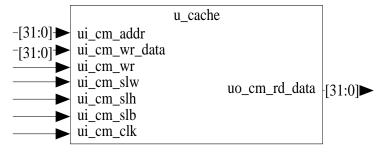

| 5-6 Memory Unit                                                        | 61 |

| 5-6-1 Memory Unit Interface                                            | 61 |

| 5-6-2 Memory Unit Mapping                                              | 62 |

| CHAPTER 6: VERIFICATION SPECIFICATION                                  | 63 |

| 6-1 Test Plan for FPU                                                  | 63 |

| 6-2 Simulation Result for FPU                                          | 65 |

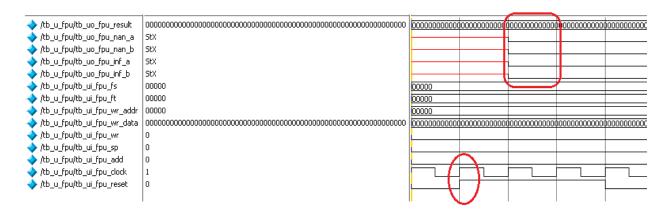

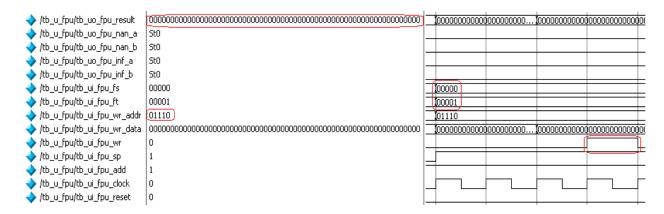

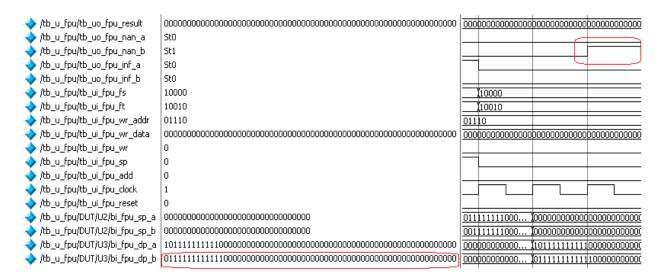

| 6-2-1 Test Case #1: Reset                                              | 65 |

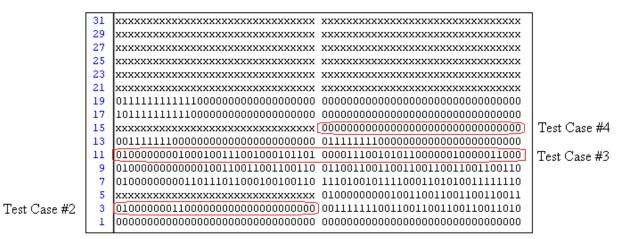

| 6-2-2 Test Case #2: Addition function test on single precision numbers | 65 |

| 6-2-3 Test Case #3: Addition function test on double precision numbers | 66 |

| 6-2-4 Test Case #4: Addition function test on all zero numbers         | 66 |

| 6-2-5 Test Case #5: Infinity inputs test                               | 67 |

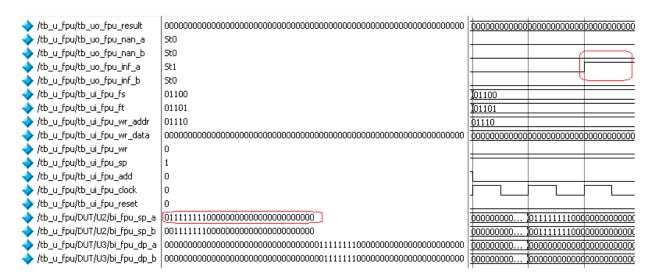

| 6-2-6 Test Case #5: NaN inputs test                                    | 67 |

| 6-3 FP Register File Contents                                          | 68 |

| 6-4 Test Bench for FPU                                                 | 69 |

| 6-5 FP Integration with RISC32                                         | 72 |

| 6-5-1 Test Program                                                     | 72 |

| 6-5-2 Simulation Result                                                | 73 |

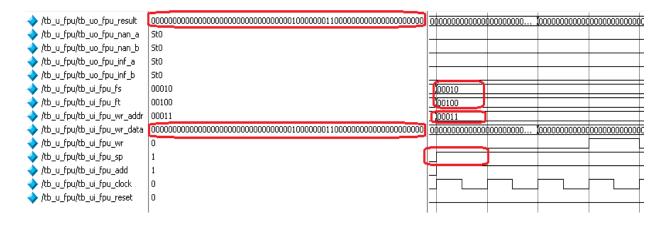

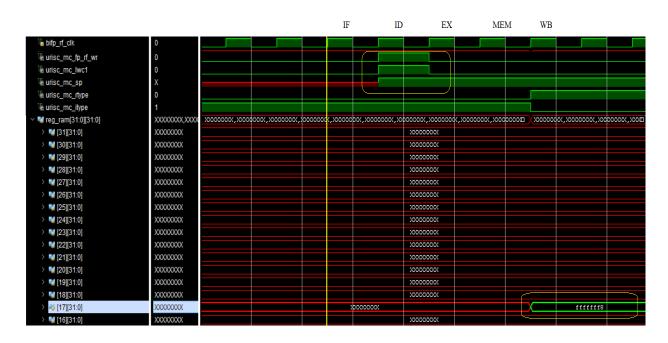

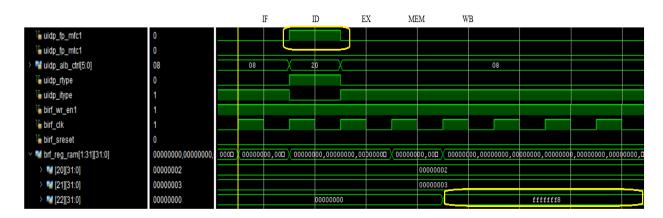

| 6-5-2-1 Test Case #1: lwc1 instruction                                 | 73 |

| 6-5-2-2 Test Case #1: swc1 instruction                                 | 73 |

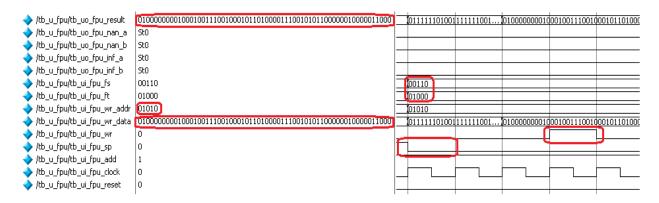

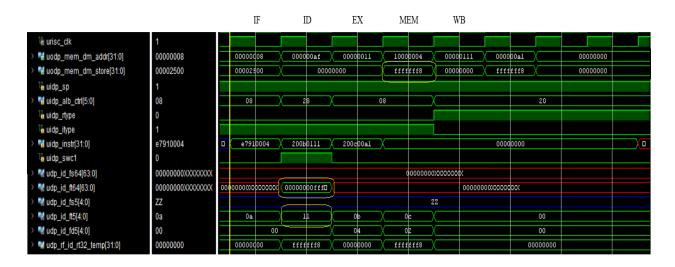

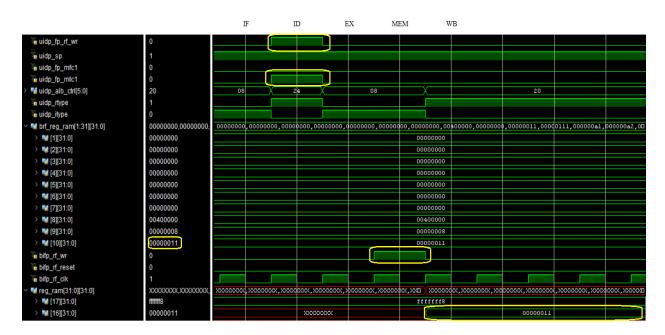

| 6-5-2-3 Test Case #3: mfc1 instruction                                 | 74 |

| 6-5-2-4: Test Case #3: mtc1 instruction.                               | 75 |

| 6-5-3 Test Bench                                                       | 76 |

| CHAPTER 7: CONCLUSION                                                  | 82 |

| BIBLIOGRAPHY                                                           | 83 |

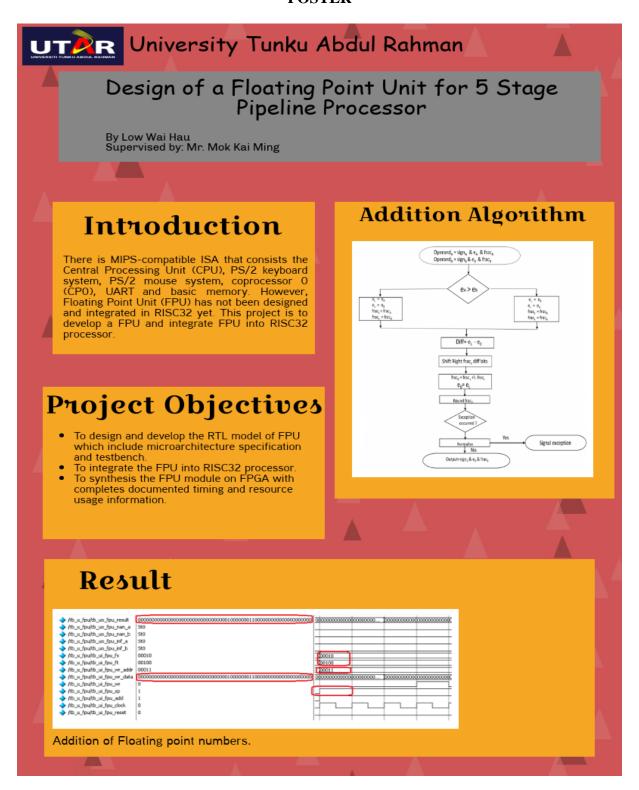

| POSTER                                                                 | 85 |

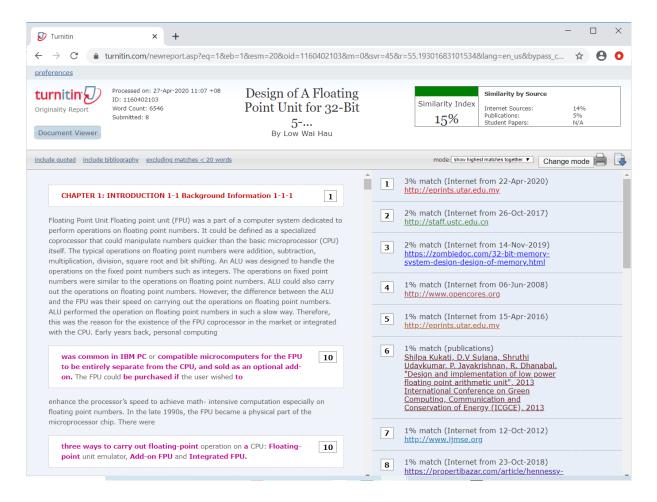

| PLAGIARISM CHECK RESULT                                                |    |

| CHECK LIST                                                             |    |

## LIST OF FIGURES

| Figure 1-1-2-F1: MIPS 5-stage pipeline (Mok, 2008, p.9)                                 | 2     |

|-----------------------------------------------------------------------------------------|-------|

| Figure 1-2-2-F1: RISC32 Microarchitecture (FPU not implemented on datapath unit)        | 4     |

| Figure 2-1-F1: Carry save adder (Kukati et al. 2013)                                    | 9     |

| Figure 2-2-1-F1: Single precision floating point number representation.                 | 11    |

| Figure 2-2-2-F1: Double precision floating point number representation                  | 12    |

| Figure 2-4-1-F1: Algorithm of addition operation                                        | 14    |

| Figure 2-5-F1: Latencies and initiation intervals for functional units                  | 15    |

| Figure 2-5-F1: Extended Pipeline for FP                                                 | 15    |

| Figure 3-1-F1: Top-down design methodology.                                             | 17    |

| Figure 3-3-F1: Grantt Chart of Project.                                                 | 20    |

| Figure 4-4-F1: Block diagram of RISC32 processor.                                       | 24    |

| Figure 4-5-F1: Memory Map                                                               | 27    |

| Figure 4-7-1-F1: Instruction Format                                                     | 31    |

| Figure 4-7-2-F1: FP Instruction Format                                                  | 31    |

| Figure 4-7-3-F1: R-format Addressing                                                    | 32    |

| Figure 4-7-3-F2: Immediate Addressing                                                   | 32    |

| Figure 4-7-3-F3: Based Displacement Addressing                                          | 33    |

| Figure 4-7-3-F4: Based Displacement Addressing with FP Register File (Used by lwc1, swc | 1) 33 |

| Figure 4-7-3-F5: PC-Relative Addressing                                                 | 34    |

| Figure 4-7-3-F6: Pseudo-Direct Addressing                                               | 34    |

| Figure 4-7-3-F7: Register Addressing for FR format (Used by add.s, add.d)               | 35    |

| Figure 4-7-3-F8: Register Addressing for FR format (Used by FP branching instructions)  | 35    |

| Figure 5.1-F1: Block Partitioning                                                       | 41    |

| Figure 5-2-F1: Microarchitecture of RISC32 processor                                    | 42    |

| Figure 5-2-1-F1: Interface of FP Register File and Extended Pipeline with Datapath Unit | 43    |

| Figure 5-3-1-F1: Datapath Unit Interface                                                | 44    |

| Figure 5-3-2-2-F1: Block Interface of FPU Register File                                 | 45    |

| Figure 5-3-3-2-F1: Block Interface of FP Pre Normalize Block                            | 48    |

| Figure 5-3-3-5-F1 FP Pre Normalize Internal Block Diagram                               | 50    |

|                                                                                         | ix    |

| Figure 5-3-4-2-F1 Block Interface of FP Adder Block           | 51 |

|---------------------------------------------------------------|----|

| Figure 5-3-4-5-F1 FP Adder Internal Block Diagram             | 53 |

| Figure 5-3-5-2-F1: Block Interface of FP Post Normalize Block | 54 |

| Figure 5-3-5-F1 FP Post Normalize Internal Block Diagram      | 56 |

| Figure 5-3-6-2-F1: Block Interface of FP Rounding Block       | 57 |

| Figure 5-3-6-5-F1 FP Rounding Internal Block Diagram          | 59 |

| Figure 5-4-1-F1: Controlpath Unit Interface                   | 60 |

| Figure 5-5-1-F1: Rom Unit Interface                           | 61 |

| Figure 5-6-1-F1: Memory Unit Interface                        | 61 |

| Figure 6-2-1-F1: Simulation result for test case #1.          | 65 |

| Figure 6-2-2-F1: Simulation result for test case #2.          | 65 |

| Figure 6-2-3-F1: Simulation result for test case #3.          | 66 |

| Figure 6-2-4-F1: Simulation result for test case #4.          | 66 |

| Figure 6-2-5-F1: Simulation result for test case #5.          | 67 |

| Figure 6-2-6-F1: Simulation result for test case #6.          | 67 |

| Figure 6-3-F1: FP register file contents                      | 68 |

| Figure 6-5-2-1-F1: Simulation result of test case #1(lwc1).   | 73 |

| Figure 6-5-2-2-F1: Simulation result of test case #1(swc1).   | 74 |

| Figure 6-5-2-3-F1: Simulation result of test case #3(mfc1).   | 74 |

| Figure 6-5-2-4-F1: Simulation result of test case #3(mtc1)    | 75 |

## LIST OF TABLES

| Table 2-1-T1: Number of clock cycles for each arithmetic operation (Al-Eryani 2006)       | 8    |

|-------------------------------------------------------------------------------------------|------|

| Table 2-1-T2: Number of clock cycles for each arithmetic operation.                       | 8    |

| Table 3-2-1-T1: Comparison between simulation tools.                                      | . 19 |

| Table 4-1-F1 RISC32 Features                                                              | . 21 |

| Table 4-3-T1: Naming convention                                                           | . 23 |

| Table 4-4-1-T1: Input pin description of RISC32 chip.                                     | . 25 |

| Table 4-4-2-T1: Output pin description of RISC32 chip.                                    | . 25 |

| Table 4-5-T1: Memory Map                                                                  | . 26 |

| Table 4-5.1-T1: Memory Map Description                                                    | . 28 |

| Table 4-6-1-T1: General Purpose Registers                                                 | . 29 |

| Table 4-6-2-T1: Special Purpose Register                                                  | . 29 |

| Table 4-6-4-T1: CP0 Register                                                              | . 30 |

| Table 4-6-5-T1: FP Register                                                               | . 30 |

| Table 4-7-1-T1: Instruction Format Definition                                             | . 31 |

| Table 4-8-T1: Supported Instruction Set                                                   | . 38 |

| Table 5-1-T1: Design Hierarchy of RISC32 Processor with FP Register File, FP Pre-Normaliz | ze,  |

| FP Adder, FP Post-Normalize and FP Rounding                                               | . 40 |

| Table 5-3-2-3-T1: Input Pin Description of FPU Register File                              | . 46 |

| Table 5-3-2-4-T1: Output Pin Description of FPU Register File                             | . 47 |

| Table 5-3-3-T1: Input Pin Description of FP Pre Norm Block                                | . 49 |

| Table 5-3-4-T1: Output Pin Description of FP Pre Norm Block                               | . 49 |

| Table 5-3-4-2-T1: Input Pin Description of FP Adder Block                                 | . 52 |

| Table 5-3-4-4-T1: Output Pin Description of FP Adder Block                                | . 52 |

| Table 5-3-5-3-T1: Input Pin Description of FP Post Norm Block                             | . 55 |

| Table 5-3-5-4-T1: Output Pin Description of FP Post Norm Block                            | . 55 |

| Table 5-3-6-3-T1: Input Pin Description of FP Rounding Block                              | . 58 |

| Table 5-3-6-4-T1: Output Pin Description of FP Rounding Block                             | . 58 |

| Table 5-6-2-T1: Memory Unit mapping and its content description                           | . 62 |

| Table 6-1-T1: Test Plan of FPU                                                            | . 64 |

|                                                                                           | vi   |

#### LIST OF ABBREVIATIONS

ALU Arithmetic Logic Unit

FPU Floating Point Unit

CPU Central Processing Unit

MIPS Microprocessor without Interlocked Pipelined Stages

VHDL VHSIC Hardware Description Language

RISC Reduced Instruction Set Computer

VHDL VHSIC Hardware Description Language

FPGA Field Programmable Gate Array

**CHAPTER 1: INTRODUCTION**

**CHAPTER 1: INTRODUCTION**

1-1 Background Information

1-1-1 Floating Point Unit

Floating point unit (FPU) was a part of a computer system dedicated to carry out operations

on floating point numbers. It could be defined as a specialized coprocessor that could manipulate

numbers quicker than the basic microprocessor (CPU) itself. The typical operations on floating

point numbers were addition, subtraction, multiplication, division, square root and bit shifting. An

ALU was designed to handle the operations on the fixed point numbers such as integers. The

operations on fixed point numbers were similar to the operations on floating point numbers. ALU

could also carry out the operations on floating point numbers. However, the difference between

the ALU and the FPU was their speed on carrying out the operations on floating point numbers.

ALU performed the operation on floating point numbers in such a slow way. Therefore, this was

the reason for the existence of the FPU coprocessor in the market or integrated with the CPU.

Early years back, personal computing was common in IBM PC or compatible

microcomputers for the FPU to be entirely separate from the CPU, and sold as an optional add-on.

The FPU could be purchased if the user wished to enhance the processor's speed to achieve math-

intensive computation especially on floating point numbers. Starting with the Intel Pentium and

Motorola 68000 series in the late 1990s, the FPU became a physical part of the microprocessor

chip.

When a CPU was executing a program that called for a floating-point operation, there were

three ways to carry it out: Floating-point unit emulator, Add-on FPU and Integrated FPU. FPU

could support the following arithmetic operations that is addition, subtraction, multiplication,

division and square root. The supported rounding modes for each operation are round to nearest

even, round to zero, round up and round down.

1

#### 1-1-2 MIPS

MIPS also known as Microprocessor without Interlocked Pipelined Stage, which based on the Reduced Instruction Set Computer (RISC) architecture was developed by a team led by John L. Hennessy and David A. Patterson. MIPS Technologies, formerly known as MIPS Computer System Inc. was co-founded at 1984 by John L. Hennessy. The MIPS architecture could be found in the book called Computer Organization and Design: The Hardware/ Software Interface (Patterson and Hennessy, 2005). This book showed the architecture of MIPS, the instruction sets, pinelined stages, just to name a few and how to build a microprocessor. MIPS processors operated by breaking instruction execution into multiple small independent "stages" and since the stages were independent, multiple instructions could be in varying stages of completion at any one time (Integrated Device Technology. Inc, 1994, p.1-2).

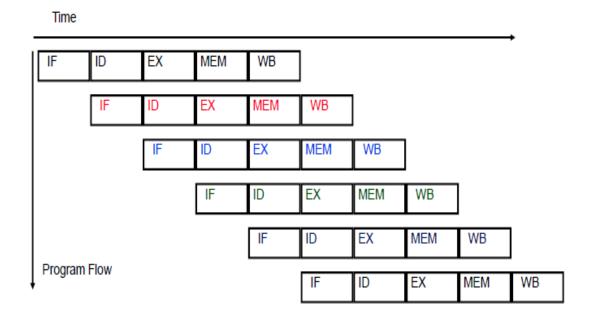

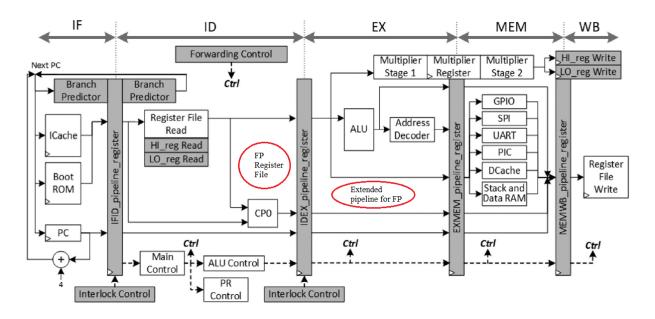

Figure 1-1-2-F1: MIPS 5-stage pipeline (Mok, 2008, p.9).

The instruction execution cycle was divided to 5 stages, IF ("Instruction Fetch"), ID ("Instruction Decode and Registers Fetch"), EX ("Execute"), MEM ("Memory") and WB ("Write Back").

- IF: Instruction Fetch and update PC.

- ID: Decodes the instruction and fetches the contents of any CPU registers it uses.

**CHAPTER 1: INTRODUCTION**

• EX: Execute R-type, calculate memory address.

• MEM: Read/write the data from/to the Data Memory.

• WB: Write the result data into the register file.

1-2 Motivation and Problem Statement

1-2-1 Motivation

A 32-bit pipelined RISC microprocessor has been developed in Faculty of Information and

Communication Technology, Universiti Tunku Abdul Rahman (UTAR) using Verilog which is a

hardware description language (HDL). The project is based on the Reduced Instruction Set

Computing (RISC) architecture. The motivations to initiate the project are due to following

reasons:

Microchip design companies designed microprocessor as Intellectual Property or IP for

commercial purpose. The microprocessor IP contains information on the entire design

process for the front-end (modeling and verification) to back-end (physical design)

integrated circuit (IC) design. These are trade secrets of a company and certainly not made

available in the market at an affordable price for research purpose.

Several freely available microprocessor cores can be found in internet, most of them can

be found at OpenCores (http://www.opencores.org/). Unfortunately, these processors do

not implement the entire MIPS Instruction Set Architecture (ISA) and lack of

comprehensive documentation which is hard to be understand.

• The verification specification for a freely available RISC microprocessor core that is

available on the Internet is not well developed and it is incomplete. Thus design process

will be slowed down without a complete verification specification.

• The lack of well-developed verification specifications for these microprocessor cores will

affect the physical design phase. A design needs to be functionally proven before the

physical design phase can proceed smoothly. Otherwise, if the front-end design has to be

changed, the physical design process has to be redone.

3

#### 1-2-2 Problem Statement

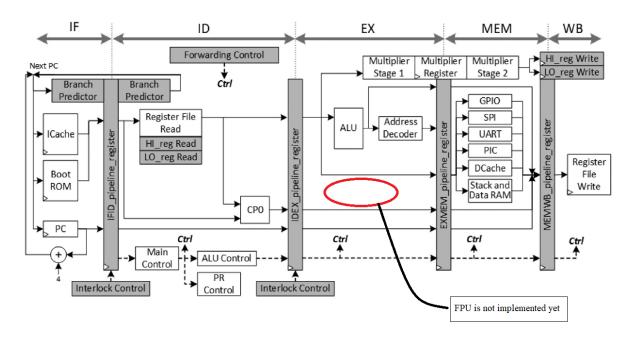

So far, there is MIPS-compatible ISA which includes the Central Processing Unit (CPU), PS/2 mouse system, PS/2 keyboard system, basic memory, coprocessor 0 (CP0), and Universal Asynchronous Receiver/Transmitter (UART). However, Floating Point Unit (FPU) has not been designed and integrated in RISC32 yet. In general, although ALU could perform operations on floating point numbers, it was considered slow to meet the expectation. Hence, this project is initiated to design a floating point unit and then integrate it into RISC32 processor.

Figure 1-2-2-F1: RISC32 Microarchitecture (FPU not implemented on datapath unit).

**CHAPTER 1: INTRODUCTION**

1-3 Project Scope

This project is to design a FPU model with Verilog for RISC32 processor. The

specifications of FPU and its internal blocks will be developed. The functionality of the FPU will

be verified by using test bench. The FPU will be integrated into existing available RISC32

processor and verification will be done to ensure it is working. Lastly, the FPU will be synthesis

on FPGA.

1-4 Project Objectives

Here are the objectives of the project:

• To design and develop the RTL model of FPU which include microarchitecture

specification and testbench.

To integrate the FPU into RISC32 processor.

• To synthesis the FPU module on FPGA with completes documented timing and resource

usage information.

1-5 Impact, Significance and Contribution

In short, there is lacking of well-developed FPU based development environment out there.

The development environment referred to the availability of the following:

• A well-developed design documentation of chip specification, architecture specification

and micro-architecture specification from top level to bottom level.

• A fully functional well-developed FPU integrated into RISC32 processor in the form of

synthesis-ready RTL written in Verilog.

• A well-developed verification specification of the FPU. The verification specification

should contain complete verification methodology and its techniques as well as test plan,

test bench architecture etc.

5

**CHAPTER 1: INTRODUCTION**

• A complete physical design in FPGA with documented timing and resources usage

information.

This project is to develop an environment that mentioned above: to integrate the RISC32 processor

core-based platform with the FPU which could support hardware modeling research work.

1-6 Report Organization

This report contains 7 chapters. The chapters are Chapter 1 Introduction, Chapter 2 Literature

Review, Chapter 3 Methodology, Chapter 4 System Specification, Chapter 5 Microarchitecture

Specification, Chapter 6 Verification Specification, Chapter 7 Conclusion.

Chapter 1 Introduction states the motivation for the project, following by problem statement,

project scope and objective and the background information of FPU and MIPS.

Chapter 2 Literature Review explains about the information related to FPU such as floating point

number and format, single and double precision as well as arithmetic of floating point number. In

this chapter, a previously developed FPU is also reviewed regarding its design.

Chapter 3 Methodology discuss about the flow of how the project is conducted. Proposed solution

is also documented at this chapter.

Chapter 4 System design gives the overview of the system on the top level and the naming

convention used within the system

Chapter 5 Microarchitecture Specification contains the units or components involved in the system

design. This chapter identifies each unit involved in the system and gives an overview about each

unit. Also contains the detailed discussion and design for each unit.

Chapter 6 Verification Specification shows the test written to verify the integration of the system.

Result of the verification test is also documented here.

Chapter 7 Conclusion concludes the overall project development.

6

#### 2-1 Previous Works Done by Other Engineers/Researchers

Since ALU performed floating point operations slower in term of speed, FPU came to existence to speed up the mathematical operations of floating point numbers. FPU this project had been done by a couple of engineers before. For instance, according to Al-Eryani (2006), he used VHDL language to model the 32-bit floating point unit which complies fully with the IEEE 754 Standard.

From his project, the proposed FPU was able to support some arithmetic operations such as addition, subtraction, multiplication, division and square root. All arithmetic operations had these three stages:

- 1. Pre-normalize: The operands were transformed into formats that makes them easy and efficient to handle internally.

- 2. Arithmetic core: The basic arithmetic operations were done here.

- 3. Post-normalize: The result would be normalized if possible (leading bit before decimal point is 1, if possible) and then transformed into the format specified by the IEEE standard (Al-Eryani 2006).

Besides, the FPU also able to perform four rounding modes which were rounding to nearest even, to zero, rounding up and down. The FPU was tested with test cases created using SoftFloat which was a software implementation of floating-point that conforms to the IEC/IEEE Standard for Binary Floating-Point Arithmetic. Moreover, the FPU was tested in ModelSim with 100,000 test cases for each arithmetic operation and for each rounding mode. As a result, an FPU with features of 100 MHz operating frequency, few clock cycles and logic elements was implemented.

However, the FPU that done by him could only support single precision format floating point numbers. In addition, in order for the FPU to achieve high frequency, the FPU had to trade off its clock cycles in which it required more pipelining. The number of clock cycles that the FPU needs for each arithmetic operation was listed below:

| Operation      | Number of clock cycles |  |

|----------------|------------------------|--|

| Addition       | 7                      |  |

| Subtraction    | 7                      |  |

| Multiplication | 12                     |  |

| Division       | 35                     |  |

| Square-root    | 35                     |  |

Table 2-1-T1: Number of clock cycles for each arithmetic operation (Al-Eryani 2006).

On the other hand, Lundgren (2014) also used VHDL to model double precision floating point core. By using double precision format, it could represented a wider range of numeric values. This core was designed to meet the IEEE 754 standard for double precision floating point arithmetic. This unit had been extensively simulated, covering all four operations (add, subtract, multiply, divide), rounding modes, exceptions like underflow and overflow, and even the obscure corner cases, like when overflowing from denormalized to normalized, and vice-versa. The floating point unit supports denormalized numbers, 4 operations, and 4 rounding modes (nearest, zero, + infinity, - infinity). The unit was synthesized with an estimated frequency of 185 MHz, for a Virtex5 target device.

| Operation      | Number of clock cycles |

|----------------|------------------------|

| Addition       | 20                     |

| Subtraction    | 21                     |

| Multiplication | 24                     |

| Division       | 71                     |

Table 2-1-T2: Number of clock cycles for each arithmetic operation.

The floating point unit he developed supported denormalized numbers which required more signals and logic levels to accommodate gradual underflow. The supported clock speed of 185 MHz makes up for the large number of clock cycles required for each operation to complete which led to longer latency as it required more logic levels.

Apart from that, floating point numbers required costly processing hardware or lengthy software implementations as it had larger range of values. Therefore, powerful computations and techniques which reduced hardware and improved the performance like power, area and timing was required. This concern led Kukati et al. (2013) designed a 32-bit floating point arithmetic unit with faster carry save adders and clock gating techniques to reduce power dissipation. The low power optimizing technique 'Multi Threshold Voltage' is used for reducing the power consumption of the arithmetic unit. Below was their proposed hardware:

Figure 2-1-F1: Carry save adder (Kukati et al. 2013).

Figure 2-1-F1 shows the data flow of the computation of two floating point numbers. The arithmetic operation flow will be discussed later in this chapter.

#### 2-2 Floating Point Number

There were several ways to represent real numbers on computer system. Fixed point places a radix point somewhere in the middle of the digits, and was equivalent to using integers that represent portions of some unit. For instance, a fixed-point number with 3 digits after the decimal point could be used to represent numbers such as: 1.005, 3.209, 28.000, etc. Another approach was to use rational, and represent every number as the ratio of two integers.

A number in scientific notation that has no leading 0s was called a normalized number, which was the usual way to write it. For example,  $1.0 \times 10^{-9}$  was in normalized scientific notation, but  $0.1_{\text{ten}} \times 10^{-8}$  was not (Patterson & Hennesy 2014).

Binary numbers in scientific notation:

$$1.0_{\text{two}} \times 2^{-1}$$

Computer arithmetic that supported such numbers was called floating point because it represents numbers in which the binary point was not fixed, as it was for integers.

Floating point solved a number of representation problems. Fixed point had a fixed window of representation, which limited it from representing very large or very small numbers. Also, fixed-point was prone to a loss of precision when two large numbers were divided. Floating point, on the other hand, employed a sort of "sliding window" of precision appropriate to the scale of the number. This allowed it to represent numbers from 1,000,000,000,000 to 0.0000000000000001 with ease.

A standard scientific notation for reals in normalized form offers three advantages. It not only simplifies exchange of data that includes floating-point numbers, it also simplified the floating-point arithmetic algorithms to know that numbers would always be in this form as well as increasing the accuracy of the numbers that could be stored in a word, since the unnecessary leading 0s were replaced by real digits to the right of the binary point (Patterson & Hennesy 2014).

#### 2-2-1 Single Precision Floating Point Number Representation

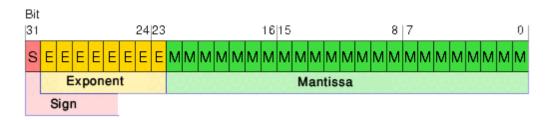

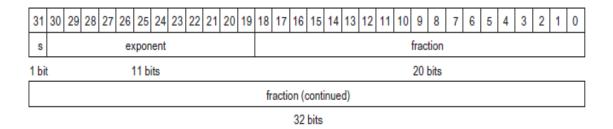

Figure 2-2-1-F1: Single precision floating point number representation.

S represents 1 sign bit.

E represents 8 exponent bits.

M represents 23 Mantissa or fraction (f) bits.

Floating point notation:

$$(-1)^s 2^e \times 1$$

.f (normalized)

$f = (b_{23}^{-1} + b_{22}^{-2} + b_i^n + ... + b_0^{-23})$  where  $b_i^n = 1$  or 0

$s = \text{sign } (0 \text{ was positive; } 1 \text{ was negative})$

$e = \text{unbiased exponent; } e = E - 127 \text{ (bias)}$

E<sub>max</sub>= 255, E<sub>min</sub>=0. E=255 and E=0 were used to represent special values.

#### 2-2-2 Double Precision Floating Point Number Representation

One way to reduce chances of underflow or overflow was to offer another format that had a larger exponent. In C, this number was called double and operations on doubles were called double precision floating-point arithmetic.

The double precision format was a method of storing approximations to real numbers in a binary format. The term double came from the full name, double precision floating-point numbers. Originally, a 4-byte floating-point number was used, (float), however, it was found that this was not precise enough for most scientific and engineering calculations, so it was decided to double the amount of memory allocated, hence the abbreviation double. The word 'double' here meant 64 bits.

The representation of a double precision floating-point number took two MIPS words, where *s* is still the sign of the number, exponent is the value of the 11-bit exponent field, and fraction is the 52-bit number in the fraction field.

Figure 2-2-2-F1: Double precision floating point number representation.

Although double precision did increase the exponent range, its primary advantage was its greater precision because of the much larger fraction. Since 0 had no leading 1, it was given the reserved exponent value 0 so that the hardware would not attach a leading 1 to it. The exponent was stored by adding a bias of 011111111112 to the actual exponent. Thus, this was all the information we need to interpret a double precision floating point number in binary form.

#### 2-3 Rounding

Although there were infinitely many integers, in most programs the result of integer computations could be stored in 32 bits. In contrast, given any fixed number of bits, most calculations with real numbers would produce quantities that could not be exactly represented using that many bits. Hence, the result of a floating-point calculation must often be rounded in order to fit back into its finite representation. The resulting rounding error is the characteristic feature of floating point computation (Goldberg 1991).

#### 2-4 Arithmetic on Floating Point Numbers

#### 2-4-1 Addition operation

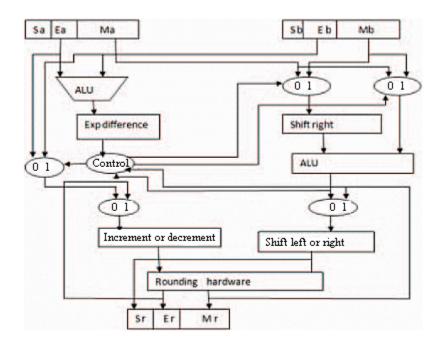

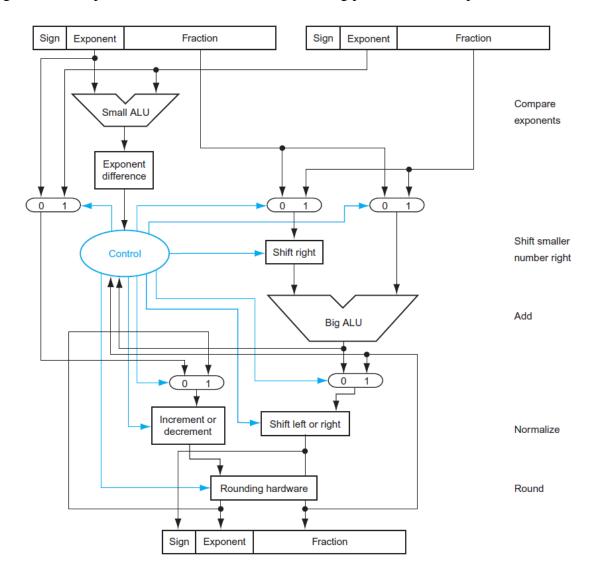

Based on the report from Singh and Bhole (2014), they had implemented arithmetic unit that are specially designed to carry out operations on floating point numbers. Floating point addition and subtraction algorithms consisted of five stages

- Firstly, difference between exponent was to be calculated, difference d = e1 e2. If e1 < e2 then d = e2 e1.

- In second stage pre-alignment of mantissas was achieved by shifting smaller mantissa right by d bits.

- In third stage addition of mantissa was done to get tentative result for mantissa.

- Then normalization is done. If there were leading-zeros in tentative result, result was shifted to left and exponent is decreased by number of leading zeros. If overflows, then result was shifted right and exponent increased by 1 bit.

- Last stage was rounding and produce final output.

Figure below explains the data flow on how the floating point arithmetic operation work.

Figure 2-4-1-F1: Algorithm of addition operation.

Since multiplication and division were far more complicated, so they would not be discussed here. In this project, only addition operation is being focused and the above algorithm is being implemented.

#### 2-5 Floating Point Pipeline

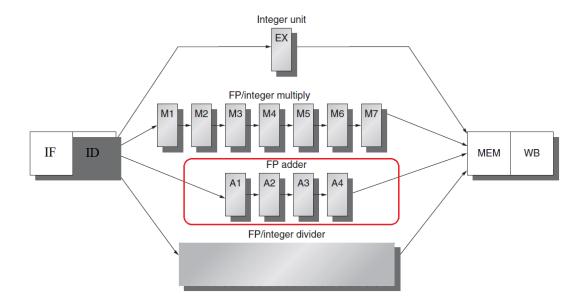

Due to FP operations required larger amount of logics to handle which arise some performance issue for the original 5-stage MIPS pipeline. This is because it is impractical to complete FP operations in 1 clock cycle as it will increase the latency for operations. The solution comes to extending the MIPS Pipeline for FP operations.

| Functional unit                     | Latency | Initiation interval |

|-------------------------------------|---------|---------------------|

| Integer ALU                         | 0       | 1                   |

| Data memory (integer and FP loads)  | 1       | 1                   |

| FP add                              | 3       | 1                   |

| FP multiply (also integer multiply) | 6       | 1                   |

| FP divide (also integer divide)     | 24      | 25                  |

Figure 2-5-F1: Latencies and initiation intervals for functional units

Pipeline latency is equal to 1 cycle less than the depth of the execution pipeline, which is the number of stages from the EX stage to the stage that produces the result. Therefore, based on the figure above, the number of stages in an FP add unit is four.

Figure 2-5-F1: Extended Pipeline for FP

In this project, only FP adder is being focused. Based on the figure above, the EX stage of the original pipeline is extended to 4 stages, A1 to A4 for FP adder. However, this only applies to floating point instruction such as add.s and add.d. The other instructions follow the original 5-stage pipeline for one complete execution.

#### **CHAPTER 3: PROPOSED METHOD AND APPROACH**

#### 3-1 Design Methodology

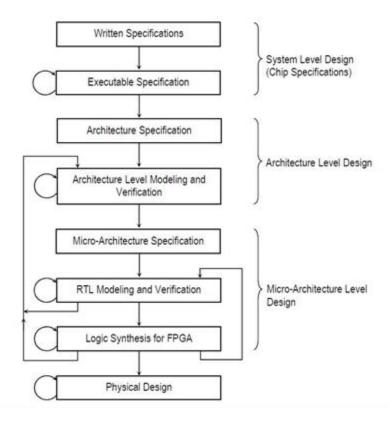

There were two types of design methodology were available, Top-down design methodology and Bottom-up design methodology. In top-down design methodology, the top level representation of a chip was first defined then partitioned into lower level representations. For bottom-up design methodology, the leaf nodes were first defined. The leaf nodes were then integrated to form a higher level model of the chip. This process was repeated until the top level of the chip was reached. Since digital system often uses the abstraction concepts to simplify the design process, thus top-down design methodology was used in this project.

Top-down design methodology process flow was shown in Figure 4.1. This methodology would keep on repeating until the system design met the requirement on functionality. If the design did not meet the requirement, the design flow had to be repeated. This project focused on microarchitecture level design.

Figure 3-1-F1: Top-down design methodology.

#### CHAPTER 3 PROPOSED METHOD AND APPROACH

#### 3-1-1 Micro-Architecture Specification

Micro-architecture specification described the internal design of a unit. The internal design was described with design-specific technical information for RTL coding to begin. For this project, the information included for each internal block of FPU were:

- FPU functionality description

- FPU operating procedures

- FPU interfaces and I/O pin description

- FPU internal operation

- FPU functional partitioning into blocks

- For each blocks,

- Block interfaces and I/O pin description

- Block functionality

- Block internal operation

- Finite-state machine (FSM)

- Block test plan

#### 3-1-2 RTL Modeling and Verification

With the micro-architecture specification developed, the RTL coding on FPU internal block could begin. The functional correctness of the model was verified at two levels:

- Micro-architecture level: Internal blocks of FPU were individually verified before they were integrated into the architecture level.

- Architecture level: The individual blocks of FPU were integrated into a unit. Verification was performed on the FPU.

### **3-2 Design Tools**

#### 3-2-1 ModelSim

Since this design would be using Verilog, it was crucial to discuss commonly used design software that could support Verilog. There would be 3 design software discussed here:

| Simulator        | VCS                            | ModelSim                  | Quartus II      |

|------------------|--------------------------------|---------------------------|-----------------|

| Company          | SYNOPSYS*  Predictable Success | <b>Mentor</b><br>Graphics |                 |

| Language         | VHDL-2002                      | VHDL-2002                 | VHDL            |

| Supported        | V2001                          | V2002                     | Verilog HDL     |

|                  | SV2005                         | SV2005                    |                 |

| Platform         | Linux                          | -Windows                  | -Windows XP/7/8 |

| Supported        |                                | XP/Vista/7/8              | -Linux          |

|                  |                                | -Linux                    |                 |

| Availability for | No                             | YES (SE Edition           | No              |

| free             |                                | only)                     |                 |

Table 3-2-1-T1: Comparison between simulation tools.

Since all of the design tools mentioned above were licensed product, ModelSim would be chose since free license was provided for student edition.

#### 3-2-2 PC Spim

PC Spim was a simulator that provides a MIPS environment to simulate MIPS assembly language. It would be used to develop test program to verify the functionality of the design.

#### 3-2-3 Xilinx Vivado

The Vivado development software was designed by Xilinx. This software was designed for synthesis and analysis of Verilog designs, enabling the developer to synthesize their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer.

#### 3-3 Grantt Chart

Figure 3-3-F1: Grantt Chart of Project.

## **CHAPTER 4 SYSTEM SPECIFICATION**

## **4-1 System Feature**

|                                    | RISC32 with FPU        |

|------------------------------------|------------------------|

| Dummy Instruction Cache (KB)       | 16                     |

| Dummy Data Cache (KB)              | 16                     |

| Data width (bits)                  | 32                     |

| Instruction width (bits)           | 32                     |

| General Purpose Register           | 32                     |

| Special Purpose Register           | HILO, PC               |

| Co-Processor Register              | 32                     |

| Floating Point Register            | 32                     |

| Pipelined Stage                    | 5                      |

| Data Hazard Handling               | Yes                    |

| Control Hazard Handling            | Yes                    |

| Interlock Handling                 | Yes                    |

| Exception Handling                 | Yes (4)                |

| Data Dependency Forwarding         | Yes                    |

| Branch Prediction                  | Dynamic – 2bits scheme |

| Multiplication (size of multiplier | yes – 32 bits          |

| and multiplicand)                  |                        |

| Branch Delay Slot                  | Not supported          |

| Instruction supported              | 44                     |

Table 4-1-F1 RISC32 Features

#### **CHAPTER 4 SYSTEM SPECIFICATION**

#### **4-1-1 System Functionality**

1. Divide execution of instruction into 5 stages:

-IF(Instruction Fetch) Instruction fetch and update PC

-ID(Instruction Decode) Decode instruction and fetch operand

-EX(Execute) Execute instruction

-MEM(Memory) Read/write data from/ memory

-WB(Write Back) Write back the result to the register file

2. Resolve data hazard by data forwarding.

3. Resolve load-use instructions problem using stalling.

4. Resolve structural hazards using separating data and instruction cache

5. Resolve control hazards by branch prediction.

6. Resolve exception interrupt with exception handler.

#### **4-2 Operating Procedure**

- 1. Start the system.

- 2. Porting sequence of instruction into instruction cache.

- 3. Reset the system for at least 2 clocks.

- 4. After the reset, the system will automatically fetch and run the program inside instruction cache.

- 5. Observe the waveform from development tools (Modelsim).

#### **4-3 Naming Convention**

Module - [lvl][mod. name]

Instantiation - [lvl][abbr. mod. name]

Pin - [lvl][type][abbr. mod. name]\_[pin name]

- [lvl][type][abbr. mod. name]\_[stage]\_[pin name]

- [lvl][type][abbr. mod. name]\_[pin name]

|                    | Description             | Case      | Available                                           | Remark                              |

|--------------------|-------------------------|-----------|-----------------------------------------------------|-------------------------------------|

| lvl                | Level                   | Lower     | c : Chip<br>u : Unit<br>b : Block<br>sb : sub-block |                                     |

| mod. name          | Module name             | Lower all | Any                                                 |                                     |

| abbr. mod.<br>name | Abbreviated module name | Lower all | Any                                                 | Maximum 3 characters                |

| type               | Pin type                | Lower     | o : output<br>i : input                             |                                     |

| stage              | Stage name              | Lower all | if, id ,ex, mem,<br>wb                              |                                     |

| pin name           | Pin name                | Lower all | Any                                                 | Several word<br>separated by<br>"_" |

Table 4-3-T1: Naming convention.

# **4-4 System Interface**

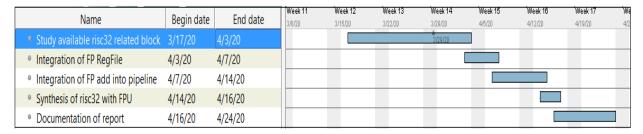

Figure 4-4-F1: Block diagram of RISC32 processor.

### **4-4-1 Input Pin Description**

| Pin Name:<br>uirisc_ua_rx_data,                                                                                     | Source -> Destination: DCE -> crisc | Active:<br>High |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|--|--|--|

| Receive data  Pin Function: Serial data to be received from DCE to DTE. When no data is transfer, this port is held |                                     |                 |  |  |  |

| at logic "1".  **DCE - Data Comr                                                                                    |                                     |                 |  |  |  |

| Pin Name:  uirisc_ua_cts, Clear-To-Send  Source -> Destination: DCE -> crisc  High                                  |                                     |                 |  |  |  |

| Pin Function: To inform DTE that it can start transmit at uorisc_ua_tx_data port.                                   |                                     |                 |  |  |  |

| Pin Name:                                                              | Source -> Destination: Active:                                 |      |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------|------|--|--|--|--|

| uirisc_clk,                                                            | External source -> crisc                                       | High |  |  |  |  |

| System Clock                                                           |                                                                |      |  |  |  |  |

| Pin Function:                                                          |                                                                |      |  |  |  |  |

| System clock for the                                                   | System clock for the integration of UART and RISC32 processor. |      |  |  |  |  |

| Pin Name:                                                              | Source -> Destination: Active:                                 |      |  |  |  |  |

| uirisc_rst,                                                            | External source -> crisc Hi                                    |      |  |  |  |  |

| Reset                                                                  |                                                                |      |  |  |  |  |

| Pin Function:                                                          |                                                                |      |  |  |  |  |

| System reset for the full chip. It is synchronous to the system clock. |                                                                |      |  |  |  |  |

Table 4-4-1-T1: Input pin description of RISC32 chip.

# **4-4-2 Output Pin Description**

| Pin Name:                                                                          | Source -> Destination:                                                           | Active:       |  |  |  |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|--|--|--|

| uorisc_ua_tx_data,                                                                 | crisc -> DCE                                                                     | High          |  |  |  |

| Transmit Data                                                                      |                                                                                  |               |  |  |  |

| Pin Function:                                                                      |                                                                                  |               |  |  |  |

| Serial data to be sent                                                             | from DTE to DCE. DTE shall hold this line at logi                                | c '1' when no |  |  |  |

| data is transfer.                                                                  |                                                                                  |               |  |  |  |

| Pin Name:                                                                          | Source -> Destination:                                                           | Active:       |  |  |  |

| uorisc_ua_rts,                                                                     | crisc -> DCE                                                                     | High          |  |  |  |

| Request-To-Send                                                                    |                                                                                  |               |  |  |  |

| Pin Function:                                                                      |                                                                                  |               |  |  |  |

| Transmission circuit                                                               | Transmission circuit will be enabled by this signal. Together with Clear-To-Send |               |  |  |  |

| signal, data transmission between DTE and DCE will be coordinated. Request-To-Send |                                                                                  |               |  |  |  |

| shall be asserted by UART when UART has data in transmission buffer. Can be de     |                                                                                  |               |  |  |  |

| asserted any time after                                                            | asserted any time after START bit is sent.                                       |               |  |  |  |

Table 4-4-2-T1: Output pin description of RISC32 chip.

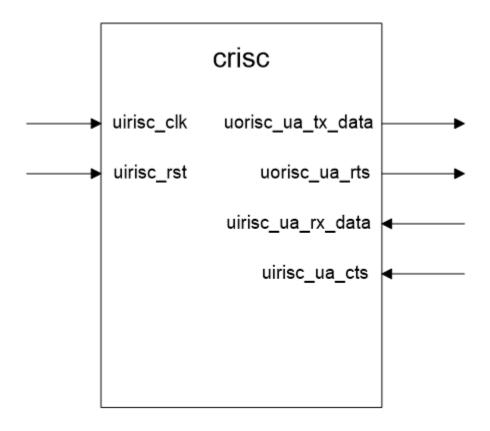

# 4-5 Memory Map

| Purpose                              | start address | Direction | Segment |

|--------------------------------------|---------------|-----------|---------|

| Kernel module                        | 0xC000 0000   | Up        | Kseg2   |

| Boot Rom                             |               | Up        | V1      |

| I/O register(if below 512MB)         | 0xA000 0000   | Up        | Kseg1   |

| Direct view of memory to 512MB linux |               | Lin       |         |

| kernel code and data                 |               | Up        | Kseg0   |

| Exception Entry point                | 0x8000 0180   | Up        |         |

| Stack                                | 0x7FFF FFFC   | Down      |         |

| Program heap                         | 0x1000 8000   | Up        |         |

| Dynamic library code and data        | 0x1000 0000   | Up        | Kuseg   |

| Main program                         | 0x0040 0000   | Up        |         |

| Reserved                             | 0x0000 0000   | Up        |         |

Table 4-5-T1: Memory Map

Figure 4-5-F1: Memory Map

However, due to the limitation of modelsim student edition version which only support up to 8k memory, the cache size will set text segment from 32'h0040\_0000 to 32'h0040\_1FFC, data segment from 32'h1000\_0000 to 32'h1000\_1FFC, stack segment from 32'h7fff\_e000 to 32'h7fff\_fffc, kernel text segment from 32'h8000\_0000 to 32'h8000\_1FFC and kernel data segment from 32'h9000\_0000 to 32'h9000\_0FFC.

# **4-5-1 Memory Map Description**

| Purpose                              | Description                                       |  |  |

|--------------------------------------|---------------------------------------------------|--|--|

| Kernel Module                        | Accessible by kernel*                             |  |  |

| Boot Rom                             | Start-up ROM which keep the system configuration* |  |  |

| I/O registers(if below(512MB)        | External IO device registers*                     |  |  |

| Direct view of memory to 512MB linux | Memory Allocation to view linux kernel            |  |  |

| kernel code and data                 | code and data*                                    |  |  |

| Exception Entry point                | Software exception handling*                      |  |  |

| Stack                                | Use for argument passing                          |  |  |

| Program heap                         | Dynamic memory allocation such as                 |  |  |

|                                      | malloc()                                          |  |  |

| Dynamic library code and data        | Data segment which is access by variable          |  |  |

| Main program                         | Text segment which contain the main               |  |  |

|                                      | program                                           |  |  |

Table 4-5.1-T1: Memory Map Description

Note \*: required CP0

### 4-6 System Register

### 4-6-1 General Purpose Register

Width: 32-bits Size: 32 units

Retrieving method : 5-bits address as index

| Name        | Address | Use                                                     | Preserved Across A Call? |

|-------------|---------|---------------------------------------------------------|--------------------------|

| \$zero      | 0       | Constant Value 0 (hardwired)                            | N.A.                     |

| \$at        | 1       | Assembler Temporary                                     | No                       |

| \$v0 - \$v1 | 2 - 3   | Value for Function Results and<br>Expression Evaluation | No                       |

| \$a0 - \$a3 | 4 - 7   | Arguments                                               | No                       |

| \$t0 - \$t7 | 8 – 15  | Temporaries                                             | No                       |

| \$s0 - \$s7 | 16 - 23 | Saved temporaries                                       | Yes                      |

| \$t8 - \$t9 | 24 – 25 | Temporaries                                             | No                       |

| \$k0 - \$k1 | 26 -27  | Reserved for OS kernel                                  | No                       |

| \$gp        | 28      | Global Pointer                                          | Yes                      |

| \$sp        | 29      | Stack Pointer                                           | Yes                      |

| \$fp        | 30      | Frame Pointer                                           | Yes                      |

| \$ra        | 31      | Return Address                                          | Yes                      |

Table 4-6-1-T1: General Purpose Registers

### 4-6-2 Special Purpose Register

Width : 32-bits Size : 2 units

Retrieving method: Via instructions: MFHI, MTHI, MFLO, MTLO, MULT or MULTU

| Name | definition             | location in double [64:0] |

|------|------------------------|---------------------------|

| HI   | Most Significant Word  | Double [63:32]            |

| LO   | Least Significant Word | Double [31:0]             |

Table 4-6-2-T1: Special Purpose Register

#### **CHAPTER 4 SYSTEM SPECIFICATION**

### 4-6-3 Program Counter Register

Width : 32-bits Size : 1 unit

Retrieving method: Control by instruction address generator control.

#### 4-6-4 CP0 Register

| Name         | Address | Use                                                            |  |  |

|--------------|---------|----------------------------------------------------------------|--|--|

| \$bcp0_stat  | 12      | Interrupt mask, enable bits and status when exception occurred |  |  |

| \$bcp0_cause | 13      | Exception type and pending interrupt                           |  |  |

| \$bcp0_epc   | 14      | Address of instruction that caused exception                   |  |  |

Table 4-6-4-T1: CP0 Register

### 4-6-5 FP Register

Width : 32 bits

Size : 32 units

Retrieving method: 5-bits address as index

| Name          | Usage                                                            |  |  |  |

|---------------|------------------------------------------------------------------|--|--|--|

| \$f0 - \$f3   | Floating point return values                                     |  |  |  |

| \$f4 - \$f10  | Temporary registers. Not preserved across procedure calls        |  |  |  |

| \$f12 - \$f14 | First two arguments to subprograms, not preserved by subprograms |  |  |  |

| \$f16 - \$f18 | More temporary registers, not preserved by subprograms           |  |  |  |

| \$f20 - \$f31 | Saved registers, preserved by subprograms                        |  |  |  |

Table 4-6-5-T1: FP Register

# **4-7 Instruction Formats and Addressing Modes**

#### **4-7-1 Basic Instruction Formats**

|   | 6 bits | 5 bits                | 5 bits | 5 bits                | 5 bits | 6 bits   |                                       |

|---|--------|-----------------------|--------|-----------------------|--------|----------|---------------------------------------|

|   | ор     | rs                    | rt     | rd                    | shamt  | funct    | R-format                              |

| [ | ор     | rs                    | rt     | immediate (16-bit)    |        | -bit)    | I-format (Immediate Instructions)     |

| [ | op     | rs                    | rt     | data address offset   |        | ffset    | I-format (Data Transfer Instructions) |

| [ | op     | rs                    | rt     | branch address offset |        | offset   | I-format (Branch Instructions)        |

| [ | op     | jump address (26-bit) |        |                       |        | J-format |                                       |

Figure 4-7-1-F1: Instruction Format

| Abbreviation          | Definitiion           | Width |

|-----------------------|-----------------------|-------|

| op                    | Operation code        | 6     |

| rs                    | Source register       | 5     |

| rt                    | Target register       | 5     |

| rd                    | Destination register  | 5     |

| shamt                 | Shift amount          | 5     |

| funct                 | Function field        | 6     |

| immediate             | Immediate             | 16    |

| data address offset   | Data address offset   | 16    |

| branch address offset | Branch address offset | 16    |

| jump address          | Jump address          | 26    |

Table 4-7-1-T1: Instruction Format Definition

#### **4-7-2 FP Instruction Formats**

| _ | 6 bits | 5 bits | 5 bits | 5 bits | 5 bits     | 6 bits |           |

|---|--------|--------|--------|--------|------------|--------|-----------|

|   | op     | fmt    | ft     | fs     | fd         | funct  | FR-format |

|   | op     | fmt    | ft     | imm    | ediate (10 | 5-bit) | FI-format |

Figure 4-7-2-F1: FP Instruction Format

#### 4-7-3 Addressing Modes

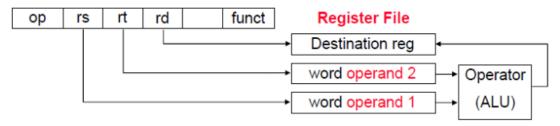

#### a) R-format

Register addressing: Perform operation on source and target register and store the result into destination register

Figure 4-7-3-F1: R-format Addressing

#### b) I-format

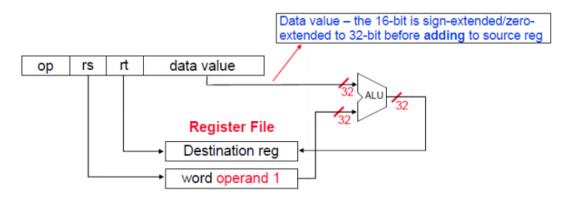

i. Immediate addressing: Perform operation on source register and immediate and store the result into target register

Figure 4-7-3-F2: Immediate Addressing

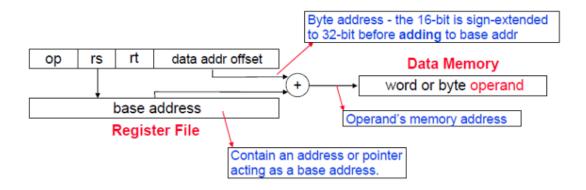

ii. Based displacement addressing: Perform operation on source register and immediate, the result is then uses as address to access the data memory to load/store data to/from target register

Figure 4-7-3-F3: Based Displacement Addressing

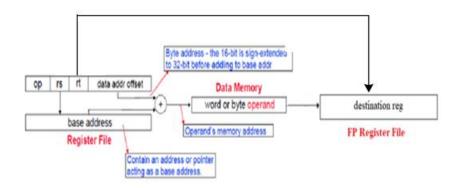

Figure 4-7-3-F4: Based Displacement Addressing with FP Register File (Used by lwc1, swc1)

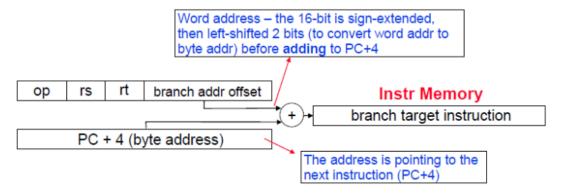

iii. PC-relative addressing: Perform operation on source and target register to determine next PC condition, the immediate is uses as address offset for next PC

Figure 4-7-3-F5: PC-Relative Addressing

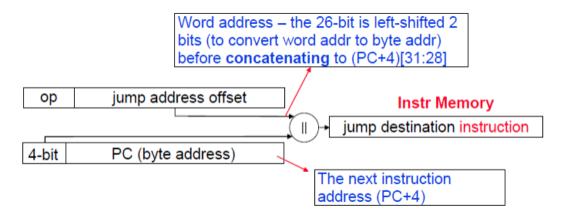

#### c) J-format

Pseudo-direct addressing: Perform operation by concatenating the upper bits of PC with the jump address

Figure 4-7-3-F6: Pseudo-Direct Addressing

#### **CHAPTER 4 SYSTEM SPECIFICATION**

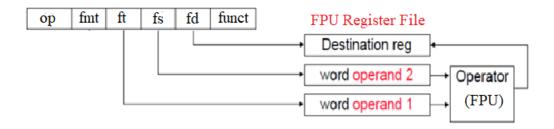

#### d) FR-format

Register addressing: Perform operation on source and target register and store the result into destination register

Figure 4-7-3-F7: Register Addressing for FR format (Used by add.s, add.d)

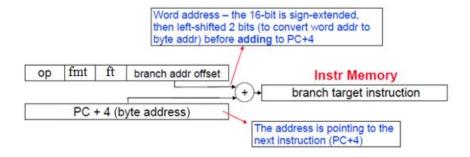

#### e) FI-format

PC-relative addressing: Perform operation on source and target register to determine next PC condition, the immediate is uses as address offset for next PC

Figure 4-7-3-F8: Register Addressing for FR format (Used by FP branching instructions)

# **4-8 Supported Instructions Set**

| Instructio | Format | Addr. Mode        | Machi      | ne Lang | guage  |       |           |          | Register Transfer Notation                | Assembly Format       | Over |

|------------|--------|-------------------|------------|---------|--------|-------|-----------|----------|-------------------------------------------|-----------------------|------|

| n          |        |                   | OpC<br>ode | Rs      | Rt     | Rd    | Sham<br>t | Func     |                                           |                       | flow |

| sll        | R      | Register          | 0x00       | 0       | \$rt   | \$rd  | n         | 0x01     | R[rd] =R[rs] << n                         | sll \$rd, \$rt, n     | no   |

| srl        | R      | Register          | 0x00       | 0       | \$rt   | \$rd  | n         | 0x03     | R[rd] = R[rs] >> n                        | srl \$rd, \$rt, n     | no   |

| sra        | R      | Register          | 0x00       | 0       | \$rt   | \$rd  | n         | 0x04     | R[rd] = R[rs] >>> n                       | sra \$rd, \$rt, n     | no   |

| jr         | R      | Register          | 0x00       | \$rs    | 0      | 0     | 0         | 0x0<br>A | PC = R[rs]                                | jr \$rs               | no   |

| jalr       | R      | Register          | 0x00       | \$rs    | 0      | 0     | 0         | 0x0<br>B | PC = R[rs], R[31] = PC + 4                | jalr \$rs             | no   |

| mfhi       | R      | Register          | 0x00       | 0       | 0      | \$rd  | 0         | 0x10     | R[rd] = HI                                | mfhi \$rd             | no   |

| mthi       | R      | Register          | 0x00       | \$rs    | 0      | 0     | 0         | 0x11     | HI = R[rs]                                | mthi \$rs             | no   |

| mflo       | R      | Register          | 0x00       | 0       | 0      | \$rd  | 0         | 0x12     | R[rd] = LO                                | mflo \$rd             | no   |

| mtlo       | R      | Register          | 0x00       | \$rs    | 0      | 0     | 0         | 0x13     | LO = R[rs]                                | mtlo \$rs             | no   |

| mult       | R      | Register          | 0x00       | \$rs    | \$rt   | 0     | 0         | 0x24     | HILO = R[rs] * R[rt]                      | mult \$rs, \$rt       | no   |

| multu      | R      | Register          | 0x00       | \$rs    | \$rt   | 0     | 0         | 0x24     | HILO = U(R[rs]) * U(R[rt])                | multu \$rs, \$rt      | no   |

| add        | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x20     | R[rd] = R[rs] + R[rt]                     | add \$rd, \$rs, \$rt  | yes  |

| addu       | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x21     | R[rd] = U(R[rs]) + U(R[rt])               | addu \$rd, \$rs, \$rt | no   |

| sub        | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x22     | R[rd] = R[rs] - R[rt]                     | sub \$rd, \$rs, \$rt  | yes  |

| subu       | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x23     | R[rd] = U(R[rs]) - U(R[rt])               | subu \$rd, \$rs, \$rt | no   |

| and        | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x24     | R[rd] = R[rs] & R[rt]                     | and \$rd, \$rs, \$rt  | no   |

| or         | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x25     | $R[rd] = R[rs] \mid R[rt]$                | or \$rd, \$rs, \$rt   | no   |

| xor        | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x26     | $R[rd] = R[rs] \wedge R[rt]$              | xor \$rd, \$rs, \$rt  | no   |

| nor        | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x27     | $R[rd] = \sim (R[rs]   R[rt])$            | nor \$rd, \$rs, \$rt  | no   |

| slt        | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x2<br>A | R[rd] = (R[rs] < R[rt]) ? 1 : 0           | slt \$rd, \$rs, \$rt  | no   |

| sltu       | R      | Register          | 0x00       | \$rs    | \$rt   | \$rd  | 0         | 0x2<br>B | R[rd] = (U(R[rs]) < U(R[rt]))?<br>1:0     | sltu \$rd, \$rs, \$rt | no   |

| j          | J      | Pseudo-<br>Direct | 0x02       | Jump    | Addr ( | Label | )         |          | PC = {(PC+4) [31:28],<br>JumpAddr, 2'b00} | j label               | no   |

### **CHAPTER 4 SYSTEM SPECIFICATION**

| beq   | I | PC-Relative                | 0x04 | \$rs | \$rt | BranchAddr<br>(Label) | PC = (R[rs] == R[rt]) ?<br>(PC + 4 + (SE(BranchAddr) << 2)) :<br>(PC + 4)        | beq \$rs, \$rt, label  | no  |

|-------|---|----------------------------|------|------|------|-----------------------|----------------------------------------------------------------------------------|------------------------|-----|

| bne   | I | PC-Relative                | 0x05 | \$rs | \$rt | BranchAddr<br>(Label) | PC = (R[rs] != R[rt]) ?<br>(PC + 4 + (SE(BranchAddr) << 2)) :<br>(PC + 4)        | bne \$rs, \$rt, label  | no  |

| blez  | I | PC-Relative                | 0x06 | \$rs | 0    | BranchAddr<br>(Label) | PC = (R[rs] <=0) ?<br>(PC + 4 +<br>(SE(BranchAddr)<<2)) :<br>(PC + 4)            | blez \$rs, \$rt, label | no  |

| bgtz  | I | PC-Relative                | 0x07 | \$rs | 0    | BranchAddr<br>(Label) | PC = (R[rs] > 0 ) ?<br>(PC + 4 +<br>(SE(BranchAddr)<<2)) :<br>(PC + 4)           | bgtz \$rs, \$rt, label | no  |

| addi  | I | Immediate                  | 0x08 | \$rs | \$rt | Imm                   | R[rt] = R[rs] + SE(Imm)                                                          | addi \$rt, \$rs, imm   | yes |

| addiu | I | Immediate                  | 0x09 | \$rs | \$rt | Imm                   | R[rt] = U(R[rs]) + U(ZE(Imm))                                                    | addiu \$rt, \$rs, imm  | no  |

| slti  | I | Immediate                  | 0x0A | \$rs | \$rt | Imm                   | R[rt] = (R[rs] < SE(Imm)) ? 1 : 0                                                | slti \$rt, \$rs, imm   | no  |

| sltiu | I | Immediate                  | 0x0B | \$rs | \$rt | Imm                   | $ \begin{array}{ll} R[rt] &=& (U(R[rs]) &<\\ U(SE(Imm))) ? 1 : 0 & \end{array} $ | sltiu \$rt, \$rs, imm  | no  |

| andi  | I | Immediate                  | 0x0C | \$rs | \$rt | Imm                   | R[rt] = R[rs] & ZE(Imm)                                                          | andi \$rt, \$rs, imm   | no  |

| ori   | I | Immediate                  | 0x0D | \$rs | \$rt | Imm                   | $R[rt] = R[rs] \mid ZE(Imm)$                                                     | ori \$rt, \$rs, imm    | no  |

| xori  | I | Immediate                  | 0x0E | \$rs | \$rt | Imm                   | $R[rt] = R[rs] ^ ZE(Imm)$                                                        | xori \$rt, \$rs, imm   | no  |

| lui   | I | Immediate                  | 0x0F | \$rs | \$rt | Imm                   | R[rt] = Imm << 16                                                                | lui \$rt, imm          | no  |