# The Design of An Asynchronous RISC Processor BY PEE YAO HONG

# A REPORT SUBMITTED TO Universiti Tunku Abdul Rahman in partial fulfillment of the requirements for the degree of BACHELOR OF INFORMATION TECHNOLOGY (HONOURS) COMPUTER ENGINEERING Faculty of Information and Communication Technology (Kampar Campus) JAN 2021

### UNIVERSITI TUNKU ABDUL RAHMAN

| The Design of An Asynchronous RISC Processor      |                                                                                    |                                                                                    |  |

|---------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

|                                                   | Academic Session                                                                   | n: <u>2021/01</u>                                                                  |  |

| I                                                 | PEE YAO HONG                                                                       |                                                                                    |  |

| -                                                 | (CAPITAL                                                                           | LETTER)                                                                            |  |

| 1. The                                            | dissertation is a property of the Librar                                           | ct to the regulations as follows:<br>y.<br>his dissertation for academic purposes. |  |

| 1. The                                            | dissertation is a property of the Librar                                           | у.                                                                                 |  |

| 1. The                                            | dissertation is a property of the Librar                                           | у.                                                                                 |  |

| 1. The                                            | dissertation is a property of the Librar                                           | y.<br>his dissertation for academic purposes.                                      |  |

| 1. The<br>2. The                                  | dissertation is a property of the Librar                                           | y.<br>his dissertation for academic purposes.                                      |  |

| 1. The<br>2. The<br>(Author'<br>Address           | dissertation is a property of the Librar<br>Library is allowed to make copies of t | y.<br>his dissertation for academic purposes.<br>Verified by,                      |  |

| 1. The<br>2. The<br>(Author'<br>Address<br>K-90L, | dissertation is a property of the Librar<br>Library is allowed to make copies of t | y.<br>his dissertation for academic purposes.<br>Verified by,                      |  |

# The Design of An Asynchronous RISC Processor BY PEE YAO HONG

A REPORT SUBMITTED TO Universiti Tunku Abdul Rahman in partial fulfillment of the requirements for the degree of BACHELOR OF INFORMATION TECHNOLOGY (HONOURS) COMPUTER ENGINEERING Faculty of Information and Communication Technology (Kampar Campus) JAN 2021

### **DECLARATION OF ORIGINALITY**

I declare that this report entitled "**The Design of An Asynchronous RISC Processor**" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other award.

lee

Signature

:

| Name | : | PEE YAO HONG |

|------|---|--------------|

| Date | : | 16/04/2021   |

## ACKNOWLEDGEMENTS

I would like to express my sincere thanks and appreciation to my supervisors, Mr Mok Kai Ming who has given me this bright opportunity to engage in a digital system design project. It is my first step to establish a career in digital system design field. A million thanks to you.

A million thanks to my family, especially my parents, for their patience, unconditional support and love, and for always backing me up throughout the course. They have always been there to provide me with financial support.

To my course mates of CT course, I would like to txtend my gratitude for their friendship, company and encouragement during the course of my bachelor degree. We had been putting in a lot of hard work together as a team for the past 3 years.

Finally, I would like to extend my sincere thanks to my seniors who have willingly helped me out with their abilities, providing necessary and useful information about the project. All the advises and suggestions had contributed to the completion of this project.

#### Abstract

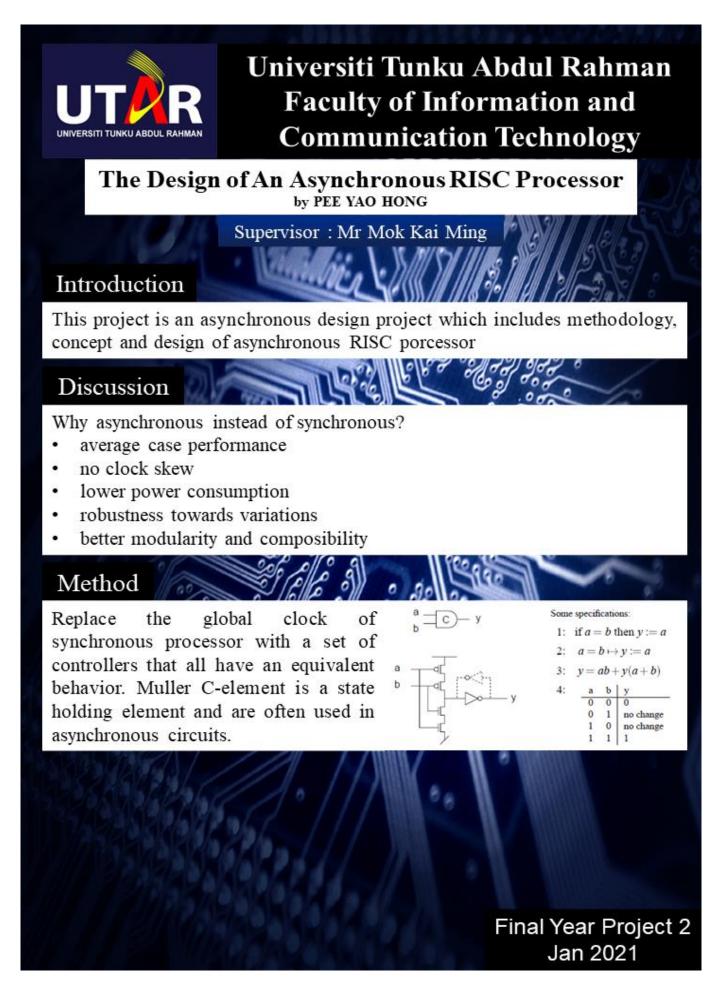

This project is an asynchronous processor design project for academic purpose. It will provide students with the methodology, concept and design of asynchronous RISC processor. This will be illustrated by converting a synchronous processor to an asynchronous processor. This can be done by substituting the global clock for a synchronous processor with a set of controllers that all have an equivalent behavior. Since asynchronous processor is better than synchronous processor in aspects of no clock skew, lower power dissipation and etc, it is well suited for digital circuits and therefore implemented in this project. The tools used in this project are Verilog hardware description language in combination with ModelSim synthesis tools and PCSpim. Moreover, there is several types of asynchronous implementation style and the one used here is the 4-phase single-rail pipeline. The verification plan of the project is a testbench with numbers of instruction to make sure the processor is workable. Lastly, the output of the project would be the synthesized hardware of asynchronous RISC processor with shortest delay for every single instruction in order to implement that asynchronous processor is better than synchronous processor.

| TITLE PAGE                                                               | i       |

|--------------------------------------------------------------------------|---------|

| DECLARATION OF ORIGINALITY                                               |         |

| ACKNOWLEDGEMENTS                                                         |         |

|                                                                          |         |

| ABSTRACT                                                                 | iv      |

| TABLE OF CONTENTS                                                        | v - vii |

| LIST OF TABLES                                                           | viii    |

| LIST OF FIGURES                                                          | ix - x  |

| LIST OF ABBREVIATIONS                                                    | xi      |

|                                                                          |         |

| CHAPTER 1 : INTRODUCTION                                                 |         |

| 1.1 Problem Statement and Motivation                                     | 1 - 4   |

| 1.2 Project Scope                                                        | 5       |

| 1.3 Problem Objectives                                                   | 5       |

| 1.4 Impact, Significance and Contribution                                | 6       |

| 1.5 Background Information                                               | 7       |

|                                                                          |         |

| <b>CHAPTER 2 : LITERATURE REVIEW</b>                                     |         |

| 2.1 Literature Review                                                    | 8 - 15  |

| 2.2 Data Collection                                                      | 16      |

| 2.3 Critical Remark of Previous Works                                    | 17      |

| CHAPTER 3 : HARDWARE DEVELOPMENT                                         |         |

| 3.1 System Overview                                                      | 18      |

| 3.1.1 Design Hierarchy                                                   | 18 - 19 |

| 3.1.2 Internal Operation                                                 | 20      |

|                                                                          | 20      |

| 3.1.3 Memory Map                                                         |         |

| 3.2 CPU                                                                  | 22      |

| 3.2.1 Pipeline Micro-architecture         3.3 Design Block Specification | 22 - 23 |

| 3.3.1 Main Control Block                                                 | 24      |

| 5.5.1 Main Control Block                                                 | 24 - 28 |

# **Table of Contents**

| 3.3.2 Arithmetic Logic Control Block             | 28      |

|--------------------------------------------------|---------|

| 3.3.3 Register File Block                        | 29 - 31 |

| 3.3.4 Forwarding Block                           | 32 - 37 |

| 3.3.5 Interlock Block                            | 38 - 39 |

| 3.3.6 ALU Block                                  | 40 - 41 |

| 3.3.7 Multiplier Block                           | 42 - 43 |

| 3.3.8 Boot ROM Unit                              | 43      |

| 3.3.9 Data and Stack RAM Unit                    | 44 - 45 |

|                                                  |         |

| CHAPTER 4 : METHODLOGY AND TOOLS                 |         |

| 4.1 Design Specifications                        | 46      |

| 4.1.1 Methodologies and General Work Procedures  | 46 - 47 |

| 4.1.2 Development Tools                          | 47 - 48 |

| 4.1.3 Verification Plan                          | 48      |

| 4.2 Timeline                                     | 49      |

|                                                  |         |

| <b>CHAPTER 5 : MULLER C-ELEMENT</b>              |         |

| 5.1 Muller Pipeline                              | 50      |

| 5.2 Circuit Implementation Style                 | 52 - 55 |

| 5.3 Implementation of Pipeline                   | 56      |

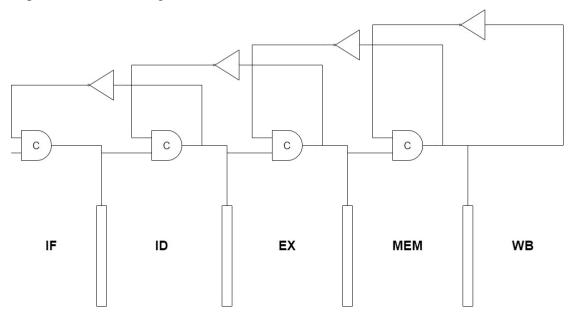

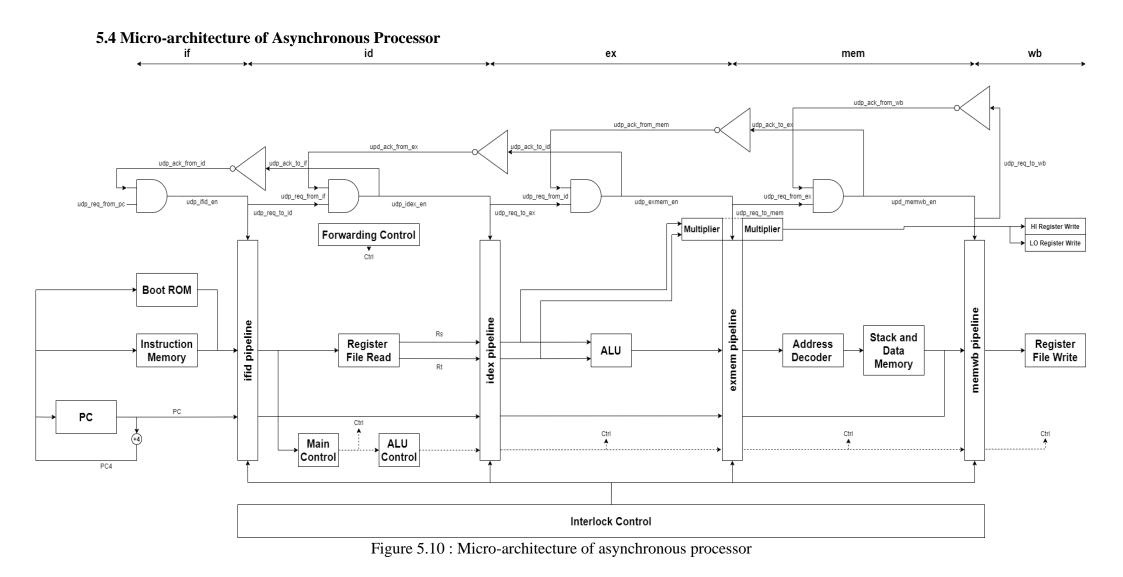

| 5.4 Micro-architecture of Asynchronous Processor | 57      |

|                                                  |         |

| CHAPTER 6 : VERIFICATION                         |         |

| 6.1 Simulation Result                            | 58 - 60 |

| CHAPTER 7 : SYNTHESIS                            | 61      |

| 7.1 Utilization Report                           |         |

|                                                  |         |

| <b>CHAPTER 8 : CONCLUSION AND FUTURE WORK</b>    |         |

| 8.1 Conclusion                                   | 62      |

| 8.2 Future Work                                  | 62      |

| BIBLIOGRAPHY            | 63      |

|-------------------------|---------|

| POSTER                  | 64 - 65 |

| PLAGIARISM CHECK RESULT | 66 - 67 |

| FYP2 CHECKLIST          | 68      |

| Table Number | Title                                                          | Page    |

|--------------|----------------------------------------------------------------|---------|

| Table 2.1    | Comparison between different type of asynchronous processor    | 16      |

| Table 3.1    | Design hierarchy of the processor                              | 19      |

| Table 3.2    | Main Control Block I/O description                             | 24 - 28 |

| Table 3.3    | Arithmetic Logic Control Block I/O<br>description              | 28      |

| Table 3.4    | Conventional usange of the registers in<br>Register File Block | 29      |

| Table 3.5    | Register File Block I/O description                            | 30      |

| Table 3.6    | General condition of Register File related<br>data hazards     | 33      |

| Table 3.7    | \$ra register relater data hazards                             | 34      |

| Table 3.8    | HILO register related data hazards                             | 35      |

| Table 3.9    | Forwarding Block I/O description                               | 35 - 37 |

| Table 3.10   | Interlock Block I/O description                                | 38 - 39 |

| Table 3.11   | ALU Block I/O description                                      | 40      |

| Table 3.12   | ALU Block operation                                            | 41      |

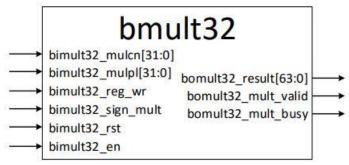

| Table 3.13   | Multiplier Block I/O description                               | 42 - 43 |

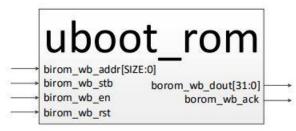

| Table 3.14   | Boot ROM Unit I/O description                                  | 43      |

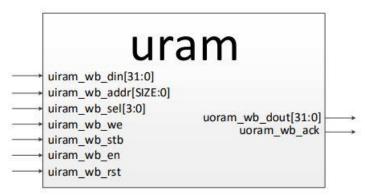

| Table 3.15   | Data and Stack RAM Unit I/O description                        | 44 - 45 |

| Table 4.1    | Gantt chart for Project I                                      | 49      |

| Table 4.2    | Gantt chart for Project II                                     | 49      |

| Table 7.1    | The utilization report                                         | 61      |

# List of Tables

| Figure Number | Title                                            | Page |

|---------------|--------------------------------------------------|------|

| Figure 2.1    | The Caltech Asynchronous Processor               | 8    |

| Figure 2.2    | The Fully Asynchronous Processor                 | 9    |

| Figure 2.3    | The Non synchronous RISC                         | 10   |

| Figure 2.4    | The Counter Flow Pipeline Processor              | 12   |

| Figure 2.5    | The structure of the STRIP processor             | 13   |

| Figure 2.6    | Amulet1 processor organization                   | 14   |

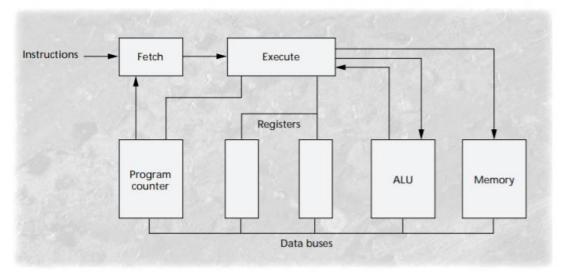

| Figure 3.1    | The overview of the processor                    | 18   |

| Figure 3.2    | Micro-architecture of the processor              | 18   |

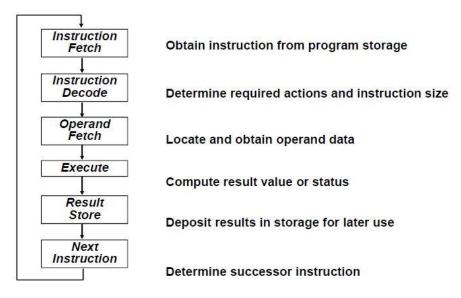

| Figure 3.3    | Instruction execution cycle                      | 20   |

| Figure 3.4    | Memory map                                       | 21   |

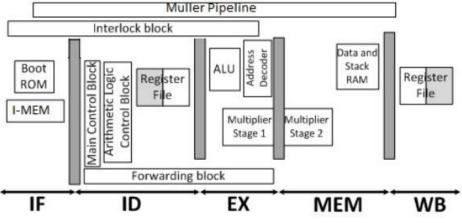

| Figure 3.5    | Abstract view of 5-stage asynchronous processor  | 22   |

| Figure 3.6    | Micro-architecture of datapath with memory unit  | 23   |

| Figure 3.7    | Main Control Block chip interface                | 24   |

| Figure 3.8    | Arithmetic Logic Control Block chip<br>interface | 28   |

| Figure 3.9    | Register File Block chip interface               | 30   |

| Figure 3.10   | Internal operation of Register File Block        | 31   |

| Figure 3.11   | Forwarding Block chip interface                  | 35   |

| Figure 3.12   | Interlock Block chip interface                   | 38   |

| Figure 3.13   | ALU Block chip interface                         | 40   |

| Figure 3.14   | Multiplier Block chip interface                  | 42   |

| Figure 3.15   | Boot ROM Unit chip interface                     | 43   |

| Figure 3.16   | Data and Stack RAM Unit chip interface           | 44   |

# **List of Figures**

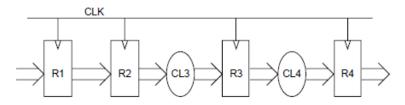

| Figure 4.1  | Synchronous circuit                                                   | 46 |

|-------------|-----------------------------------------------------------------------|----|

| Figure 4.2  | Asynchronous circuit                                                  | 46 |

| Figure 4.3  | An asynchronous control circuit                                       | 47 |

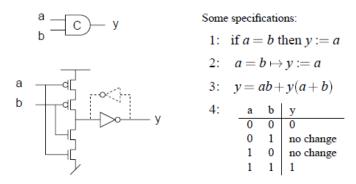

| Figure 5.1  | The Muller C-element                                                  | 50 |

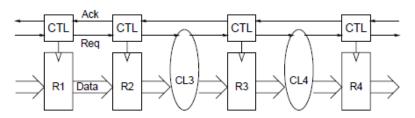

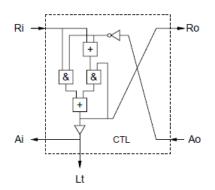

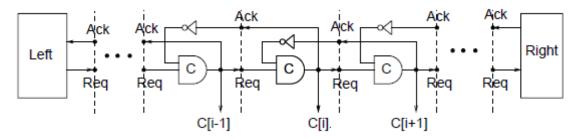

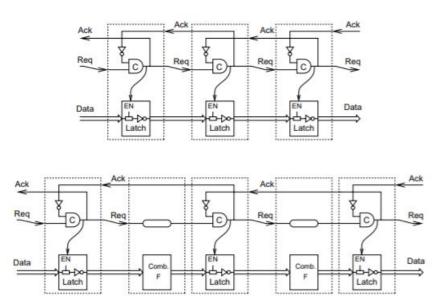

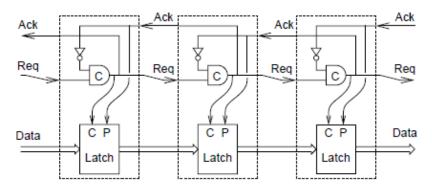

| Figure 5.2  | Muller pipeline                                                       | 51 |

| Figure 5.3  | The 4 phases single-rail pipeline                                     | 52 |

| Figure 5.4  | The 2 phases single-rail pipeline                                     | 53 |

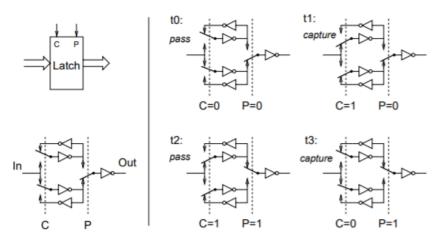

| Figure 5.5  | Operation and Implementation of a capture-pass event controlled latch | 53 |

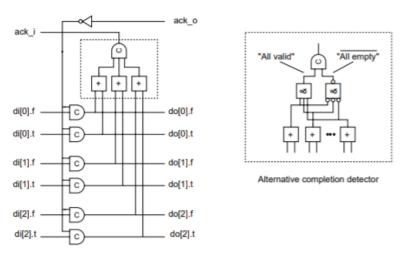

| Figure 5.6  | A simple 3-stage 1-bit wide 4-phase<br>dual-rail pipeline             | 54 |

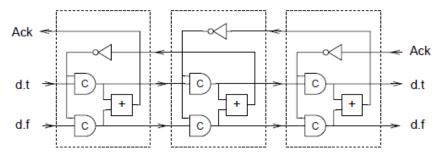

| Figure 5.7  | An N-bit latch with completion detection                              | 54 |

| Figure 5.8  | Illustration of handshaking on a 2-phase<br>dual-rail channel         | 55 |

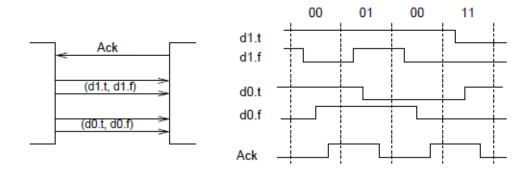

| Figure 5.9  | Pipeline with Muller C-element                                        | 56 |

| Figure 5.10 | Micro-architecture of asynchronous processor                          | 57 |

| Figure 6.1  | The waveform of muller pipeline                                       | 58 |

| Figure 6.2  | The results of arithmetic instruction                                 | 58 |

| Figure 6.3  | The results of logical instruction                                    | 58 |

| Figure 6.4  | The results of STORE, SET_BR and LWSW                                 | 59 |

| Figure 6.5  | The results of t_sb, t_lb and t_lbu                                   | 59 |

| Figure 6.6  | The results of t_sh, t_lh and t_lhu                                   | 59 |

| Figure 6.7  | The results of swl, swr, lwl and lwr                                  | 59 |

| Figure 6.8  | The results of multiplication and loop                                | 60 |

| RISC | Reduced Instruction Set Computing                     |  |

|------|-------------------------------------------------------|--|

| FPGA | Field Programmable Gate Array                         |  |

| MIPS | Microprocessor without Interlocked Pipeline<br>Stages |  |

| ALU  | Arithmetic Logic Unit                                 |  |

| FIFO | First-In First-Out                                    |  |

| CMOS | Complementary Metal Oxide Semiconductor               |  |

| RTL  | Register-Transfer Level                               |  |

| HDL  | Hardware Description Language                         |  |

# List of Abbreviations

#### **Chapter 1 : Introduction**

#### **1.1 Problem statement and Motivation**

A 32-bit five stage pipeline asynchronous RISC soft-core can be beneficial in creating a core-based environment to support research and development work in the area of developing IP cores. On the other hand, there are restrictions in obtaining such workable core-based design environment as microprocessors are developed by microchip design companies as IP for commercial purpose and most of these IP are trade secret of those companies.

There are some asynchronous processor cores projects available freely online such as www.opencore.org, www.ics.forth.gr/carv/aspida/ and etc. However, the asynchronous processor's micro-architecture included in these projects is not well presented. Other than that, the Verilog codes wrote in these projects are also hard to understand because of the confused naming convention used.

Furthermore, the verification plans for the asynchronous processor which available on the open source are not completed. The lack of complete verification for the processor will affect the process of design. Therefore, there is a necessary to develop a verification plan to verify the functionality of the asynchronous processor.

Last but not least, the senior who took this FYP title previously was not able to finish her work. The outputs of the supported insturctions are incorrect and the synthesis of the asynchronous processor on FPGA has not been done yet. Nowadays, there are a lot of digital system designed as synchronous. In synchronous circuits, the data stored in memory devices named flip-flops. The flip-flop output the data at discrete instants of time which specified by a clock signal connected to it. This synchronous circuits built based on two assumptions which are the signals are in binary and every parts share a same clock signal. (Jens Sparsø & Steve 2001, p3)

By assuming all signals are in binary, the logic inside the circuit can be illustrated by simple Boolean logic. Moreover, by assuming every parts share a same clock signal, something happen inside the circuit can be ignored such as hazards and feedback. However, when the complexity of system and speed of clock increase, synchronous design has a lot of problems because of its way of keeping operations in lock-step execution. The problems are stated below (Hans Jacobson 1996, p13-14):

### • Worst Case Performance

The clock frequency determines the speed of asynchronous circuit. The clock signal should be big enough to run the worst-case delay and this is the reason why synchronous circuit has worst case performance.

#### Clock Skew

Clock skew is defined as difference in arrival times of a clock signal at different block or stage. All modules of the synchronous circuit need to operate with a same clock in order to operate correctly. It is difficult to minimize the clock skew with a large circuit.

#### • Higher Power Consumption

As synchronous circuit is clocked by a global clock which include those which are not use at a certain cycle. It toggles some of the node unnecessarily and this causes higher power consumption. Other than that, switching of the gate and fanout problem at the root of the clock tree also consume a lot of power.

# • Easier Influenced by The Variations

Semiconductors mainly affected by process speed of fabrication, power supply voltage level and temperature. These three properties will cause a transistor to operate faster or slower. Synchronous circuit need to consider these physical properties across its entire range in order to ensure the device is functioning.

# • Worse Modularity and Composability

Synchronous designer always take serious consideration on satify the detailed interfacial timing specifications. Other than that, replacing new parts do not give advantage to synchronous circuit because one of the part changes, the clock frequency of the whole circuit also need to be changed either follows the old clock frequency or adjust other parts to suit the new clock frequency.

Asynchronous circuits also assume all signals are in binary but there is no same clock signal. Other than that, asynchronous circuits is self-timed instead of governed by a block clock signal. The components inside the circuits use handshaking between each other in order to communicate. A particular component only clocked when it is needed.

Unlike synchronous circuits, asynchronous circuits do not suffer from the problems stated above but it has a lot of advantages which stated below (Jens Sparsø & Steve 2001, p3-4):

## • Averange Case Performance

Asynchronous circuit is controlled by local communications which will direct initial the next computation when the other one is completed. When the computation completed early, the new one can start early and this is why asynchronous circuit does not exhibit worse case performance but an averange case performance.

# • No Clock Skew

Asynchronous circuit is built up with small self-timed circuit which means there is no global clock signal connected between each other. So, there is no need to worry about the clock skew.

# • Lower Power Consumption

Asynchronous circuit only toggles the block or stage when it is being used, thus reduring the power consumption.

# Robustness Towards Variations

The self-timed logic and processing logic in asynchronous circuit are located in the same area, both of them are affected by the same environmental changes so that it is more unaffected to transient changes.

# • Better Modularity and Composability

Asynchronous circuist is simply connect a proper module with a matching interfacial specifications which means sequences of events that take place but not include the timing of the event. It saves a lot of time when designing the asynchronous circuit because of no need to worry about the delays occur inside the individual module. Other than that, parts of the asynchronous circuit can be replaced by the new one in order to improve the performance.

## **1.2 Project Scope**

There is an enorous field of research which covers widely diverse techniques to the implementation of asynchronous design. However, this project will only focus on the goals listed below:

- Architecture of the asynchronous processor.

- Methodologies used to implement the asynchronous processor.

# **1.3 Project Objectives**

The main objective of this project is to design and synthesis the asynchronous RISC processor, and it still can be divided into several sub-objectives as stated below:

- Design Level

- To design and develop an asynchronous RISC processor that can meet all the specifications correctly by using Verilog HDL.

- Verification Level

- To develop a complete testbench to verify all the functional correctness of the asynchronous RISC processor.

- Synthesis Level

- To synthesis and integrate the asynchronous RISC processor which is the FPGA technology.

## 1.4 Impact, significance and contribution

As a summary to the problem statement, there is a lack of well-developed and well-founded 32-bit asynchronous RISC processor core-based development environment. The development environment refers to the availability of the following:

- A well-developed design document, which includes the chip specification, architecture specification and micro-architecture specification.

- A fully functional well-developed 32-bit asynchronous RISC architecture core in the form of synthesis-ready RTL written in Verilog HDL.

- A well-developed verification environment for the 32-bit asynchronous RISC core. The verification specification should contain suitable verification methodology, verification techniques, test plans, test bench architectures etc.

- A complete physical design in Field Programmable Gate Array (FPGA) with documented timing and resource usage information.

With the available well-developed basic 32-bit asynchronous RISC RTL model (which has been fully functional verified), the verification environment and the design documents, researchers can develop their own specific RTL model as part of the development environment (whether directly modifying the internals of the processor or interface to the processor) and can quickly verify their model to obtain results, without having to worry about the development of the verification environment and the modeling environment. This can speed up the research work significantly. For example, a researcher may have developed an image-processing algorithm and modified the algorithm to obtain a structure that suits the hardware implementation. The structure can be modeled in Verilog as part of a specialized data-path or as a coprocessor interfacing to the asynchronous RISC processor.

#### **1.5 Background information**

A circuit is considered to be asynchronous if it does not employ a periodic clock signal to synchronize its internal operations, an obvious example is asynchronous processor. Unlike a conventional processor, the asynchronous processor does not require a central clock to coordinate the progress of data through the pipeline. The first asynchronous design came out on 1952 and are widely used in computer during 1960's. However, during 1970's, the interest of asynchronous design dropped and disappeared after the appearance of synchronous design. The main reasons why was this happened are because of the rapidly growing of complexity of digital systems and the simplicity offered by synchronous design.

However, with the progress of time and the advance in technology, synchronous design showed up several problems when higher performance was a need. The problems include clock skew for high frequency systems, power consumption due to increase of portability of digital systems and worst case performance. The asynchronous design does not suffer from the problems. Therefore, attention of the researchers and designers were created. Today, the semiconductor industry is giving serious consideration to the adoption of asynchronous circuit technology. There are some projects from the industry have proven that the design of asynchronous circuit is achieve the significant benefits stated in (C.H. Van Berkel, M.B. Josephs & S.M. Nowick 1999, p224-230).

#### **Chapter 2 : Literature Review**

#### 2.1 Literature Review

There are several different asynchronous processors with their own architecture, type of communication and data transfer protocol discussed by (Tony Werner & Venkatesh Akella 1997, p.69-76) & (T.Samyuktha & K.Balachandra 2015, p.10208-10211).

**1. Caltech Asynchronous Processor (CAP)** (Alan Martin's group 1980s cited in Tony Werner & Venkatesh Akella 1997)

- Concurrent processes, 4-phase, dual-rail.

- The earliest known asynchronous processor.

- Dynamic logic families works efficiently with this design.

- 15 MIPS performance is estimated by the designers.

Figure 2.1 : The Caltech Asynchronous Processor

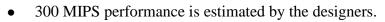

**2. Fully Asynchronous Processor (FAM)** (Kyoung.R.C, Kazum.O, Kunijiro.A 1990s cited in Tony Werner & Venkatesh Akella 1997)

- 4-stage pipeline (see Figure 2.2), 4-phase, dual-rail.

- The processor contains 32 bits data path and 32 of 32 bits general registers.

- Only 18 instructions are available for this processor. The method to design asynchronous data path and control path is achieved by this effort.

- It uses combined instruction and data cache (ALU and register file are combined). Disadvantage : Conflicts between the two stages need to be solved.

- Both computation block and interconnection block are used in this design. Each pipeline stage or computation block are separated by the interconnection block and provides space to separate the computation blocks.

- FAM uses at most two transistors in series to both set and reset the flip-flops which called 2-AND logic, describing the state of the system.

Figure 2.2 : The Fully Asynchronous Processor

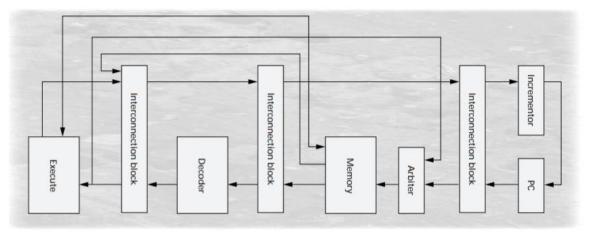

**3. Non synchronous RISC (NSR)** (Erik.B 1993 cited in Tony Werner & Venkatesh Akella 1997)

- 5-stage pipeline (see Figure 2.3), 2-phase, bounded-delay.

- The processor contains sixteen 16-bit registers.

- FIFO queues are added between the concurrent blocks to minimize stalls caused by slower instructions. Each stage accepts data for processing and passes the result to the next stage by way of FIFO. Potentially, FIFO could greatly increases the penalties from memory access, branching and so on. However, the instructions will only pass through the stages which are needed.

- The validity of the data path is ensured by adding delay to the control path which called bounded-delay.

• 1.3MIPS perfromance is reported by the disigners.

Figure 2.3 : The Non synchronous RISC

# 4. Counter Flow Pipeline Processor (CFPP) (Ivan.S 1994 cited in Tony Werner

& Venkatesh Akella 1997)

- 12 stages pipeline (see Figure 2.4).

- For this processor, the data generated by the instructions flow at opposite direction of the instructions through the pipeline.

- It places program counter and register file at both end respectively. Before the packets send to the register file, instruction with opcode, source and destination register binding, and possibly the corresponding program counter are inserted. Before the instruction is send back to the program counter, it reads the source operands and then only inserts the instruction into the pipeline.

- The instruction packet must match with its source operands is the only requirement to execute in every stage of pipeline.

- This architecture provide register renaming. When the instrction reaches the register file, it does not need to wait to receive its source operands. However, the source operands from the result pipeline will be recerived maybe before updating the register file.

- This processor supports interrupts and a wrongly predicted branches can be recoverd by inserting an identifier into the results pipeline. The instructions in front of the identifier keep on move to the register file and their results are still posted. However, it prevent alter of rigister file by marking the instructions which follow the indentifier. It will enters interrupt routine or loads the correct branch destination when the identifier reached the program counter.

- Long computation delay instructions are executed by using auxiliary stages or "siblings".

Figure 2.4 : The Counter Flow Pipeline Processor

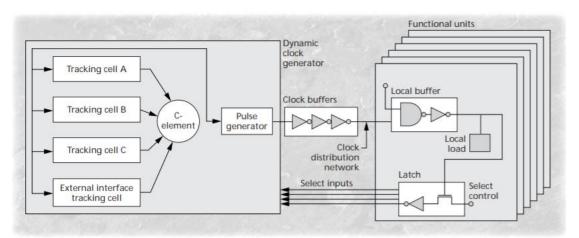

**5. Self-Timed RISC Processor (STRIP)** (Mark.D cited in Tony Werner & Venkatesh Akella 1997)

- 5-stage pipeline, dynamic clock, bounded-delay.

- It is a synchronous processor with an adjustable clock, called dynamic clocking.

- The slowest critical path of current clock cycle determines the clock period. Optimization for every stage of pipeline and functional unit are needed.

- C-element and simple pulse generator are used by STRIP. The propagation delay of a particular critical path represented by a tracking cell. An active critical paths determine the clock cycle because the processor will moves those tracking cells which are not needed for to their next state. Each tracking cells is then input to C-element. When all tracking cells are completed, the C-element changes to its next state. The tracking cells are restarted and the pulse generator is activated (see Figure 2.5).

- The external interface operates on four phases and dual rail protocol.

- It supports precise interrupts because an instructions cannot change the processor's state until the write-back stage. The instructions are stopped and the program counter will set to zero to begin the exception handling when an interrupt occurs. The addresses of the register fetch and

instruction decode, ALU and data memory access stages will be saved by the processor. Restarting the instructions that occupied these stages are required to recover from the interrupt.

• The memory access time decides the performance of the processor. It places memory buffers between each instruction and data memory paths in order to minimize the memory access latency.

• 62.5 MIPS performance is reported by the designers.

Figure 2.5 : The structure of the STRIP processor

**6. Superscalar Asynchronous Low Power Processor (SCALP)** (University of Manchester 1996 cited in T.Samyuktha & K.Balachandra 2015)

- Each instruction only specifies the destination of the results but not the source of their operands. However, they use the values provided by instruction before it.

- Each instruction has a functional unit identifier which indicates which functional unit will execute the instruction.

# 7. AMULET1 (Steve.F cited in T.Samyuktha & K.Balachandra 2015)

- 6-stage pipeline, 2-phase, bounded-delay.

- Contains thirty 32-bit general registers for register bank. Only 16 are able to access once, 15<sup>th</sup> register contains the program counter.

- First fully functional asynchronous processor.

- Two levels of interrupts and the exceptions generated by virtual memory system are supported by this processor.

- FIFO structure called pc pipe uses to keep the record of program counter values. If needed, the value which is at the top of the FIFO queue is transferred along with the instruction to the execute unit. Otherwise, the value is removed.

- It uses lock FIFO to eliminate register hazards.

- The physical size and transistor count are reduced by utilizing dynamic logic of the register bank and execute unit.

Figure 2.6 : Amulet1 processor organization

**8. AMULET2e - An Asynchronous Embedded Controller** (Steve.F cited in T.Samyuktha & K.Balachandra 2015)

- It is designed as embedded system chip with an enhanced ARM core a 4Kbyte pipelined cache, a flexible memory interface and assorted programmable control functions.

- It also consists of counter-timer for real time reference.

- AMULET2e silicon demonstrates competitive performance, power efficiency and ease of design.

- Pipeline reorganization was done with respect to AMULET1.

9. AMULET3 (Steve.F cited in T.Samyuktha & K.Balachandra 2015)

- It is a fully asynchronous implementation of ARM architecture which including 16 bit thumb instruction set.

- Suitable for low power processor.

- It is equal to a 32-bit embedded processor in energy efficiency and was developed for microcontroller applications.

# 2.2 Data Collection

The table below shows the comparison between several asynchronous processors with diffrent architecture, protocol, technology and performance discussed by (Tony Werner & Venkatesh Akella 1997, p.69-76) & (T.Samyuktha & K.Balachandra 2015, p.10208-10211).

| Microprocessor                                | Architecture            | Protocol                  | Technology       | Performance   |

|-----------------------------------------------|-------------------------|---------------------------|------------------|---------------|

| Caltech<br>Asynchronous<br>Processor<br>(CAP) | Concurrent<br>processes | 4-phase,<br>dual-rail     | 2 - µm CMOS      | 15 MIPS       |

| Fully<br>Asynchronous<br>Processor<br>(FAM)   | 4-stage<br>pipeline     | 4-phase,<br>dual-rail     | 0.5 - μm<br>CMOS | 300 MIPS      |

| Non<br>synchronous<br>RISC (NSR)              | 5-stage<br>pipeline     | 2-phase,<br>bounded-delay | Actel FPGAs      | 1.3 MIPS      |

| Self-Timed<br>RISC Processor<br>(STRIP)       | 5-stage<br>pipeline     | dynamic clock             | 2 - µm CMOS      | 62.5 MIPS     |

| AMULET1                                       | 6-stage<br>pipeline     | 2-phase,<br>bounded-delay | 1 - µm CMOS      | 9K Dhrystones |

Table 2.1 : Comparison between different type of asynchronous processor

#### 2.3 Critical Remarks of Previous Works

It can been seen that asynchronous circuits have more advantages than synchronous circuits but it also have its own limitations. These limitations are stated below (Hans Jacobson 1996, p15-16):

- **Hazards.** Asynchronous circuits are easily influenced by glitches and hazards because it depend on the events within the wire to communicate. Therefore, it is important to take care of it during state of synthesis in order to remove the chance of function and logic hazards. Other than that, the result of the circuit is also sensitive to glitches.

- Latency with Handshake. The method where asynchronous circuits used to communicate will slow down the performance due to handshake overhead. The communicating elements are put close to each other in order to solve the problem.

- Different Design Methodologies. Inconsistent of specification and implementation styles caused by different methodologies used to design the asynchronous circuit. It is hard to compare the differences of those systems and also difficult to pull off on exiting works.

- Immature Synthesis Methodologies. There is a must for mature synthesis methodologies in order to let asynchronous design to be accepted by those synchronous designers and industry. Unfortunately, there are many methods are still in their early stages of research. Other than that, it also has not yet been modeled with real industrial designs.

### **Chapter 3 : Hardware Development**

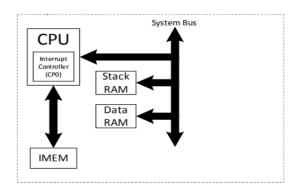

### 3.1 System Overview

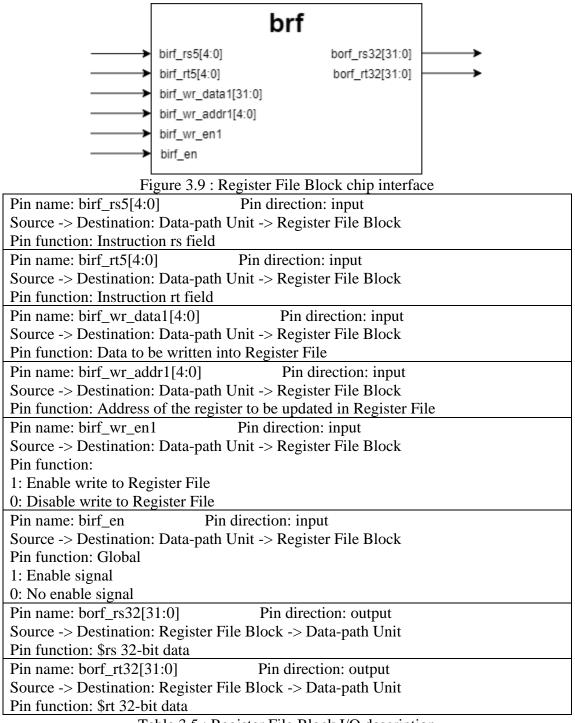

The asynchronous RISC processor built with 2 major parts which are Central Processing Unit (CPU) and Memory Unit. It is compatible to a 5-stage 32-bit MIPS Instruction Set Architecture (ISA). It supports instructions included arithmetic, logic, data memory access, program control and etc. The memory unit consists of Boot ROM, Stack RAM and Data RAM.

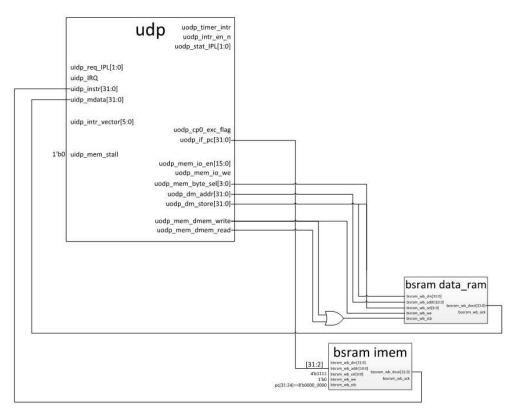

Figure 3.1 : The overview of the processor

## **3.1.1 Design Hierarchy**

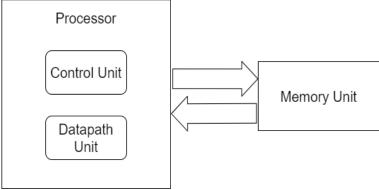

Other than that, the processor is divided into two main units which are datapath unit and control unit. Datapath unit is a collection of functional units and control unit is to generate control signals to datapath. Moreover, both datapath unit and control unit can be further split into smaller blocks. (Chip -> Unit -> Block)

Figure 3.2 : Micro-architecture of the processor

|       |                   | Address Decoder Block                    | ]                   |

|-------|-------------------|------------------------------------------|---------------------|

|       |                   | (baddr_decoder)                          |                     |

|       |                   | ALU Block                                | -                   |

|       |                   | (balb)                                   |                     |

|       |                   | Forwarding Block                         | -                   |

|       |                   | (bfwl_ctrl)                              |                     |

|       |                   | Interlock Block                          | -                   |

|       |                   | (bitl_ctrl)                              |                     |

|       |                   |                                          | adder_lvl1          |

|       |                   |                                          | adder_lvl1_firstrow |

|       | Detenath Unit     |                                          | add_lvl1_lastrow    |

|       | Datapath Unit     | Multiplier Dlock                         | adder_lv12          |

|       | (udata_path)      | Multiplier Block<br>(bmult32)            | adder_lvl2_lastrow  |

|       |                   | (0)(0)(0)(0)(0)(0)(0)(0)(0)(0)(0)(0)(0)( | adder_lv13          |

|       |                   |                                          | adder_lvl4          |

| crisc |                   |                                          | adder_lv15          |

| ense  |                   |                                          | sub_lvl1_lastrow    |

|       |                   | Register Block                           |                     |

|       |                   | (brf)                                    |                     |

|       |                   |                                          | Muller C Gate       |

|       |                   | Muller Pipeline Block                    | (mcg)               |

|       |                   | (bmp)                                    | Muller C Element    |

|       |                   |                                          | (mce)               |

|       |                   | Arithmetic Logic Control Block           |                     |

|       | Control Path Unit | (balb_ctrl)                              |                     |

|       | (uctrl_path)      | Main Control Block                       |                     |

|       |                   | (bmain_ctrl)                             |                     |

|       | Data and Stack    |                                          |                     |

|       | RAM Unit          |                                          |                     |

|       | (uram)            |                                          |                     |

|       | Boot ROM Unit     |                                          |                     |

|       | (uboot_rom)       | 1. Design hierorghy of the processo      |                     |

Table 3.1 : Design hierarchy of the processor

# **3.1.2 Internal Operation**

## Stage 1 : Instruction Fetch (IF)

- Intruction fetched from instruction memory

- Pragram counter (PC) incremented

# **Stage 2 : Instruction Decode (ID)**

- Opcode and funct are gathered and decoded

- Read data from register file

# Stage 3 : Execution (EX)

- Execute R-type, calculate memory address

- Computation of most instructions are done except jump

# Stage 4 : Memory (MEM)

- Read/write the data from/to the data memory

- Only load and store instructions are active in this stage

# Stage 5 : Write Back (WB)

• Write the result data into the register file

Figure 3.3 : Instruction execution cycle

# 3.1.3 Memory Map

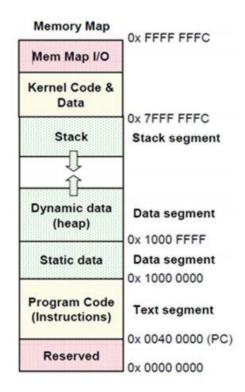

Figure 3.4 : Memory map

MIPS memory location is divided into 3 parts, namely text segment, data segment and stack segment.

**Text segment** (0x0040 0000 - 0xFFFF FFFC) is used to hold the program's instruction.

Data segment is divided into:

-Static data segment (0x1000 0000 - 0x1000 FFFB)

- Holds object whose lifetime is the program's entire execution

- Cease to exist only after execution completes

- -Dynamic data segment or heap (0x1000 FFFF ?)

- Holds variables declared dynamically as in structures that grow and shrink

• Heap size is not known in advance, so locations are not assigned during compile time.

**Stack segment** (0x7FFF FFFC - ?) is used by procedure during execution to store register values. Stack size is not known in advance, so locations are not assigned during compile time

# **3.2 CPU**

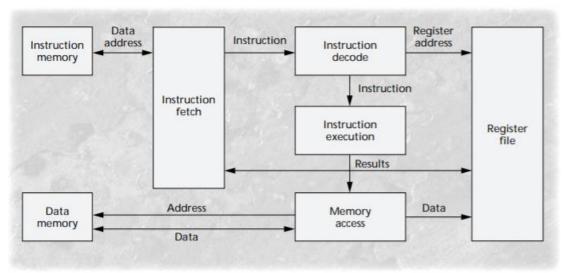

## 3.2.1 Pipeline Micro-architecture

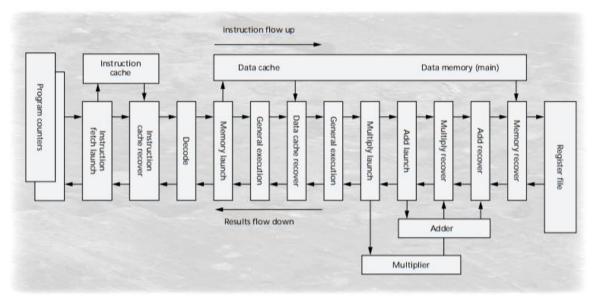

At IF stage, an instruction is fetched from the Boot ROM or I-MEM and registered to the IF/ID pipeline registers. At ID stage, the instruction that registered in the IF/ID pipeline registers will be decoded by the Main Control block and the Arithmetic Logic Control block. Signals output from both hardware components will be registered to the ID/EX pipeline registers and also pass to the remaining hardware components in the ID stage, i.e. Register File. At the same time, IF stage continues to fetch the consecutive instruction from the I-MEM. At EX stage, ALU block covers all the operation except the multiplication operation. Multiplier block starts the multiplication operation at EX stage and requires 2 clock cycles (EX and MEM stages) to perform a multiplication operation on two 32-bit operands. At the MEM stage, only load and store instructions are permitted to perform the operation, in which other instructions are bypassing this stage. Load or store instruction is used to access the memory components at the MEM stage, i.e. D-MEM and Data and Stack RAM. At WB stage, the result of the operation is updated. Data hazards always exist in a pipeline processor.

Data hazards can cause the computational error when multiple instructions are overlapped during execution. The data hazard occurs due to Read-after-Write (RAW) data dependencies, which involve accessing the processor's system registers, i.e. Register File and HILO register. Extra circuitries (forwarding and interlock) are required to resolve the data hazards arise. However, the high computational speed achieved by pipelined processor still outweighs its counterparts and remains a popular choice in processor design.

Figure 3.6 : Micro-architecture of datapath with memory unit

# 3.3 Design Block Specification

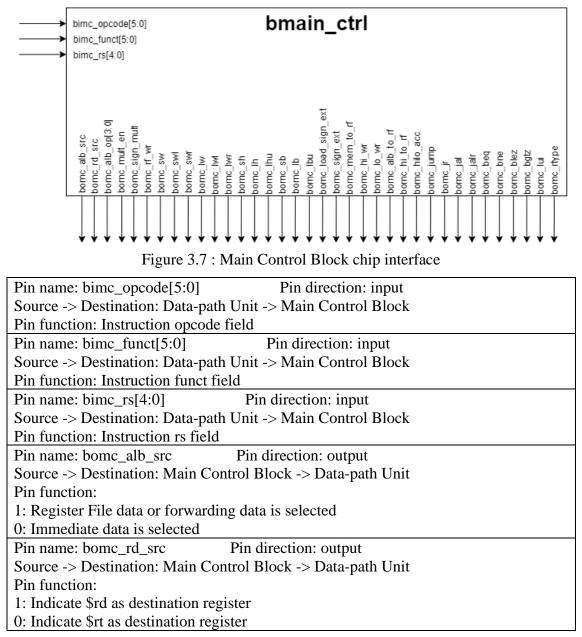

# **3.3.1 Main Control Block**

The Main Control block is used to decode a 32-bit instruction machine code and generate control signals to represent the unique identity of each instruction. The control signals identify the source of operands, destination to save the result and the respective operation to operate. The Main Control block consists of only combinational logic, which the decoding can be done within one clock cycle. Figure 3.7 shows the chip interface of the Main Control Block and describes the function of each pin on Main Control Block.

| Pin name: bomc_alb_op[3:0]   Pin direction: output                          |

|-----------------------------------------------------------------------------|

| Source -> Destination: Main Control Block -> Arithmetic Logic Control Block |

| Pin function: Encoded opcode for Arithmetic Logic Control Block to produce  |

| optimized signal to ALU                                                     |

| Pin name: bomc_mult_en     Pin direction: output                            |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function:                                                               |

|                                                                             |

| 1: Indicate mult instruction is executing                                   |

| 0: Indicate mult instruction is not execute                                 |

| Pin name: bomc_sign_mult Pin direction: output                              |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function:                                                               |

| 1: Indicate mult or multu instruction is executing                          |

| 0: Indicate mult and multu instruction is not executing                     |

| Pin name: bomc_rf_wrPin direction: output                                   |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function:                                                               |

| 1: Enable write to Register File                                            |

| 0: Disable write to Register File                                           |

| Pin name: bomc_sw Pin direction: output                                     |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function: Store word (32-bit data)                                      |

| 1: Indicate sw, swl or swr instruction is executing                         |

| 0: Indicate sw, swl and swr instructions are not executing                  |

| Pin name: bomc_swl Pin direction: output                                    |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function: Unaligned store word left (32-bit data)                       |

| 1: Indicate swl instruction is executing                                    |

| 0: Indicate swl instruction is not executing                                |

| Pin name: bomc_swr Pin direction: output                                    |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function: Unaligned store word right (32-bit data)                      |

| 1: Indicate swr instruction is executing                                    |

| 0: Indicate swr instruction is not executing                                |

| Pin name: bomc_lw   Pin direction: output                                   |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function: Load word (32-bit data)                                       |

| 1: Indicate lw, lwl or lwr instruction is executing                         |

| 0: Indicate lw, lwl and lwr instructions are not executing                  |

| Pin name:     bomc_lwl     Pin direction:     output                        |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function: Unaligned load word left (32-bit data)                        |

| 1: Indicate lwl instruction is executing                                    |

| 0: Indicate lwl instruction is not executing                                |

| Pin name:     bomc_lwr     Pin direction:     output                        |

| Source -> Destination: Main Control Block -> Data-path Unit                 |

| Pin function: Unaligned load word right (32-bit data)                       |

|                                                                             |

| 1: Indicate lwr instruction is executing                                    |

| 0: Indicate lwr instruction is not executing                                |

| Pin name: bomc_shPin direction: output                                      |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

|-----------------------------------------------------------------------------------------|

| Pin function: Store half-word (16-bit data)                                             |

| 1: Indicate sh instruction is executing                                                 |

| 0: Indicate sh instruction is not executing                                             |

| Pin name: bomc_sh Pin direction: output                                                 |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function: Store half-word (16-bit data)                                             |

| 1: Indicate sh instruction is executing                                                 |

| 0: Indicate sh instruction is not executing                                             |

| Pin name: bomc_lhu Pin direction: output                                                |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function: Load half-word unsigned (16-bit data)                                     |

| 1: Indicate lhu instruction is executing                                                |

| 0: Indicate lhu instruction is not executing                                            |

| Pin name: bomc_sb Pin direction: output                                                 |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function: Store byte (8-bit data)                                                   |

| 1: Indicate sb instruction is executing                                                 |

| 0: Indicate sb instruction is not executing                                             |

| Pin name: bomc_lb Pin direction: output                                                 |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function: Load byte (8-bit data), sign extend required (refer uipr_load_sign_ext)   |

| 1: Indicate lb instruction is executing                                                 |

| 0: Indicate lb instruction is not executing                                             |

| Pin name: bomc_lbu Pin direction: output                                                |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function: Load byte unsigned (8-bit data)                                           |

| 1: Indicate lbu instruction is executing                                                |

| 0: Indicate lbu instruction is not executing                                            |

| Pin name: bomc_load_sign_ext Pin direction: output                                      |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function:                                                                           |

| 1: Indicate lh or lb instruction is executing, sign extend 16-bit to lh or 24-bit to lb |

| 0: Indicate lh or lb instructions are not executing                                     |

| Pin name: bomc_sign_ext Pin direction: output                                           |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function:                                                                           |

| 1: Immediate data sign extend                                                           |

| 0: Immediate data zero extend                                                           |

| Pin name: bomc_mem_to_rfPin direction: output                                           |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function:                                                                           |

| 1: Data memory data to Register File                                                    |

| 0: ALU block result to Register File                                                    |

| Pin name: bomc_alb_to_rf Pin direction: output                                          |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function: Reserved for future development                                           |

| Pin name: bomc_hi_to_rf Pin direction: output                                           |

| Source -> Destination: Main Control Block -> Data-path Unit                             |

| Pin function:                                                                           |

|                                                                                         |

| 1. III register data ta Degister Eila                       |

|-------------------------------------------------------------|

| 1: HI register data to Register File                        |

| 0: LO register data to Register File                        |

| Pin name: bomc_hilo_acc Pin direction: output               |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate mflo or mfhi instruction is executing           |

| 0: Indicate mflo and mfhi instructions are not executing    |

| Pin name: bomc_jump Pin direction: output                   |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate j instruction is executing                      |

| 0: Indicate j instruction is not executing                  |

| Pin name: bomc_jrPin direction: output                      |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate jr instruction is executing                     |

| 0: Indicate jr instruction is not executing                 |

| Pin name: bomc_jal Pin direction: output                    |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate jal instruction is executing                    |

| 0: Indicate jal instruction is not executing                |

| Pin name: bomc_jalrPin direction: output                    |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate jalr instruction is executing                   |

| 0: Indicate jalr instruction is not executing               |

| Pin name: bomc_beq Pin direction: output                    |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate beq instruction is executing                    |

| 0: Indicate beq instruction is not executing                |

| Pin name: bomc_bne Pin direction: output                    |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate bne instruction is executing                    |

| 0: Indicate bne instruction is not executing                |

| Pin name: bomc_blez Pin direction: output                   |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate blez instruction is executing                   |

| 0: Indicate blez instruction is not executing               |

| Pin name: bomc_bgtz Pin direction: output                   |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate bgtz instruction is executing                   |

| 0: Indicate bgtz instruction is not executing               |

| Pin name: bomc_lui Pin direction: output                    |

| Source -> Destination: Main Control Block -> Data-path Unit |

| Pin function:                                               |

| 1: Indicate lui instruction is               | executing                              |  |  |  |  |

|----------------------------------------------|----------------------------------------|--|--|--|--|

| 0: Indicate lui instruction is not executing |                                        |  |  |  |  |

| Pin name: bomc_rtype                         | Pin direction: output                  |  |  |  |  |

| Source -> Destination: Mai                   | n Control Block -> Data-path Unit      |  |  |  |  |

| Pin function:                                |                                        |  |  |  |  |

| 1: Indicate R-type instruction               | on is executing                        |  |  |  |  |

| 0: Indicate I-type or J-type                 | instruction is executing               |  |  |  |  |

| Table 3                                      | 2 : Main Control Block I/O description |  |  |  |  |

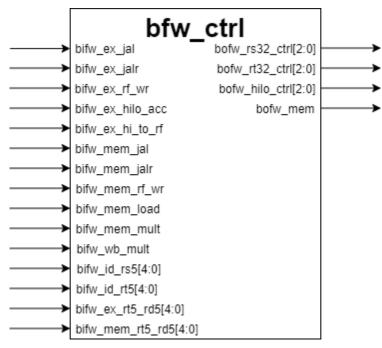

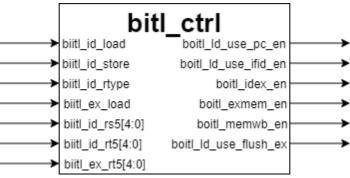

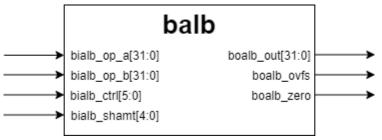

# **3.3.2 Arithmetic Logic Control Block**

The Arithmetic Logic Control block generates the optimized control signals which will be used by the ALU block to perform the operation. The decoding is completed within one clock cycle. The chip interface of the Arithmetic Logic Control Block is shown in Figure 3.8.

Figure 3.8 : Arithmetic Logic Control Block chip interface

| Pin name: bialc_funct[5:0]Pin direction: input                                     |

|------------------------------------------------------------------------------------|

|                                                                                    |

| Source -> Destination: PR unit -> Arithmetic Logic Control Block                   |

| Pin function: Instruction funct field                                              |

| Pin name: bialc_op[3:0]Pin direction: input                                        |

| Source -> Destination: Main Control Block -> Arithmetic Logic Control Block        |

| Pin function: Decoded ALU operation signal from Main Control Block                 |

| Pin name: boalc_ctrl[5:0]Pin direction: output                                     |

| Source -> Destination: Arithmetic Logic Control Block -> PR unit -> Data-path Unit |

| Pin function:                                                                      |

| boalc_ctrl[5]-1: Disable sign overflow                                             |

| 0: Enable sign overflow to occurs                                                  |

| boalc_ctrl[4]-1: Inverting operand B of the ALU to perform subtraction             |

| 0: No invert required                                                              |

| boalc_ctrl[3:2]- 00: Final output from the shift operation                         |

| 01: Final output from the logical operation                                        |

| 10: Final output from the summation                                                |

| 11: Final output from the set-on-less-than operation                               |

| Table 3.3 : Arithmetic Logic Control Block I/O description                         |

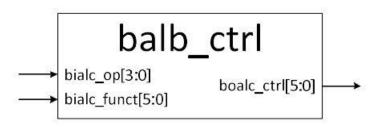

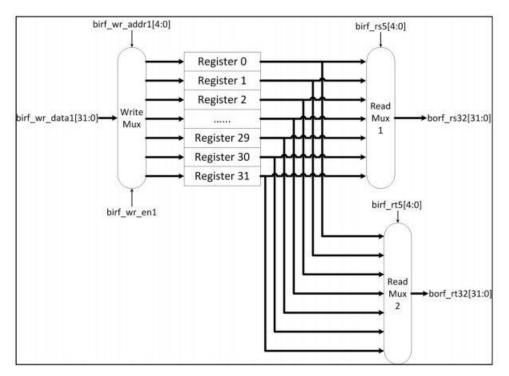

## **3.3.3 Register File Block**

The Register File block consists of thirty-two 32-bit registers. It is designed with dual read ports and single write port to accommodate the register accessing requirement from the MIPS ISA. Source register operand (\$rs) and target register operand (\$rt) specify for the registers read address, while either target register operand (\$rt) or destination register operand (\$rd) specify the register write address. Table 3.4 shows the conventional usage of each register in the Register File set by MIPS ISA.

| Register | Code  | Register | Usage                                                 |  |  |

|----------|-------|----------|-------------------------------------------------------|--|--|

| No.      |       | Name     |                                                       |  |  |

| 0        | 00000 | \$zero   | The constant value 0                                  |  |  |

| 1        | 00001 | \$at     | Assembler temporary                                   |  |  |

| 2        | 00010 | \$v0     | Values for function results and expression evaluation |  |  |

| 3        | 00011 | \$v1     | Values for function results and expression evaluation |  |  |

| 4        | 00100 | \$a0     | Arguments                                             |  |  |

| 5        | 00101 | \$a1     | Arguments                                             |  |  |

| 6        | 00110 | \$a2     | Arguments                                             |  |  |

| 7        | 00111 | \$a3     | Arguments                                             |  |  |

| 8        | 01000 | \$t0     | Temporaries                                           |  |  |

| 9        | 01001 | \$t1     | Temporaries                                           |  |  |

| 10       | 01010 | \$t2     | Temporaries                                           |  |  |

| 11       | 01011 | \$t3     | Temporaries                                           |  |  |

| 12       | 01100 | \$t4     | Temporaries                                           |  |  |

| 13       | 01101 | \$t5     | Temporaries                                           |  |  |

| 14       | 01110 | \$t6     | Temporaries                                           |  |  |

| 15       | 01111 | \$t7     | Temporaries                                           |  |  |

| 16       | 10000 | \$s0     | Saved temporaries                                     |  |  |

| 17       | 10001 | \$s1     | Saved temporaries                                     |  |  |

| 18       | 10010 | \$s2     | Saved temporaries                                     |  |  |

| 19       | 10011 | \$s3     | Saved temporaries                                     |  |  |

| 20       | 10100 | \$s4     | Saved temporaries                                     |  |  |

| 21       | 10101 | \$s5     | Saved temporaries                                     |  |  |

| 22       | 10110 | \$s6     | Saved temporaries                                     |  |  |

| 23       | 10111 | \$s7     | Saved temporaries                                     |  |  |

| 24       | 11000 | \$t8     | Temporaries                                           |  |  |

| 25       | 11001 | \$t9     | Temporaries                                           |  |  |

| 26       | 11010 | \$k0     | Reserved for OS kernel                                |  |  |

| 27       | 11011 | \$k1     | Reserved for OS kernel                                |  |  |

| 28       | 11100 | \$gp     | Global pointer                                        |  |  |

| 29       | 11101 | \$sp     | Stack pointer                                         |  |  |

| 30       | 11110 | \$fp     | Frame pointer                                         |  |  |

| 31       | 11111 | \$ra     | Return address                                        |  |  |

Table 3.4 : Conventional usange of the registers in Register File Block

Table 3.5 : Register File Block I/O description

Figure 3.10 describes the internal operation of the Register File block. There are three 5-bit multiplexers used to select over thirty-two registers. The write access to the register starts when enable is asserted while the combinational read accesses of the registers allow the updated result to be used in the consecutive instruction. This is to avoid the data hazard that might arise when both read and write access to the same register happen at the same time.

Figure 3.10 : Internal operation of Register File Block

#### **3.3.4 Forwarding Block**

Data hazards exist when the processor is designed in the pipeline structure. Data hazard occurs due to Read-after-Write (RAW) data dependency. According to MIPS ISA, Register File block will only be updated at WB stage. Both read (ID stage) and write (WB stage) to Register File block is occurred in two different stages, thus, an instruction may attempt to read Register File block before it is updated with the latest data. Our approach resolves all the data hazards (except load-use hazard) that might arise within the range of basic MIPS ISA core instructions, using the Forwarding block. The data hazards that can be resolved using data forwarding are divided into 4 groups in relation to the system registers: General Condition of Register File, \$ra Register, Load-store and HILO Register.

For General Condition of Register File related data hazards, the data forwarding is performed as earlier as possible, i.e. from EX or MEM stages to ID stage. This can reduce the power consumption and pipeline size due to lesser control unit signals passing through the pipeline structure. Another small advantage is to balance the stage propagation delay of ID and EX stage: the propagation delay of ALU in EX stage is longer than RF in ID stage. Table 3.6 shows the combination of instructions that causes data hazard grouped under general condition of Register File related data hazards.

| 1  | add \$1, \$1, \$1    | 2  | add \$1, \$1, 0x0    | 3  | add \$1, \$1, \$1    | 4  | addi \$1, \$1, 0x0   |

|----|----------------------|----|----------------------|----|----------------------|----|----------------------|

| 1  | add \$1, \$1, \$1    | 2  | add \$1, \$1, \$1    | 5  | addi \$1, \$1, 0x0   | +  | addi \$1, \$1, 0x0   |

| 5  | add \$1, \$1, \$1    | 6  | addi \$1, \$1, 0x0   | 7  | add \$1, \$1, \$1    | 8  | addi \$1, \$1, 0x0   |

| 5  | lw \$1, 100(\$1)     | 0  | lw \$1, 100(\$1)     | /  | sw \$1, 100(\$1)     | 0  | sw \$1, 100(\$1)     |

| 9  | add \$1, \$1, \$1    | 10 | addi \$1, \$1, 0x0   | 11 | add \$ra, \$ra, \$ra | 10 | addi \$ra, \$ra, 0x0 |

| 7  | beq \$1, \$1, 100    | 10 | beq \$1, \$1, 100    | 11 | jr \$ra              | 10 | jr \$ra              |

| 13 | add \$1, \$1, \$1    | 14 | addi \$1, \$1, 0x0   | 15 | add \$1, \$1, \$1    | 16 | addi \$1, \$1, 0x0   |

| 15 | mult \$1, \$1        | 14 | mult \$1, \$1        | 15 | mtc0 \$1, \$epc      | 10 | mtc0 \$1, \$epc      |

|    | add \$ra, \$ra, \$ra |    | addi \$ra, \$ra, 0x0 |    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |

| 17 | jalr \$ra            | 18 | jalr \$ra            | 19 | nop                  | 20 | nop                  |

|    | jan qia              |    | jan sia              |    | add \$1, \$1, \$1    |    | add \$1, \$1, \$1    |

|    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |

| 21 | nop                  | 22 | nop                  | 23 | nop                  | 24 | nop                  |

|    | addi \$1, \$1, 0x0   |    | addi \$1, \$1, 0x0   |    | lw \$1, 100(\$1)     |    | lw \$1, 100(\$1)     |

|    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |

| 25 | nop                  | 26 | nop                  | 27 | nop                  | 28 | nop                  |

|    | sw \$1, 100(\$1)     |    | sw \$1, 100(\$1)     |    | beq \$1, \$1, 100    |    | beq \$1, \$1, 100    |

|    | add \$ra, \$ra, \$ra |    | addi \$ra, \$ra, 0x0 |    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |

| 29 | nop                  | 30 | nop                  | 31 | nop                  | 32 | nop                  |

|    | jr \$ra              |    | jr \$ra              |    | mult \$1, \$1        |    | mult \$1, \$1        |

|    | add \$1, \$1, \$1    |    | addi \$1, \$1, 0x0   |    | add \$ra, \$ra, \$ra |    | addi \$ra, \$ra, 0x0 |

| 33 | nop                  | 34 | nop                  | 35 | nop                  | 36 | nop                  |

|    | mtc0 \$1, \$epc      |    | mtc0 \$1, \$epc      |    | jalr \$ra            |    | jalr \$ra            |

|    | lw \$1, 100(\$1)     |

| 37 | nop                  | 38 | nop                  | 39 | nop                  | 40 | nop                  |

|    | lw \$1, 100(\$1)     |    | sw \$1, 100(\$1)     |    | mult \$1, \$1        |    | mult \$1, \$1        |

|    | lw \$1, 100(\$1)     |    | lw \$1, 100(\$1)     |    | lw \$1, 100(\$1)     |    |                      |

| 41 | nop                  | 42 | nop                  | 43 | nop                  |    |                      |

|    | jr \$ra              |    | jalr \$ra            |    | mtc0 \$1, \$epc      |    |                      |

|    |                      |    |                      |    |                      |    |                      |

Table 3.6 : General condition of Register File related data hazards

The \$ra register related data hazards arises when the processor issued an unconditional branch instruction such as jump and link, (jal) and jump and link register, (jalr) which updates the \$ra register with the address of the next instruction (PC+4). However, the consecutive instruction right after jal or jalr will read the old value of \$ra register at ID stage. jal will update the \$ra register at WB stage, but the corresponding address value (PC+4) in \$ra register is needed earlier by the consecutive instructions at ID stage. Thus, data forwarding should take place to resolve this problem. Table 3.7 shows the combination of instructions that causes data hazard grouped under \$ra register related data hazards.

|                                 |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                      |                                                        |                                                         |                                                        |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| jal 10000<br>add \$ra_\$ra_\$ra | 2                                                                                                                                                                                                                                                                                                         | jalr \$ra<br>add \$ra_\$ra_\$ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                                                      | jal 10000<br>lw \$ra_100(\$ra)                         | 4                                                       | jalr \$ra<br>lw \$ra, 100(\$ra)                        |