# DESIGN OF A DIRECT MEMORY ACCESS MODULE FOR 32-BIT RISC32 PROCESSOR

BY

TAN E-CHIAN

## A REPORT

#### SUBMITTED TO

Universiti Tunku Abdul Rahman

in partial fulfillment of the requirements

for the degree of

#### BACHELOR OF COMPUTER ENGINEERING (HONOURS)

Faculty of Information and Communication Technology

(Kampar Campus)

JAN 2022

# UNIVERSITI TUNKU ABDUL RAHMAN

| <b>Fitle</b> :                                                         | Design of a Direct Memory Ac                                                                                   | ccess Module for 32-Bit RISC32 Processor                                                      |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|                                                                        | Acaden                                                                                                         | nic Session: JAN 2022                                                                         |

| I                                                                      | TAN E-CHIAN                                                                                                    |                                                                                               |

| 1. The                                                                 | dissertation is a property of the Libr                                                                         | eject to the regulations as follows:<br>ary.<br>f this dissertation for academic purposes.    |

| 1. The                                                                 | dissertation is a property of the Libr                                                                         | ary.                                                                                          |

| 1. The                                                                 | dissertation is a property of the Libr                                                                         | ary.                                                                                          |

| 1. The 2. The 2.                                                       | dissertation is a property of the Libr                                                                         | ary.<br>f this dissertation for academic purposes.                                            |

| 1. The<br>2. The<br>(Author'<br>Address                                | dissertation is a property of the Libr<br>Library is allowed to make copies o                                  | rary.<br>f this dissertation for academic purposes.<br>Verified by,                           |

| 1. The<br>2. The<br>(Author'<br>Address<br>16, Jala                    | dissertation is a property of the Libr<br>Library is allowed to make copies o                                  | rary.<br>f this dissertation for academic purposes.<br>Verified by,                           |

| 1. The<br>2. The<br>2. The<br>(Author'<br>Address<br>16, Jala<br>Taman | dissertation is a property of the Libr<br>Library is allowed to make copies o<br>s signature)<br>an Mutiara 1, | ary.<br>f this dissertation for academic purposes.<br>Verified by,<br>Gupervisor's signature) |

Bachelor of Information Technology (Honours) Computer Engineering

Faculty of Information and Communication Technology (Kampar Campus), UTAR

| INFORMATION TECHNOLOGY AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FACULTY/INSTITUTE* OF COMMUNICATION TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| UNIVERSITI TUNKU ABDUL RAHMAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21/4/2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Date:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SUBMISSION OF FINAL YEAR PROJECT /DISSERTATION/THESIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| It is hereby certified that Tan E-Chian (ID No:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1705490       ) has completed this final year project/ dissertation/ thesis* entitled         Design of a Direct Memory Access Module<br>for 32-Bit RISC32 Processor       under the supervision of<br>Computer and       Ts Dr. Chang Jing Jing         (Supervisor) from the Department of Technology       Gommunication       Faculty/Institute* of         Information and Communication       and Ts Dr. Ooi Chek Yee       (Co-Supervisor)* from the<br>Computer and Communication         Department       of       Technology       Faculty/Institute*         Information and Communication       Technology       Faculty/Institute*         Technology       .       .         Information and Communication       Faculty/Institute*       of         Department       of       Technology       Faculty/Institute*         Information and Communication       Faculty/Institute*       of         Department       of       Technology       Faculty/Institute*         Information and Communication       .       .       .         Technology       .       .       .       .         Information and Communication       .       .       .       .         Information and Communication       .       .       .       .       .         Information and Communication       . |

| pdf format into UTAR Institutional Repository, which may be made accessible to UTAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| community and public.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Yours truly.<br>(Student Name)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

\*Delete whichever not applicable

# **DECLARATION OF ORIGINALITY**

I declare that this report entitled "**DESIGN OF A DIRECT MEMORY ACCESS MODULE FOR 32-BIT RISC32 PROCESSOR**" is my own work except as cited in the references. The report has not been accepted for any degree and is not being submitted concurrently in candidature for any degree or other award.

At ...

| Signature | : |             |

|-----------|---|-------------|

| Name      | : | Tan E-Chian |

|           |   |             |

|           |   | 21/4/2022   |

| Date      | : |             |

#### ACKNOWLEDGEMENTS

Firstly, I would really like to thank my project supervisor who is also my academic advisor, Mr. Mok Kai Ming and Dr Chang Jing Jing for his constant supervision, suggestions for the project, as well as all the encouragement and life lessons he had taught me throughout the years of study. I am thankful because he had given me the opportunity to do this project which allowed me to learn many things and would be helpful for the path I am going to pursue in the future years of study or working environment.

I would also like to thank my beloved family who provided me the support and financial help I need during my years of study. Thank you for supporting me in all the good and bad times I express throughout my life and thank you for always being there whenever I need to turn to someone.

Finally, I must say thank you to my fellow course mates who throughout the years of study, been though hardships and many different obstacles and finally overcame it as the years of study is finally coming to an end. Thank you for all the generous helps and kindness.

#### ABSTRACT

The project is about the design and implementation of a direct memory access (DMA) specifically for Reduced Instruction Set Computer (RISC-32) processor. In this proposal, a short introduction about the knowledge needed to get the project going is stated at the beginning. Followed by the literature review which talks about previous research done by other researchers.

A short explanation about DMA is introduced and how everything is to be implemented into the RISC32 microprocessor. A block diagram will show what is inside the DMA controller. A partitioning level diagram is drawn to make users understand what is inside the DMA Controller. The pin description of the DMA is drawn out.

Lastly, challenges encountered in this project is written and come the conclusion to state what has been done in this overall project together with the progress timeline made during the weeks.

# TABLE OF CONTENTS

| TITLE PAGE i                                                              |

|---------------------------------------------------------------------------|

| <b>DECLARATION OF ORIGINALITY</b> Error! Bookmark not defined.            |

| ACKNOWLEDGEMENTSv                                                         |

| ABSTRACT vi                                                               |

| TABLE OF CONTENTSvii                                                      |

| LIST OF TABLESxii                                                         |

| List of figures xiii                                                      |

| LIST OF ABBREVIATIONxv                                                    |

| Chapter 1: Introduction17                                                 |

| 1.1 Background Information17                                              |

| 1.1.1 Direct Memory Access (DMA)17                                        |

| 1.1.2 MIPS                                                                |

| 1.1.3 Bus                                                                 |

| 1.2 Motivation                                                            |

| 1.3 Problem Statement                                                     |

| 1.4 Project Scope21                                                       |

| 1.5 Project Objectives                                                    |

| 1.6 Impact, Significance, and Contribution                                |

| Chapter 2: Literature Review                                              |

| 2.1: Overview of Direct memory access (designed by Ahmed, 2019)           |

| 2.1.1: Advanced Microcontroller Bus Architecture (AMBA)                   |

| 2.1.2: Pin description of DMA (designed by Ahmed, 2019)25                 |

| 2.1.3: Block diagrams of Direct memory access (designed by Ahmed, 2019)26 |

| 2.1.4: Timing Diagram of DMAC27                                           |

| Chapter 2.2: Overview of Direct memory access (designed by Jagtap, 2017)2                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2.1: Multichannel DMA controller                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2.2: Block diagrams of the DMAC2                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2.3: Datapath of proposed DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 3: Proposed Method/ Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1 Methodologies and General Work Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1.1 RTL Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1.2 Micro-architecture Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1.3 RTL Modelling and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1.4 Logic synthesis for FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2 Design Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2.1 ModelSim Student edition-x64 10.5                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2.2 Xilinx Vivado Design Suite                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2.3 PCSpim                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.3 PCSpim   3     3.4 Implementation Issues and Challenges   3                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4 Implementation Issues and Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3                                                                                                                                                                                                                                                                                                                                                           |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3         3.5.2 Gantt Chart for Project 2       3                                                                                                                                                                                                                                                                                                           |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3         3.5.2 Gantt Chart for Project 2       3         Chapter 4 System Specification                                                                                                                                                                                                                                                                    |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3         3.5.2 Gantt Chart for Project 2       3         Chapter 4 System Specification         3.4 I System Overview of Risc32 Pipeline Processor       3                                                                                                                                                                                                 |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3         3.5.2 Gantt Chart for Project 2       3         Chapter 4 System Specification         3.4 I System Overview of Risc32 Pipeline Processor       3         4.1 System Overview of Risc32 Pipeline Processor       3         4.1.1 RISC32 Pipeline Processor Architecture       3                                                                   |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3         3.5.2 Gantt Chart for Project 2       3         Chapter 4 System Specification         3.4.1 System Overview of Risc32 Pipeline Processor       3         4.1.1 RISC32 Pipeline Processor Architecture       3         4.1.2 Functionality of RISC32 Pipeline Processor       4                                                                   |

| 3.4 Implementation Issues and Challenges       3         3.5 Timeline       3         3.5.1 Gantt Chart for Project 1       3         3.5.2 Gantt Chart for Project 2       3         Chapter 4 System Specification         3.4.1 System Overview of Risc32 Pipeline Processor       3         4.1.1 RISC32 Pipeline Processor Architecture       3         4.1.2 Functionality of RISC32 Pipeline Processor       4         4.1.3 Memory Map of the RISC32 Pipeline Processor       4 |

viii

| 4.2.3 Input Output Description of the Chip Interface of the RISC32 | Pipeline Processor |

|--------------------------------------------------------------------|--------------------|

| Chapter 5: Micro-Architecture Specification                        | 45                 |

| 5.1 DMA Controller Unit                                            |                    |

| 5.1.1 Functionality/ Feature of the DMA Controller Unit            |                    |

| 5.1.2 Operating Procedure (External Operation)                     | 45                 |

| 5.1.3 Unit Interface of the DMA controller                         | 46                 |

| 5.1.4 Input Pin Description of the DMA Controller Unit             | 47                 |

| 5.1.5 Output Pin Description of the DMA Controller Unit            | 47                 |

| 5.1.6 Input Output Pin Description of the DMA Controller Unit      |                    |

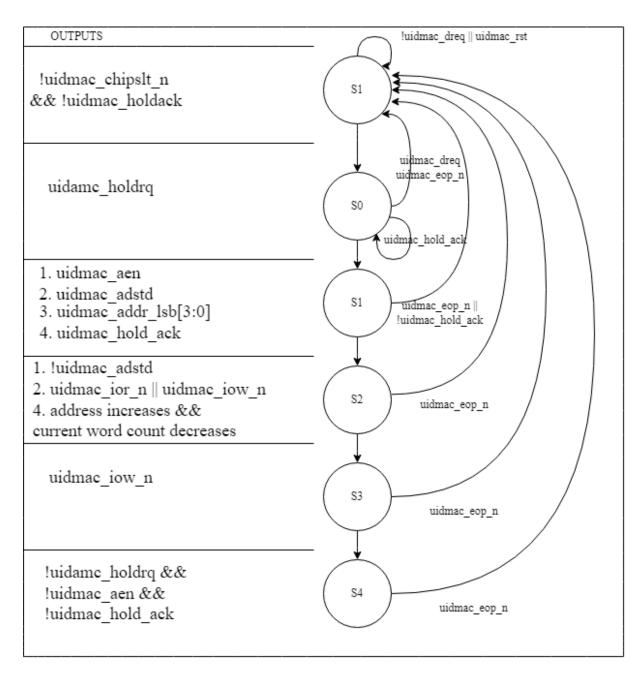

| 5.1.7 Finite State Machine of DMA controller operations            |                    |

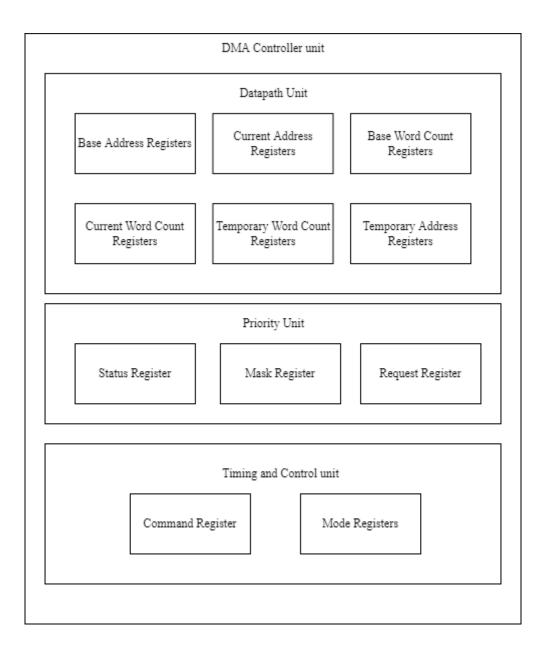

| 5.1.8 Design Partitioning of the DMA Controller unit               |                    |

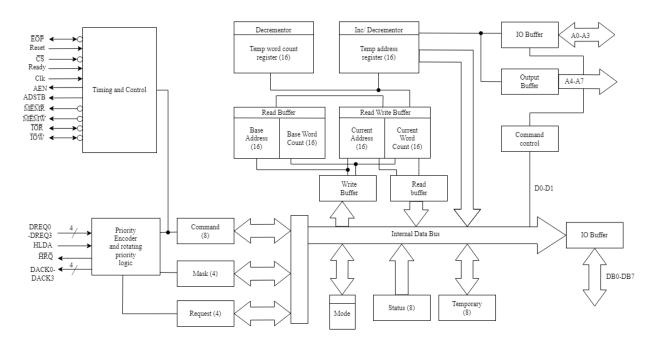

| 5.1.9 Micro-Architecture of the DMA Controller Unit (Block Level)  | )52                |

| 5.2 DMAC Datapath Unit                                             |                    |

| 5.2.1 Functionality/Feature of the Datapath Unit                   | 53                 |

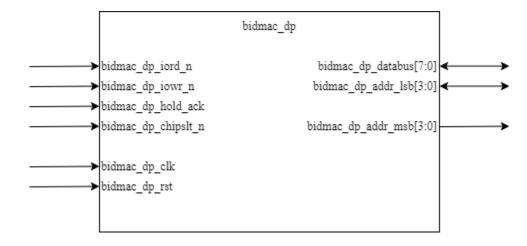

| 5.2.2 Block Interface of the DMAC Datapath Unit                    | 54                 |

| 5.2.3 Input Pin Description of the DMAC Datapath Unit              | 54                 |

| 5.2.4 Output Pin Description of the DMA Controller Unit            | 55                 |

| 5.2.5 Input Output Pin Description of the DMA Controller Unit      |                    |

| 5.3 DMAC Timing and Control Unit                                   | 55                 |

| 5.3.1 Functionality/Feature of the Timing and Control Unit         |                    |

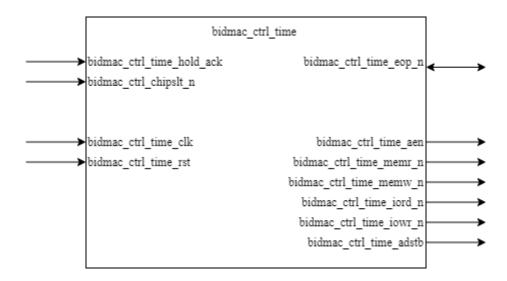

| 5.3.3 Block Interface of the DMAC Timing and Control Unit          | 57                 |

| 5.3.4 Input Pin Description of the Timing and Control Unit         |                    |

| 5.3.5 Output Pin Description of the Timing and Control Unit        |                    |

| 5.3.6 Input Output Pin Description of the Timing and Control Unit  |                    |

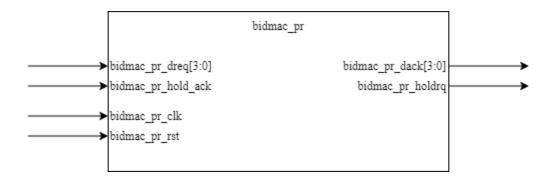

| 5.4 DMAC Priority Unit                                             |                    |

| 5.4.1 Functionality/Feature of the Priority Unit                   |                    |

ix

44

| 5.4.3 Block Interface of the DMAC Priority Unit        | 61           |

|--------------------------------------------------------|--------------|

| 5.3.4 Input Pin Description of the DMAC Priority Unit  | 61           |

| 5.3.5 Output Pin Description of the DMAC Priority Unit |              |

| CHAPTER 6: VERIFICATION SPECIFICATION AND STMULATIO    | ON RESULT 63 |

| 6.1 Test Plan for DMA Controller                       |              |

| CHAPTER 7: SYNTHESIS AND IMPLEMENTATION                | 64           |

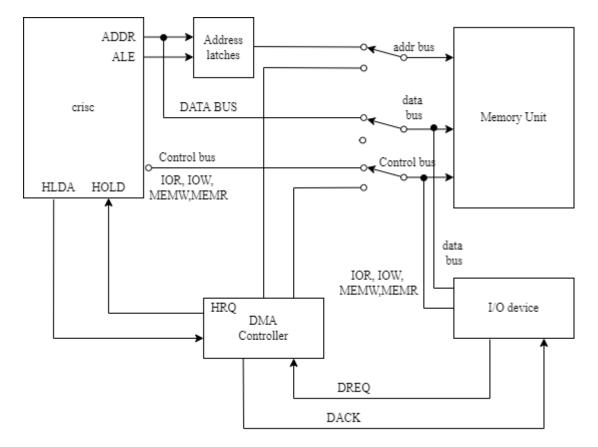

| 7.1 DMA Interface With RISC32 Processor                | 64           |

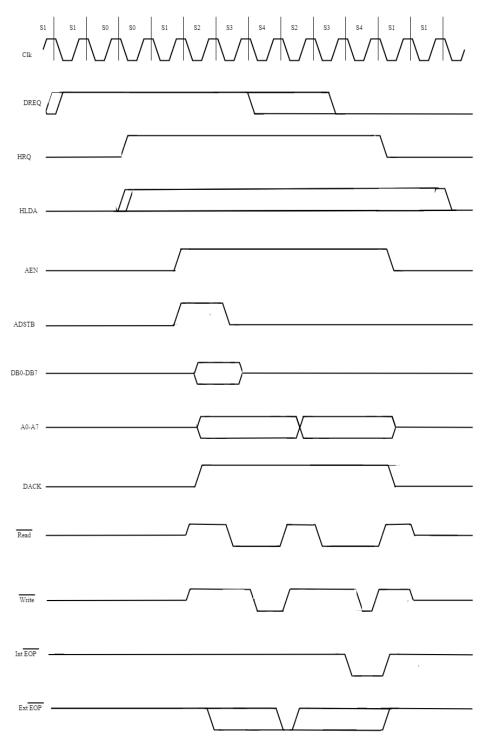

| 7.2 Timing Waveforms of the DMA Processes              |              |

| Chapter 8: Conclusion and Future Work                  | 66           |

| 8.1 Conclusion                                         |              |

| 8.2 Future Work                                        |              |

| Bibliography 67                                        |              |

| Appendix A: A                                          |              |

| A.1 RTL design module of interfaces.                   | A            |

| A.2 DMA Timing and Control module interface            | D            |

| A.3 Interface for DMA Registers                        | F            |

| APPENDIX B: Bi-weekly Reports                          | a            |

| B.1: Bi-weekly Week 2                                  | a            |

| B.1: Bi-weekly Week 4                                  | b            |

| B.1: Bi-weekly Week 6                                  | c            |

| B.1: Bi-weekly Week 8                                  | d            |

| B.1: Bi-weekly Week 10                                 | e            |

| B.1: Bi-weekly Week 12                                 | f            |

| B.1: Bi-weekly Week 14                                 | g            |

| Poster H                                               |              |

| н                                                      |              |

Bachelor of Information Technology (Honours) Computer Engineering Faculty of Information and Communication Technology (Kampar Campus), UTAR

# LIST OF TABLES

| Table                                                                  | Page |

|------------------------------------------------------------------------|------|

| Table 2.1.2.1: AHB side signals                                        | 9-10 |

| Table 2.1.2.1: APB side signals                                        | 10   |

| Table 3.2.1.: Comparison among Verilog Simulators                      | 19   |

| Table 3.5.1.1: Gantt chart for Project 1                               | 21   |

| Table 3.3.1.2: Gantt chart for Project 2                               | 21   |

| Table 4.1.1.1: Specification of the RISC32 pipeline                    | 24   |

| Table 4.1.3.1: Memory map description of the RISC32 pipeline processor | 26   |

| Table 5.1.8.1: Functionality of DMA controller unit's components       | 35   |

| Table 5.1.8.2: Internal registers of the DMA controller                | 36   |

| Table 5.2.1.1: Internal registers of DMAC Datapath                     | 38   |

| Table 5.3.1.1: Internal registers of DMAC Timing and Control Unit      | 39   |

| Table 5.3.1.2: Command and Register Codes                              | 40   |

| Table 5.4.1.1: Internal registers of DMAC Priority Unit                | 43   |

# List of figures

| Figure                                                                                                                                         | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1.1.1: Simple representation of Direct Memory Access                                                                                  | 1    |

| Figure 1.1.2.1: Conventional pipeline execution                                                                                                | 2    |

| Figure 1.1.3.1: Illustration of three types of buses in a computer                                                                             | 3    |

| Figure 2.1.1.1: Typical AMBA-based system                                                                                                      | 8    |

| Figure 2.1.3.1 Multiple masters connected to slave                                                                                             | 11   |

| Figure 2.1.3.2 DMA in computer architecture                                                                                                    | 11   |

| Figure 2.1.4.1: Timing diagram of read operation                                                                                               | 12   |

| Figure 2.2.1.1: Block Diagram of DMA                                                                                                           | 13   |

| Figure 2.2.3.1: Datapath of DMAC                                                                                                               | 14   |

| Figure 3.1.1.1: RTL design flow used to design DMAC                                                                                            | 16   |

| Figure 4.1.1.1: An overview on the architecture of the                                                                                         | 23   |

| RISC32 pipeline processor                                                                                                                      |      |

| Figure 4.1.2.1: functionality of MIPS architecture                                                                                             | 25   |

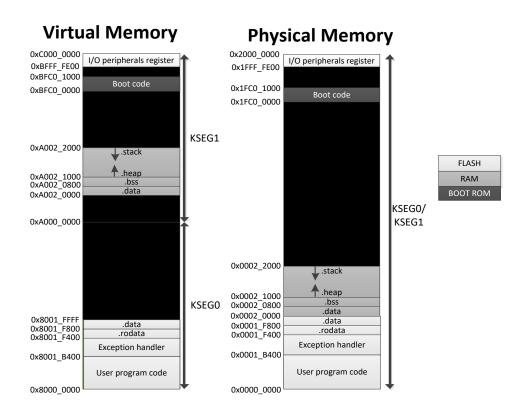

| Figure 4.1.3.1: Memory map of the RISC32 pipeline processor.                                                                                   | 26   |

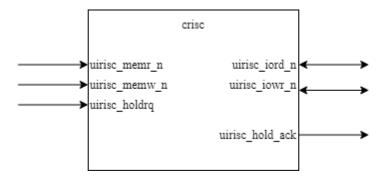

| Figure 4.2.1: Chip interface of the RISC32 pipeline processor needed for DMA                                                                   | C 27 |

| Figure 5.1.3.1: DMA controller unit interface.                                                                                                 | 30   |

| Figure 5.1.7.1 Finite state machine of DMA controller unit                                                                                     | 33   |

| Figure 5.1.8.1: Block-level partitioning of the DMA controller unit                                                                            | 35   |

| Bachelor of Information Technology (Honours) Computer Engineering<br>Faculty of Information and Communication Technology (Kampar Campus), UTAR |      |

xiii

| Table 5.1.9.1: Simplified Micro-architecture of the DMA controller unit | 36 |

|-------------------------------------------------------------------------|----|

| Figure 5.2.2.1: Block interface of the DMAC Datapath Unit.              | 38 |

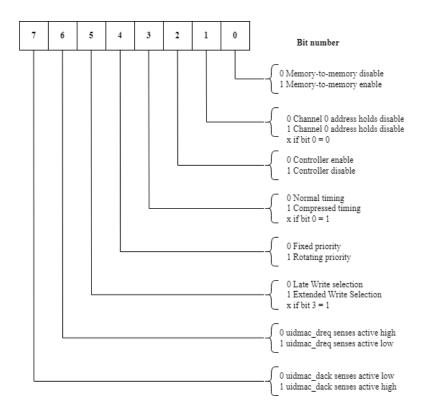

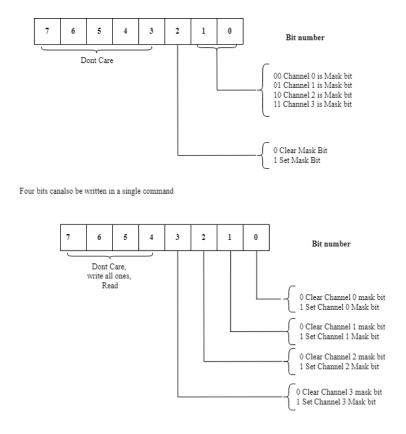

| Figure 5.3.1.1: Addresses and Description of each Pin                   | 40 |

| Number for Command Register                                             |    |

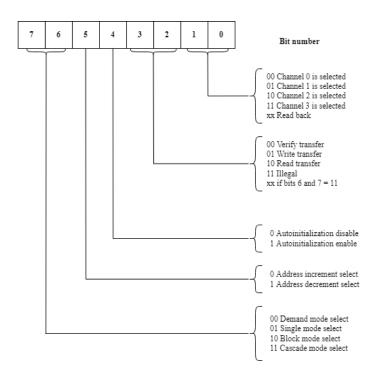

| Figure 5.3.1.2: Addresses and Description of each Pin                   | 41 |

| Number for Mode Register                                                |    |

| Figure 5.3.3.1: Block Interface of the DMA Timing and Control Unit.     | 41 |

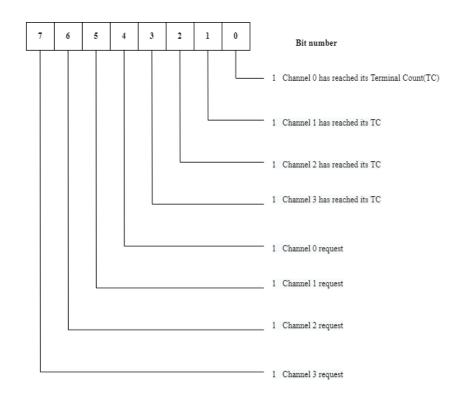

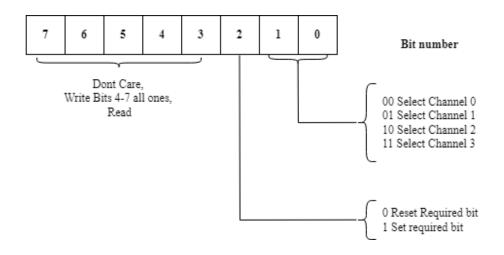

| Figure 5.4.1.1: Addresses and Description of each Pin                   | 44 |

| Number for Status Register                                              |    |

| Figure 5.4.1.2: Addresses and Description of each Pin                   | 44 |

| Number for Mask Register                                                |    |

| Figure 5.4.1.3: Addresses and Description of each Pin                   | 45 |

| Number for Request Register                                             |    |

| Figure 5.4.3.1: Block Interface of the DMAC Priority Unit               | 45 |

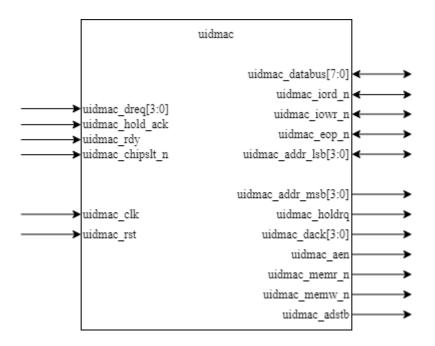

| Figure 7.1.1: DMA Interface With RISC32 Processor                       | 48 |

| Figure 7.2.1: Timing Waveforms of the DMA Processes                     | 49 |

# LIST OF ABBREVIATION

| AMBA | Advanced Microcontroller Bus architecture           |

|------|-----------------------------------------------------|

| DMA  | Direct Memory Access                                |

| CPU  | Central Processing Unit                             |

| RAM  | Random Access Memory                                |

| MIPS | Microprocessor without Interlocked Pipelined Stages |

| I/O  | Input/ Output                                       |

| VHDL | Verilog Hardware Description Language               |

| RISC | Reduced-Instruction-Instruction-set Computing       |

| IP   | integrated property                                 |

| IC   | Integrated circuit                                  |

| ISA  | Instruction set architecture                        |

| USB  | Universal Serial Bus                                |

| ISR  | Interrupt Service Routine                           |

| AHB  | Advanced High-performance Bus                       |

| APB  | Advanced Peripheral Bus                             |

| ASB  | Advanced System Bus                                 |

| DDR  | Double Data Rate                                    |

| AXI  | Advanced eXtensible Interface                       |

| ROM  | Read-only Memory              |  |  |

|------|-------------------------------|--|--|

| FSM  | Finite-state machine          |  |  |

| FPGA | Field Programmable Gate Array |  |  |

| RTL  | Register Transfer Level       |  |  |

| FIFO | First in First out            |  |  |

| IF   | Instruction Fetch             |  |  |

| ID   | Instruction Decode            |  |  |

| WB   | Write Back                    |  |  |

| EX   | Execute                       |  |  |

| MEM  | Memory                        |  |  |

## **Chapter 1: Introduction**

## **1.1 Background Information**

An overview of a must-knows that help identify and understand some facts or knowledge about this current project.

# 1.1.1 Direct Memory Access (DMA)

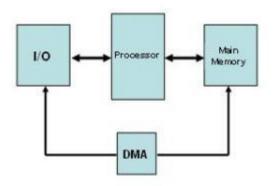

DMA is a method used to transferring data from the computer's RAM to another part of the computer without passing into the CPU. By doing this it can help save processing time and is a great and efficient way to move data from the computer's memory to other parts of the computer.

Figure 1.1.1.1: Simple representation of Direct Memory Access

#### 1.1.2 MIPS

MIPS in non-abbreviated form is Microprocessor without Interlocked Pipeline Stages. MIPS is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by MIPS Technologies USA 1995 the in the (Charles, https://en.wikipedia.org/wiki/MIPS\_architecture#cite\_note-Price1995-2 ). RISC is designed to do a simpler instruction sets with only a few addressing modes as opposed to the Complex Instruction Set Computer (CISC) which has a much more complex sets of instruction. This results in hardware being able to provide much more efficient work as it is less complex, easier and faster for users to build and test. All this of course comes with a price, sacrificing complexity results in an increase of instructions used per program per clock cycle. To avoid this, the instruction is run overlappingly in a pipeline manner as shown in Figure 1.1.1.1. Over the years, the technologies have been improved ever since it is first developed. It can now support 64- bit addressing and operation with high precision and succeeded in making its way into video game consoles, routers etc.

| Instr. No.     | Pipeline Stage |    |    |     |     |     |     |

|----------------|----------------|----|----|-----|-----|-----|-----|

| 1              | IF             | ID | ΕX | MEM | WB  |     |     |

| 2              |                | IF | ID | EX  | мем | WB  |     |

| 3              |                |    | IF | ID  | ΕX  | мем | WB  |

| 4              |                |    |    | IF  | ID  | ΕX  | мем |

| 5              |                |    |    |     | IF  | ID  | ΕX  |

| Clock<br>Cycle | 1              | 2  | 3  | 4   | 5   | 6   | 7   |

Figure 1.1.2.1: Conventional pipeline execution

#### 1.1.3 Bus

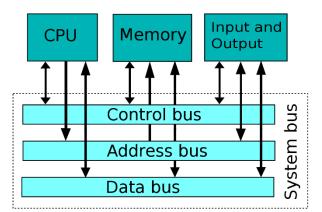

In a computer subsystem, bus allows the transfer of data between one component to another within the same system mother board or even between two different sets of computers. Transferring data to and from memory or the Central Processing Unit (CPU) and in this case, direct memory access (DMA) is one of the many ways a bus in a computer system can be used. In most case, there are three types of buses that can carry information around the system. These include:

- The address bus which carries memory addresses from the processor to input/ output devices (I/O). this bus is considered unidirectional

- The data bus which carries data between the processor and the I/O. This bus is considered bidirectional.

- The control bus that carries control signals to and from I/O. they can also carry clock signal. This bus is considered bidirectional.

Figure 1.1.3.1: Illustration of three types of buses in a computer

## **1.2 Motivation**

A 32-bit RISC pipeline microprocessor has been developed in the Faculty of Information and Communication Technology (FICT) of Universiti Tunku Abdul Rahman (UTAR) by using Verilog Hardware Description Language (HDL). This project is based on the Reduced Instruction Set Computing (RISC) architecture. The motivations for initiating this project are as follows:

- Microchip design companies have come up with microprocessor designs as Intellectual Property (IP) and is only used for commercial purposes. Microprocessors IP involves the information on a complete design for both front-end (modeling and verification) and the back-end (physical design) of an integrated circuit (IC). These IPs are kept confidential because it usually costs huge sums of money to get the designs.

- There are quite a few microprocessor cores designs that can be found on the internet at OpenCores (<u>http://www.opencores.org/</u>). However, those designs do not utilize the entire MIPS Instruction Set Architecture (ISA), therefore cannot be reused and customized

- In addition to the reason above, these free designs are most of the time complete and underdeveloped as compared to the paid ones. Due to this reason, there isn't any comprehensive verification specification making the verification of a RISC microprocessor slower. This is bad because it will slow the whole design process down significantly.

- When the front-end design is done badly, the physical design would be affected as well and need to be repeatedly changed. This is all due to the poorly design verification specifications for these microprocessor cores.

UTAR has already came up with solutions for the problems mentioned above by creating a 32bit RISC core-based environment for research as well as specific hardware modelling purpose. The RISC32 project that was initiated in UTAR has completed the CPU designs that supports basic instructions similar to MIPS instructions. The system control coprocessor that is the Coprocessor 0 (CP0) is also available to interface with I/O devices and handle interrupts. Because of this reason, a DMAC can be developed making data transfers more efficient. Clearly, there isn't many free designs about DMAC available in the internet and even if there is one available, it is either not very detailed due to the advancement of the technologies for a DMA and not comprehensive enough or the data isn't completed for us to build a design.

#### **1.3 Problem Statement**

As mentioned above, Direct Memory Access (DMA) is method used for sending and fetching data directly from the input/ outputs to and from the main memory, bypassing the Central Processing Unit (CPU). Without this method, the speed of memory processing in CPU is greatly reduced. In the current generation, it is almost impossible for a CPU to run without the DMA.

CPU will be fully occupied during the process of using a programmed input/ output for the entire read or write operation, making it unavailable to perform other work. Simple task such as transferring files from a USB drive to the computer would be such a hassle. This problem is not only important to tech companies like Huawei, Microsoft, etc, it is also as equally important to anyone that is doing their task on a computer or a laptop. Users would not be able to experience the convenience and speed of the modern world technology as the option to multitask is taken out of the picture. It is crucial for computer engineers as well. Computer engineers spend huge amount of time in simulation which requires a huge workload from CPUs. When DMA is out of the picture, it can be hard for the engineers to complete their work on time which can be very costly in terms failing to fulfil the contract in a required time.

#### **1.4 Project Scope**

The project scope will mainly focus on designing and integrating the DMA controller into the existing RISC32 pipeline processor. The specification of the DMAC unit and its internal block will be functionally verified by developing testbenches.

In addition, an Interrupt Service Routine (ISR) for handling all the interrupt requests generated by the DMA controller will be developed and then integrated into the existing exception handler of the RISC32 pipeline processor. Some MIPS test programs will also be written to test the DMA controller's functions after integration as well as to verify the correctness of the ISR execution.

Lastly, a detailed documentation on this project will be developed and maintained. This will be a project that includes a software, simulation result and concept design are expected to be delivered at the end of the project.

#### **1.5 Project Objectives**

The objectives of this project are:

- To develop a DMA controller. This involves the micro-architecture modelling and verification of the DMA controller using Verilog language.

- To integrate the DMA controller into the RISC32. This involves the development of the interface between the DMA controller and the RISC32 based on I/O memory mapping technique. An Interrupt Service Routine specifically for the DMA controller will be developed in MIPS assembly language and integrated into the exception handler

#### 1.6 Impact, Significance, and Contribution

After the completion of this project, it can provide a complete RISC microprocessor core-based development environment. The development of this will result in the following:

- A well-developed design and documentation of the chip specification, the top-down architecture specification and the micro-architecture specification

- A fully functional well-developed DMAC that controls the in and out data flow of the system written in Verilog HDL

• A well-developed verification specification of the DMA controller unit. This verification specification contains suitable verification methodology, verification techniques, test plan, testbench architecture etc.

This project would help to come up with an environment that is mentioned above by providing support to hardware modelling research work. Once the project is implemented into the RISC32 MIPS environment, it can significantly increase research speeds of future research work due to the functionality of the DMA controller. Future users can also easily identify its function since a detailed paperwork is being shown here in this project so there won't be any confusions.

# **Chapter 2: Literature Review**

#### 2.1: Overview of Direct memory access (designed by Ahmed, 2019)

#### 2.1.1: Advanced Microcontroller Bus Architecture (AMBA)

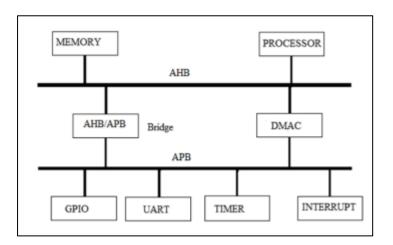

Despite this design of DMA controller working on Advanced Microcontroller Bus architecture (AMBA) specifications instead of RISC32 MIPS environment, it can be used as an example of DMA controller designs as this is one of the few designs available on the internet for free. The AMBA specification mainly focuses these two buses: Advanced High-performance Bus and the Advanced peripheral Bus. The DMA controller design works as a bridge between these two buses and allow them to work hand in hand. It provides the options of choosing between buffer or non-buffer data transfer mode according to the peripheral speed. The operation is done synchronized by an asynchronous FIFO.

Figure 2.1.1.1: Tvpical AMBA-based system

• Advanced High-performance Bus (AHB)

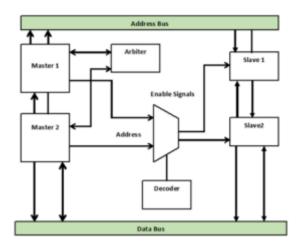

This bus is able to maintain a maximum of 128-bits transfer. It is also able to support several bus masters. The AHB normally contain the AHB slave, AHB master, the control unit (arbitrary), and decoder. In a conventional AMBA design, there will normally be many masters and slaves. The Control unit would give out signals to select one master at a time. This bus I usually at the processor's side.

• Advanced System Bus (ASB)

This is a high performing bus. It will be synchronous once being connected to the control unit from multiple masters allowing them to be accessed in one control unit. This bus implements the pipeline so data and addresses can be transferred concurrently. This is also usually at the processor's side.

• Advanced Peripheral Bus (APB)

This is a low performing bus which is designed just to connect the peripherals on the System on chip (SoCs). This bus s the AHB master to address one of the slaves of APB system when the APB and AHB is connected. This bus only connects the master and slave together so it is placed on the peripheral side.

| Name   | Bit size | Description                                             |

|--------|----------|---------------------------------------------------------|

| CLK    | 1        | Clock signal                                            |

| RESET  | 1        | Active low reset                                        |

| BUSREQ | 1        | Used to request for bus permission                      |

| GRANT  | 1        | Feedback from master that access has been granted       |

| ADDR   | 32       | 32-bit address bus                                      |

| TRANS  | 2        | Transfer type: idle, busy, sequential or non-sequential |

| WRITE  | 1        | High to write/ low to read                              |

| SIZE   | 3        | Size of transfer: byte, half word or word               |

| BURST  | 3        | Transfer form indication                                |

| PROT   | 4        | Indicates transfer type, opcode fetch or data access    |

# 2.1.2: Pin description of DMA (designed by Ahmed, 2019)

Bachelor of Information Technology (Honours) Computer Engineering Faculty of Information and Communication Technology (Kampar Campus), UTAR

| WDATA | 32 | Write pins, data transfer from master to slave |

|-------|----|------------------------------------------------|

| RDATA | 32 | Read pins, data transfer from slave to master  |

| READY | 1  | High to indicate transfer completion           |

| RESP  | 1  | Feedback status: error, okay, retry or split   |

| SEL   | 1  | Slave selected                                 |

#### Table 2.1.2.1: AHB side signals

| Name   | Bit size | Description                                                         |

|--------|----------|---------------------------------------------------------------------|

| CLK    | 1        | Clock signal                                                        |

| RESET  | 1        | Active low reset                                                    |

| SEL    | 16       | Able to tell which slave is selected and what type of data transfer |

| ENABLE | 1        | Enable Signal                                                       |

| WRITE  | 1        | High to write/ low to read                                          |

| WDATA  | 32       | Write pins, data transfer from master to slave                      |

| RDATA  | 32       | Read pins, data transfer from slave to master                       |

| READY  | 1        | High to indicate transfer completion                                |

#### Table 2.1.2.1: APB side signals

# 2.1.3: Block diagrams of Direct memory access (designed by Ahmed, 2019)

Figure 2.1.3.1 Multiple masters connected to slave

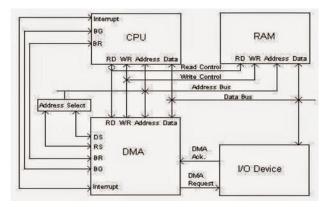

Figure 9129 DMA in computer architecture

# 2.1.4: Timing Diagram of DMAC

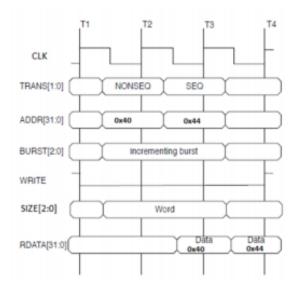

To build this AMBA design and implement it so that it works the way it is intended to, the Verilog hardware descriptive language (HDL) is used. The read operations will be activated once the bus has granted access.

Figure 2.1.4.1: Timing diagram of read operation

# Chapter 2.2: Overview of Direct memory access (designed by Jagtap, 2017)2.2.1: Multichannel DMA controller

Unlike the previous design, this design is implemented into ISA expansion bus. The traditional 4-bit DMA channel is increased to a 16-bit DMAC.

For each channel, two lines are needed in order to function: One of the line request access of buses from the processor and the second one is to prevent data transfer from being disrupted from the processor. For this very purpose, the bus must be used by the DMAC when the processor does not require it or by cycle stealing.

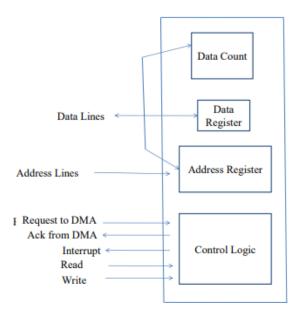

#### 2.2.2: Block diagrams of the DMAC

Figure 2.2.1.1: Block Diagram of DMA

The overall functionality is quite the same compared to the previous design. A series of command will be sent from the processor when a huge amount of data is needed to be transferred. The buses will be taken over by the DMA once the procedure has started and can only be stopped once an acknowledge signal is sent from the DMA to the processor that signifies the completion of the process. This is done when the interrupt signal is sent form the DMA.

In this current design, efficient communication is the main focus between the memory and processor with different commands from the control unit which provides more flexibility and versatility to the design. An additional FIFO is added into this design to make up for the

complexity and the less versatile design of the older versions of DMAC. More channels are added to increase the configurability.

With this the DMAC is implemented in the computer architecture and is shown in the figure below. As mentioned above, an interrupt will occur once it senses any data that is going to be transferred from the processor or the memory or vice versa. It stops its current task at hand so that it is able to grant permission to the DMAC to control all the buses once all the requirements are met: handshake, acknowledgment, opcode data, etc. after all this is done, the DMA will check the descriptor for any information related to different DMA channels. Control unit will be able to perform read/ write operation for different DMA channels.

# 2.2.3: Datapath of proposed DMA

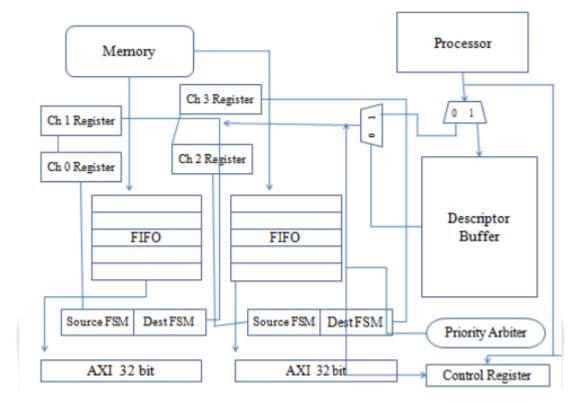

Figure 2.2.3.1: Datapath of DMAC

This design consists of 4 channels, arbiter module, channel registers, 3 AXI masters, one AXI slave, Asynchronous FIFO buffers. Again, the DMAC consists of 4 channel and each performs a specific data transmission type for example channel one is asked to transfer a series of data which might be addresses and channel two for normal data transfer, then they will do what that has been told and not be overlapped causing confusion on the receiving end. Although there are four AXI masters mentioned but there is only one that is associated with the AXI protocol. The two remaining AXI masters can be connected to the external memory or the Double Data Rate (DDR).

There are two modes that this DMA controller can run on: the first one is the data transfer mode and second one being the descriptor transfer mode. The first one is when the DMA controller transfer huge load of data and after that a second priority channel is selected. Whereas in the second mode, tasks are being sent to the channel descriptor by the processor ahead pf schedule. After this had happened, the arbitration scheme would select the highest priority channel which means that the transfer that happen first (data transfer) in the data descriptor will load the work registers and execution of related data transfer would be started. This is how data is being transferred in the DMA Controller without the interference and involvement of the processor.

#### **Chapter 3: Proposed Method/ Approach**

#### 3.1 Methodologies and General Work Procedures

For this project's design process' digital system, there will be 3 types of design methodologies being used: firstly, it is the top-down design methodology followed by the bottom-up design methodology and finally the mixed design methodology. The top-down design methodology will be used for designing and developing the DMA controller unit. Next, the top-down design methodology, the top level-representation of a unit is first specified, lastly, lower-level representations based on different important cases such as speed, power consumption, silicon area and functionality.

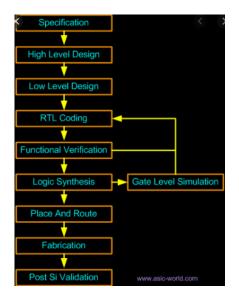

#### **3.1.1 RTL Design Flow**

Register-transfer level (RTL) is a design summary used to represent a synchronous digital circuit in terms of digital signal flow between hardware registers, logical operations, etc, performed on those signals. In RTL design flow, the micro-architectural level design will be used for the main frame of the design because the DMA controller will be designed in unit-level. Using this design flow, a better representation of project progress and accuracy will be achieved.

Figure 3.1.1.1: RTL design flow used to design DMAC

Bachelor of Information Technology (Honours) Computer Engineering Faculty of Information and Communication Technology (Kampar Campus), UTAR

## 3.1.2 Micro-architecture Specification

This part of the project will give a detailed description of the internal design of the DMA controller. The internal design of the DMA controller will give be described in detail and also design-specific technical information will be provided for the design to be as accurate as possible. In this project, the unit level of the DMA controller will include the following information:

- Functionality and the feature description

- Interfaces and I/O pin description

- Functional partitioning into blocks and inter-blocks signalling

- Additional blocks would be separated once a specific block is too complexed and would be divided into a combination of smaller blocks

- Test plan (functional test)

For the block level design of the DMA controller, this following description would be provided:

- Functionality and the feature description

- Interfaces and I/O pin description

- Internal operation: Finite-state machine (FSM), and etc,

- Schematic and block diagram

- Test plan ((Functional test)

# 3.1.3 RTL Modelling and Verification

After the micro-architecture specification has been came up with, the RTL coding of the DMA controller can begin. The RTL models will then be verified for functional correctness at each level after the coding has finished. Going deeper into the picture, each block of RTL model is

to be verified before they are integrated into unit level. In the development process of the project, the design does not meet the requirement of the DMA controller, the design flow would need to be repeated until everything is done right. After all the requirements are fulfilled, then this design would be brought over to FPGA technology to be implemented.

#### 3.1.4 Logic synthesis for FPGA

After the DMA controller unit has been fully verified with its functionality, the model would be ready for logic synthesis where RTL code is to be translated into gate level representation. Based on the result, the gate level unit would need to be verified again with its functional correctness. The design is ready for the next phase, which the physical design phase when all the design has been fully verified with the appropriate logic. On the other hand, if it does not meet with the requirement then depending on the severity, would need to be repeated just like the previous step until it is all error free.

#### **3.2 Design Tools**

For each of the step mentioned above, from building the design to physical model would require both software and hardware tools. Because of all these procedures, there exists the Electronic Design Automation (EDA) tools for designing at abstraction level. Since the model for this current DMA controller design uses Verilog hardware description language (HDL), thus a Verilog simulator has to be used to emulate Verilog HDL. Here are some examples of Verilog simulators and comparison among themselves:

| Simulator | Modelsim | VCS                              | CVC |

|-----------|----------|----------------------------------|-----|

| Company   | Graphics | SYNOPSYS*<br>Predictable Success |     |

Bachelor of Information Technology (Honours) Computer Engineering Faculty of Information and Communication Technology (Kampar Campus), UTAR

| Supported                | • VHDL-2002                       | • VHDL-2002 | V2001     |

|--------------------------|-----------------------------------|-------------|-----------|

| language                 | • V2001                           | • V2001     |           |

|                          | • SV2005                          | • SV2005    |           |

| Platform<br>availability | •Windows<br>XP/Vista/7<br>• Linux | Linux       | • Windows |

| Free                     | Yes                               | No          | Yes       |

Table 3.2.1.: Comparison among Verilog Simulators

From the table above, it is quite apparent that Modelsim is the best choice among the three since in terms of available language supported and price. A free student edition license is available for everyone on the internet. It is also true that VCS offer more range of functionality and versatility but Modelsim is sufficient enough to support all that needs to be done for this project. Modelsim also runs on Windows platform for the majority and even runs on Linux for those who do not use a Windows operating system. We do not use VCS is also because it is too expensive (minimum \$20,250 per year subscription) and for semi-professional work such as this project is really not needed.

As for the tools used for synthesis, there are several tools that can be used for logic synthesis. These can include Vivado Design suite by Xilinx, Encounter RTL Compiler by Cadence Design System, Quartus by Altera and many more. For this project, I will be using the Xilinx Vivado Design Suite because its FPGA supported functionality and it is freely available all over the internet.

#### 3.2.1 ModelSim Student edition-x64 10.5

ModelSim from Mentor graphic is the industry-leading simulation and debugging tool for HDL-based design. Furthermore, its license can be obtained online for free. Although it only provides the free license for student version only instead of the full version, it is already sufficient enough because we do not need the full functionality of the software for this current project. We just needed the Verilog and the VHDL languages that is available in the student version of the said simulator. Furthermore, syntax errors are shown once it detects any syntax error in the compiled code. Waveform simulation play an important role in the designing procedure. Testbenches are also available together with the timing diagram for different input and output pins used for model verification.

#### 3.2.2 Xilinx Vivado Design Suite

Vivado Design Suite is a software suite designed by Xilinx. The said software is used to synthesize and analyse the HDL designs. It gives the option to synthesize, perform timing analysis, examine RTL diagrams, verify and test the design. Configuration of the device is also available which makes it easier for users to complete the tasks.

#### 3.2.3 PCSpim

PCSpim is the Window version of spim. This simulation tool loads and executes assembly language program for the MIPS RISC architecture. It also provides a simple assembler as well as a debugger and a simple set of operating services. Hence, this tool would be extremely useful in developing MIPS test program in order to verify the correctness of the interrupt Service routine (ISR).

#### **3.4 Implementation Issues and Challenges**

With just the logic analysis, the implementation of the DMA into RISC32 is do-able, with the introduction of clock signals and edge positive sensitive data, a more detailed testing needs to

be conducted. Passing signal and data safely from block with different timing requirement seemed to be quite challenging to achieve. The lack of real life example is also a major challenge encountered during this project therefore, not the most accurate result will be produced at the end.

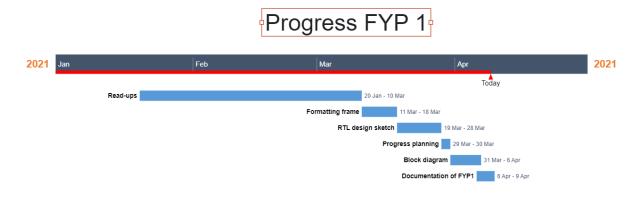

## 3.5 Timeline

## 3.5.1 Gantt Chart for Project 1

## Table 3.5.1.1: Gantt chart for Project 1

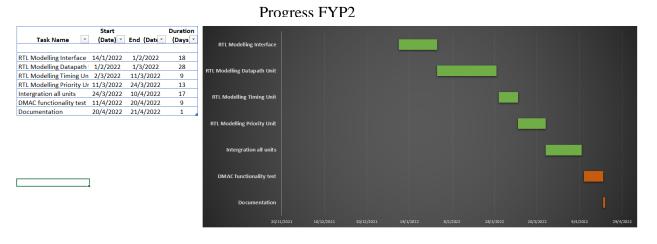

# 3.5.2 Gantt Chart for Project 2

Table 3.5.1.2: Gantt chart for Project 2

#### **Chapter 4 System Specification**

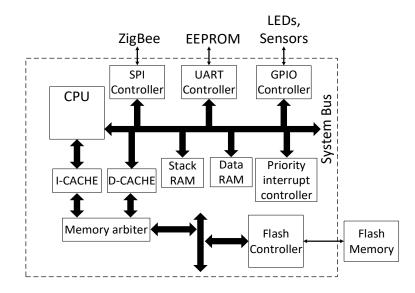

#### 4.1 System Overview of Risc32 Pipeline Processor

Since the usage of direct memory access function is not implemented inside the RISC32 pipeline processor, a DMAC would be implemented in this current project to reduce the workload of the processor during the read and write stage of the pipeline processing. The processor used in this project I developed by UTAR FICT because it provides the best software and firmware flexibility advantage for the direct memory access controller front-end design.

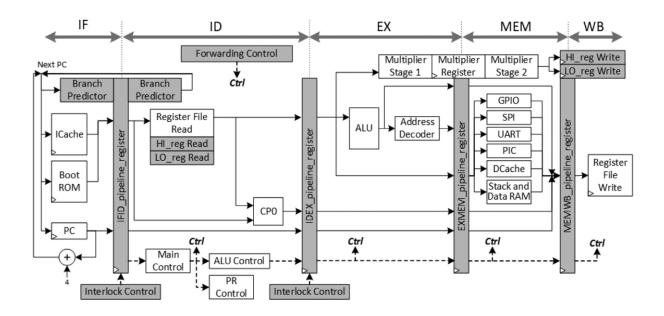

#### 4.1.1 RISC32 Pipeline Processor Architecture