# WIDE-SUPPLY INTEGRATION CMOS DC-DC CONVERTER FOR ENERGY HARVESTING APPLICATIONS

## NUR ALLISA SABRINA BINTI AMIN

# FACULTY OF ENGINEERING AND GREEN TECHNOLOGY UNIVERSITI TUNKU ABDUL RAHMAN

UNIVERSITI TUNKU ABDUL RAHMAN

AUGUST 2023

### **APPROVAL FOR SUBMISSION**

I certify that this project report entitled **WIDE- SUPPLY INTEGRATION CMOS DC-DC CONVERTER FOR ENRGY HARVESTING APPLICATIONS** was prepared by **NUR ALLISA SABRINA BINTI AMIN** has met the required standard for submission in partial fulfilment of the requirements for the award of Master Of Engineering (Electronic Systems at Universiti Tunku Abdul Rahman.

Approved by,

Signature

Supervisor

: Dr. Gabriel Chong Sing Leung

Date

: <u>16 August 2023</u>

## FACULTY OF ENGINEERING AND GREEN TECHNOLOGY UNIVERSITI TUNKU ABDUL RAHMAN

### UNIVERSITI TUNKU ABDUL RAHMAN

Date: 16 August 2023

#### SUBMISSION OF THESIS

I hereby certified that <u>Nur Allisa Sabrina Binti Amin</u> (ID No: <u>21AGM06715</u>) has completed this thesis entitled <u>"WIDE- SUPPLY INTEGRATION CMOS DC-DC CONVERTER FOR ENRGY HARVESTING APPLICATIONS"</u> under supervision of <u>DR. Gabriel Chong Sing Leung</u> from the <u>Department of Electronic</u> <u>Engineering</u>, Faculty of <u>Engineering</u> and <u>Green Technology Universiti Tunku</u> <u>Abdul Rahman.</u>

I understand that the University will upload soft copy of my thesis in pdf format into UTAR Institutional Repository, which may be made accessible to UTAR community and public.

Your Truly,

(Nur Allisa Sabrina Binti Amin)

## DECLARATION

I hereby declare that this project report is based on my original work except for citations and quotations which have been duly acknowledges. I also declared that it has not been previously and concurrently submitted for any other master or award at UTAR or other institutions.

|           | hip                             |  |  |  |  |  |  |  |

|-----------|---------------------------------|--|--|--|--|--|--|--|

| Signature |                                 |  |  |  |  |  |  |  |

| Name      | : NUR ALLISA SABRINA BINTI AMIN |  |  |  |  |  |  |  |

| No.       | : 21AGM06715                    |  |  |  |  |  |  |  |

| Date      | : 16 AUGUST 2023                |  |  |  |  |  |  |  |

## WIDE-SUPPLY INTEGRATION CMOS DC-DC CONVERTER FOR ENERGY HARVESTING APPLICATIONS

By

## NUR ALLSIA SABRINA BINTI AMIN

A Thesis Submitted To Faculty Of Engineering And Green Technology, Universiti Tunku Abdul Rahman, in partial fulfillment of the requirements for the degree of Master of Engineering (Electronic Systems)

August 2023

The copyright of this report belongs to the author under the terms of the copyright Act 1987 as qualified by Intellectual Property Policy of Universiti Tunku Abdul Rahman. Due acknowledgement shall always be made of the use of any material contained in, or derived from, this report.

© 2023, Nur Allisa Sabrina Binti Amin. All right reserved.

#### ABSTRACT

## WIDE-SUPPLY INTEGRATION CMOS DC-DC CONVERTER FOR ENERGY HARSVESTING APPLICATIONS

#### Nur Allisa Sabrina

This study describes the design, analysis, and simulation of a Wide-Supply Integrated CMOS DC-DC Converter in the goal of creating energy-efficient technology for energy harvesting applications. Cross couple charge pump is utilized in this design to to meet the special requirements of energy harvesting systems by effectively capturing and converting captured energy into suitable voltage levels. Furthermore, this paper proposed DC-DC converter that improve the existence charge pump like Dickson Charge Pump (DCP) by adding Pulse Frequency Modulation (PFM) to enhance the performance and generate a high voltage output with a variety of supply voltages. By accomplishing its goals, this study advances energy-efficient technologies and has great potential for integrated circuit systems and a variety of energy harvesting projects.

#### ACKNOWLEDGMENT

I would like to express my deepest gratitude and appreciation to the following individuals and organizations for their unwavering support and assistance throughout the completion of this thesis. First and foremost, I would like to express my deepest gratitude ans appreciation to my supervisor, Dr. Gabriel Chong , whose guidance, expertise, and constant encouragement have been instrumental in shaping this thesis. Your insightful feedback and constructive criticism have truly elevated the quality of my work.

I am also thankful to the faculty members of the Faculty of Engineering and Green Technology for their valuable insights and for creating an intellectually stimulating environment that nurtured my academic growth.

I would like to acknowledge the assistance and support I received from my friends and peers, who provided both academic and moral support. Your discussions, debates, and shared resources greatly enriched my research.

Furthermore, a special thanks to the panel of my final year project Dr. Yeap Kim Ho and moderator Prof. Humaira Nisar. Your thorough review and constructive comments greatly enriched my thesis, pushing me to delve deeper and strive for excellence. Your valuable insights have undoubtedly contributed to the refinement of this work.

### TABLE OF CONTENTS

| LIST OF TABLES                         | v  |

|----------------------------------------|----|

| LIST OF FIGURES                        | vi |

| LIST OF ABBREVIATIONS                  | ix |

| CHAPTER 1                              |    |

| INTRODUCTION                           |    |

| 1.1 Background                         | 1  |

| CHAPTER 2                              |    |

| 2.1 Literature Review                  | 10 |

| CHAPTER 3                              |    |

| METHODOLOGY                            |    |

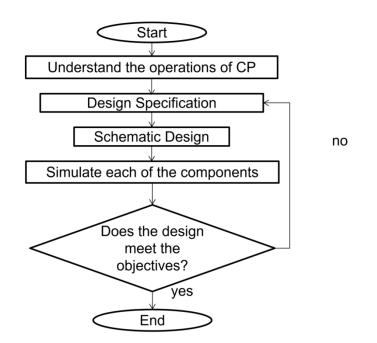

| 3.1 Flowchart                          | 32 |

| 3.2 Understand Basic Charge Pump (DCP) | 35 |

| 3.3 Proposed Design (Part I)           | 42 |

| 3.4 Results And Discussions            | 45 |

| 3.5 Proposed Design (Part II)          | 47 |

| 3.6 Result And Discussions             | 50 |

| CONCLUSION                             | 67 |

| REFERENCES                             | 68 |

### LIST OF TABLES

| Table   1 Comparison of existing papers |                                         | Page |

|-----------------------------------------|-----------------------------------------|------|

| 1                                       | Comparison of existing papers           | 24   |

| 2                                       | Parameters for Proposed Design I        | 41   |

| 3                                       | Parameters of Charge Pump without PFM   | 45   |

| 4                                       | Truth Table NAND gate                   | 56   |

| 5                                       | The parameters used in proposed design. | 65   |

| 6                                       | Parameters used for Comparator          | 65   |

### LIST OF FIGURES

## Figure

## Page

| Figure 1 . One Stage Charge Pump [1]; (a) first phase (b) second phase | 3      |

|------------------------------------------------------------------------|--------|

| Figure 2 . Clock signal, $V_{CK}$ of the Charge Pump [1]               | 4      |

| Figure 3 Dickson Charge Pump schematic design [7]                      | 10     |

| Figure 4 . Cross Coupled CTS circuit [9]                               | 11     |

| Figure 5 . Detailed Schematic of LVCP and HVCP circuit [2]             | 12     |

| Figure 6 CMOS Charge Pump in sub-2.0V operation [5]                    | 13     |

| Figure 7 . Comparison of different charge pumps. [10]                  | 14     |

| Figure 8 CP With Body Bias and Backward Control Circuit [13]           | 15     |

| Figure 9 (a)Block Diagram of RF to DC Converter (b) Cross coupled      |        |

| doubler circuit [14]                                                   | 16     |

| Figure 10 . Schematic of the proposed Charge Pump [16]                 | 17     |

| Figure 11 Proposed Design in fully integrated dual-mode charge pump [  | [18]18 |

| Figure 12 . Schematic of the Charge Pump with Clock Booster [19]       | 19     |

| Figure 13 (a) One stage of Charge Pump (b) Schematic Diagram of        |        |

| Proposed Design [20]                                                   | 20     |

| Figure 14 . Schematic the proposed Charge Pump [21]                    | 21     |

| Figure 15 . Charge Pump Method (a) Conventional. (b) Charge transfer   |        |

| switch:Type-I (c) Charge transfer switch: Type-II . (d) Two-branch     | h      |

| latch charge-pump                                                      | 22     |

| Figure 16 . Cross coupled charge pump [26]                             | 23     |

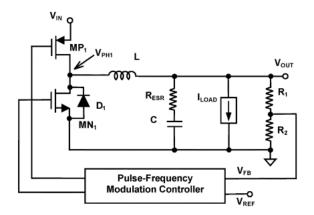

| Figure 17 | . Schematic of a synchronous buck converter with PFM contro | ol |

|-----------|-------------------------------------------------------------|----|

| [23].     |                                                             | 25 |

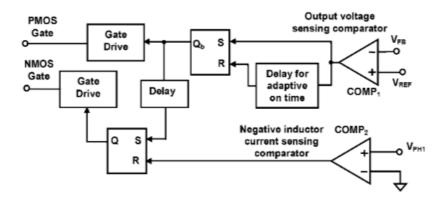

| Figure 18 | . Adaptive on-time PFM controller circuit [23]              | 26 |

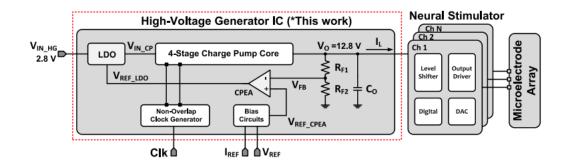

| Figure 19 | Architecture of the proposed high voltage generator IC [25] | 27 |

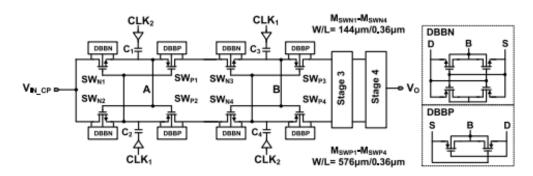

| Figure 20 | . Proposed Charge Pump [25]                                 | 27 |

| Figure 21 | LDO regulator [25]                                          | 28 |

| Figure 22 | . Charge Pump with Power Management Unit                    | 29 |

| Figure 23 | . Flow of the Charge Pump [26]                              | 30 |

| Figure 24 | Stage and Frequency Modulation [26]                         | 30 |

| Figure 25 | . Flow Chart of Wide Supply Integration CMOS DC-DC          |    |

| Conv      | erter for Energy Harvesting Applications                    | 32 |

| Figure 26 | . Dickson Charge Pump circuit                               | 35 |

| Figure 27 | . Graph for DC characteristic for Vdc from 0 to 1V          | 35 |

| Figure 28 | Vth value for M5 Transistor                                 | 36 |

| Figure 29 | : Graph for DC Characteristic (Vdc 0-3V)                    | 36 |

| Figure 30 | :Graph for DC Characteristic (Vdc 0-5V)                     | 36 |

| Figure 31 | . Graph when $R_L = 1M$ ohms                                | 37 |

| Figure 32 | . Graph for DC characteristic                               | 37 |

| Figure 33 | . Simulation result Vin =500mV                              | 38 |

| Figure 34 | Simulation result Vin=1V                                    | 39 |

| Figure 35 | . Schematic and simulation result for $Vin = 1V$            | 40 |

| Figure 36 | Simulation Result of DCP                                    | 41 |

| Figure 37 | . Block Diagram of Charge Pump without PFM                  | 42 |

| Figure 38 | . Proposed Design I                                         | 43 |

Figure 17 . Schematic of a synchronous buck converter with PFM control

| voltage                                                                  | 46   |

|--------------------------------------------------------------------------|------|

| Figure 40 . High Level of Proposed Design II                             | 47   |

| Figure 41 . The Architecture of PFM                                      | 48   |

| Figure 42 . Test Bench of Cross Couple Charge Pump                       | 50   |

| Figure 43 . Parameters of Proposed Charge Pump                           | 51   |

| Figure 44 . Simulation Result when $Vin = 550mV$                         | 52   |

| Figure 45 . Simulation Result when Vin =450m                             | 52   |

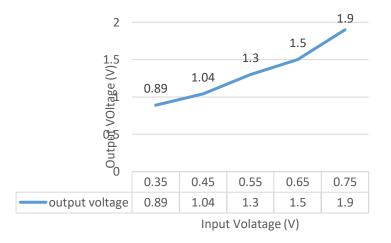

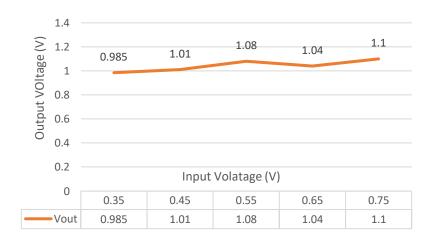

| Figure 46 Graph of Input Voltage vs Output Voltage                       | 53   |

| Figure 47 . Test Bench of PFM [26]                                       | 54   |

| Figure 48 . Test Bench of Latched Comparator [27]                        | 55   |

| Figure 49 . Simulation of Comparator and the parameters                  | 56   |

| Figure 50 . Schematic Design of NAND gate                                | 56   |

| Figure 51 . Simulation of NAD gate                                       | 57   |

| Figure 52 . Test Bench of Ring Oscillator                                | 58   |

| Figure 53 . Inverter (a) Test Bench (b) Simulation Result                | 58   |

| Figure 54 . Simulation Result of Ring Oscillator                         | 59   |

| Figure 55 . Simulation of PFM and The Parameters Used                    | 60   |

| Figure 56 . Test Bench of Proposed Design                                | 61   |

| Figure 57 . Simulation of proposed design and parameters, $Vin = 550 mV$ | V 62 |

| Figure 58 . Simulation of proposed design when $Vin = 650mV$ and $750m$  | mV62 |

| Figure 59 . Graph of Simulation For Proposed Design II                   | 63   |

| Figure 60 . Comparison of with and without PFM                           | 64   |

Figure 39 . (a) output voltage vs input voltage (b) Frequency vs input

### LIST OF ABBREVIATIONS

| SoCs            | System on Chips                                   |

|-----------------|---------------------------------------------------|

| ІоТ             | Internet-of-Things                                |

| WSNs            | Wireless Sensor Networks                          |

| EH              | Energy Harvesting                                 |

| PV              | Photovoltaic                                      |

| DC              | Direct Current                                    |

| MOSFET          | Metal-Oxide-Semiconductor Field-Effect Transistor |

| SC              | Switching Capacitor                               |

| L               | Inductor                                          |

| DCP             | Dickson Charge Pump                               |

| CP`             | Charge Pump                                       |

| LDO             | Linear Dropout                                    |

| C <sub>P</sub>  | Pumping Capacitance                               |

| C <sub>L</sub>  | Load Capacitor                                    |

| V <sub>DD</sub> | Power Supply                                      |

| IL              | Load Current                                      |

| PFM             | Pulse Frequency Modulation                        |

| NMOS            | N-type Metal-Oxide-Semiconductor                  |

| PMOS            | P-type Metal-Oxide-Semiconductor                  |

| CMOS            | Complementary Metal-Oxide-Semiconductor           |

| IC              | Integrated Circuit                                |

| РСВ             | Printed Circuit Board                             |

| CTS             | Charge Transfer Switch                            |

| LVCP                                    | Low-Voltage Charge Pump                                                                                  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------|

| HVCP                                    | High-Voltage Charge Pump                                                                                 |

| PCE                                     | Power Conversion Efficiency                                                                              |

| DBB                                     | Dynamic Body Biasing                                                                                     |

| VCE                                     | Voltage Conversion Efficiency                                                                            |

| TEG                                     | Thermaoelectric Generator                                                                                |

| mV                                      | mili Volt                                                                                                |

| u                                       | micro                                                                                                    |

| m                                       | meter/mili                                                                                               |

| pF                                      | pico Farad                                                                                               |

| MHz                                     | Mega Hertz                                                                                               |

|                                         |                                                                                                          |

| dBmW                                    | Decibels miliwatt                                                                                        |

| dBmW<br>K                               | Decibels miliwatt<br>Kilo                                                                                |

|                                         |                                                                                                          |

| K                                       | Kilo                                                                                                     |

| K<br>VBC                                | Kilo<br>Voltage Boost Converter                                                                          |

| K<br>VBC<br>SD                          | Kilo<br>Voltage Boost Converter<br>Sub-Driver                                                            |

| K<br>VBC<br>SD<br>MD                    | Kilo<br>Voltage Boost Converter<br>Sub-Driver<br>Main-Driver                                             |

| K<br>VBC<br>SD<br>MD<br>VIN             | Kilo<br>Voltage Boost Converter<br>Sub-Driver<br>Main-Driver<br>Input Supply                             |

| K<br>VBC<br>SD<br>MD<br>VIN<br>mA       | Kilo<br>Voltage Boost Converter<br>Sub-Driver<br>Main-Driver<br>Input Supply<br>mili Ampere              |

| K<br>VBC<br>SD<br>MD<br>VIN<br>mA<br>Nm | Kilo<br>Voltage Boost Converter<br>Sub-Driver<br>Main-Driver<br>Input Supply<br>mili Ampere<br>nanometer |

### **CHAPTER 1**

### **INTRODUCTION**

#### **1.0 Introduction**

As process technology progresses, portable devices become more and more popular. System on Chips (SoCs) with a smaller form factor, less energy consumption, a lower price, and lower conservation are becoming increasingly important for Internet-of-Things (IoT) systems. IoT is widely used because it can cooperate and exchange information without a lot of direct human interaction. It more closely resembles an extensive network of intelligent gadgets that can communicate with one another online. As an example, Wireless Sensor Networks (WSNs) are networks of small, self-powered gadgets called sensor nodes that collaborate to gather and send data from the environment. Due to their capacity to track and collect data from various physical, environmental, or industrial contexts, these networks have grown significantly in relevance and appeal. These sensor nodes are often employed in a variety of settings, including industrial automation, healthcare, and environmental monitoring. On the other hand, most of WSNs available today still rely on batteries to supply the required power for their functioning [1]. In addition to lowering power consumption, energy harvesting (EH) has been recommended as a potential alternative, particularly for IoT, to enhance lifelong, decrease maintenance, and cut costs. [2] [3]

Energy harvesters provide voltage by converting the available energy from outside sources into electrical energy. As an example, external sources of energy are electromagnetic, mechanical, thermal, and solar energy. Following that, this electrical energy is gathered, controlled, or transformed to meet the needs of the devices being powered or the energy storage system being charged. The harvester' output voltages, however, are insufficient to fully charge the battery for example, the output voltage of a single photovoltaic (PV) cell at its highest power point is around 0.5 to 0.6V, but the voltage required to perform charging is greater than 4V. Hence, it is important to use a power management circuit with voltage boost converter such as charge pump [4].

Charge pump circuits or also known as Charge Transfer Switch or DC-DC converter which are high-voltage generators that generate voltage above the typical supply voltage. The charge pump circuit has evolved into an important circuit technique in low supply-voltage systems, in addition to various conventional usage in memory design. Electrostatic aerators, analogue switches in switched-capacitor devices, and nonvolatile memory all require high voltage to work properly [5]. When a system requires more than one dc supply voltage, a switch-mode dc-dc converter, also known as a simple chargepump circuit, is typically utilized. It is built with capacitors and switches. The switches in discrete designs are normally diodes, although IC variations can also employ MOSFETs. The two primary subcategories of DC-DC converters are buck converters and boost converters. Buck converters are used frequently in many SoCs to reduce the voltage supplied to them. Boost converters, on the other hand, are used to enhance the input voltage. Several boost converter designs are described, including L-based [3], [6], cross-coupled switching capacitor (SC) [7], and Dickson charge pump (DCP). It is feasible to utilize both switching capacitor (SC) and linear dropout regulator (LDO) on one chip and have it work correctly. Nonetheless, for energy harvesting based systems, a cascade technique with an enhancement stage that raises voltage and a buck stage for controlling it is required. This cascade leads to a greater area and worse efficiency [6].

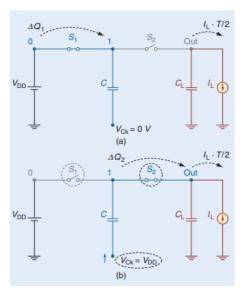

*Figure 1. One Stage Charge Pump [1]; (a) first phase (b) second phase*

An ideal charge pump as shown in figure 1 indicates that one stage charge pump which consists of two switches, pumping capacitance  $C_P$ , load capacitor  $C_L$ , power supply ( $V_{DD}$ ) and load current ( $I_L$ ). The charge pump will be driven by two phase of clock that have same amplitude with the power supply  $V_{DD}$ .

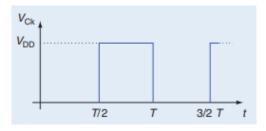

Figure 2. Clock signal, V<sub>CK</sub> of the Charge Pump [1]

During phase 1 which from 0 to T/2 as shown in figure 2, S2 is open while S1 is close. Hence  $C_P$  is being charged as it connected to  $V_{DD}$ . Therefore, the  $V_{CK}$  is equal to  $V_{DD}$ . Then, during second phase which is T/2 to T, the switches change state, S1 is open and S2 is close. The clock signal has set to  $V_{DD}$ , hence the  $C_P$  will transfer charge to  $C_L$  and  $I_L$  which can cause the voltage across to  $C_L$  increase. Clock signal is an external signal that control the timing of the switching operations within the circuit. By transferring the charge from  $C_P$  to  $I_L$ , the output voltage will be increasing follow as equation 1 stated below [8].

$$V_{\rm Out}|_{\rm Steady \ State} = 2V_{\rm DD} - \frac{I_L \cdot T}{C}.$$

(1)

The number of steps in an ideal charge pump can effect the output voltage, as shown by the equation below, where N is the number of stages and VDD is the voltage from the supply, as shown in equation (2). The output voltage corresponds to the number of steps, as shown. As a result, as the number of stages expands, this affects the output voltage because it is directly linked to the supply voltage.

$$\mathbf{V}_{\rm OUT} = \mathbf{N} * \mathbf{V}_{\rm DD} \tag{2}$$

However, there is a trade-off between the number of stages and other design factors including space , current usage, and power consumption. It's crucial to remember that the charge pump circuit's unique architecture might have an impact on the correlation between the number of stages and the output voltage. The Dickson Charge Pump, Bootstrap Charge Pump, Double Charge Pumps, Series-Parallel Charge Pumps, and Charge Pumps with Adaptive Number of Stages are a few examples of different topologies. Each has unique properties, benefits, and drawbacks.

In some application, there required different voltages for each component. Therefore, Pulse Frequency Modulation (PFM) is needed to adjust switching frequency of the charge pump based on the load demand in order to boost voltage regulation. This method can be applied to a wide range of applications to optimize energy consumption and improve overall efficiency in various electronic systems and devices. Basically PFM is used to regulate the frequency to match the output voltage same as desired value.

This study develops a wide-supply integrated CMOS employing the cross coupling DC-DC converter technology and pulse frequency modulation (PFM) to increase output voltage. However, the high performance NMOS and PMOS transistors utilized in DC-DC converters use a 130nm CMOS semiconductor manufacturing technology. The most recent technology in Cadence Software employed for simulation in this project is integrated circuits

(ICs) with feature sizes of about 130 nm.Cadence software is used to simulate the DC-DC converter and analyse the input and output voltage in order to achieve the project's aim, which is to increase the output voltage from low input voltage. PFM is employed to control the frequency in order to provide consistent output voltage with a wide variety of input voltages. In this case, the input voltage is tuned between 0.35V and 0.75V to produce an output value of about 1V

#### **1.1 Problem Statement**

Since the inductance value is directly correlated with the number of turns, and more turns need more space, small PCB sizes are in great demand nowadays but are not suited for inductors since they take up a lot of board area. Besides that, numerous ICs nowadays need a variety of voltages as it contains multiple components with different voltage requirements. For example, in one IC contains analog and digital components which they have different operations. Analog components require higher supply voltage compare to digital components for a better performance. However, by taking account design constraints and power consumption, DC-DC converter with pulse frequency modulation can be utilized to regulate the output voltage and follow the supply voltage for each of the components. This approach can maintain the power efficiency and minimize additional external components. Moreover, Dickson Charge pump has some drawback in term of the voltage conversion. This is because the charge pump in Dickson method are directly connect to the supply voltage. Hence the output can only double the input voltage. Since this project is for energy harvesting application which using low input supply and generate high voltage output. this method is not suitable. Additionally, Dickson CP features threshold losses and voltage drops. The voltage drop in Dickson CP is caused by a resistance that is present when the transistor is turned on, even if it is very tiny. However, it will become larger if there are additional stages. The threshold voltage is no different. This may reduce efficiency and have an impact on voltage output. Furthermore, DCP function in an open loop manner without feedback to precisely tune the output voltage.

Compared to more complex topologies with feedback loops, DCP techniques may lead to less accurate voltage control.

•

### **1.3 OBJECTIVES**

- i. Design a DC-DC converter using suitable topology for energy harvesting application.

- ii. Investigate the key issues in the existing charge pump and propose solutions.

- iii. Develop a wide-supply integrated CMOS using DC-DC converter.

- iv. Simulate and verify the operation of the DC-DC converter.

### **CHAPTER 2**

### LITERATURE REVIEW

#### 2.1 Charge Pump Topology

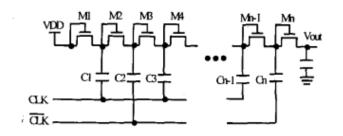

Dickson invented the Dickson topology [7] in 1976. As illustrated below, it consists of NMOS transistors, capacitors, two clock phases, a supply voltage, and an output voltage. But at each level, the NMOS turns on in turn. The threshold voltage decreases in accordance with each level. Moreover, the bulk terminals of the NMOS are often connected to the ground by the Dickson charge pump. The more stages a Dickson charge pump has, the greater body effect-induced threshold voltage drop is produced. In the end, this resulted in a loss in pumping efficiency [5]-[3],[9]-[13].

Figure 3 Dickson Charge Pump schematic design [7]

Thus, a charge transfer switch (CTS) and floating well can be utilized to reduce the PMOS gate voltage and improve the transmission voltage in the diode-connecting channel in order to prevent threshold voltage reductions and body effects [5] [9]. The floating well may keep the voltage between the source and the body constant. On the other hand, when the two pumping branches in the cross coupled CP method work in simultaneously the diode loss across stages is minimized, and the output voltage ripple is reduced. Similarly, when the number of stages rises in a DCP design, dynamic body biasing as well as other approaches may be used to assure dependability [12]. As seen in the cross coupled CTS circuit below, the inverter's gate is connected to the preceding pumping capacitance on a similar branch. The NMOS transistor's source terminal is also connected to the pumping capacitance of a prior stage on a separate branch. There is no need to wait for the capacitance of the subsequent stage to have a higher voltage in order to regulate the CTS PMOS gate at the moment of transition when the variance among VA2 and VA3 exceeds VTP since AN3 and AP3 are close in time. Capacitance charging time may be reduced as a result [9].

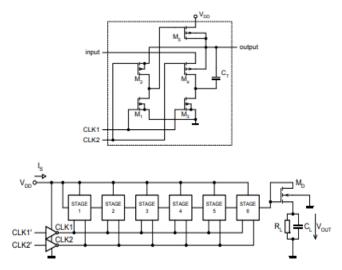

Figure 4. Cross Coupled CTS circuit [9]

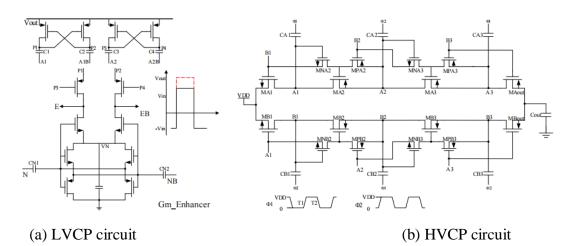

Nevertheless, in low voltage charge pump (LVCP), conductance enhancement technology may be used to activate the CTS and threshold reduction technology to raise the power conversion efficiency (PCE). By combining DBB and Gm enhancement methods, it may be possible to push the MOSFET threshold voltage over the low input voltage [2]. The DC-DC converter circuit has evolved into a crucial circuit approach in low-supply-voltage systems, in addition to several conventional uses in storage design. Electrostatic aerators, analogue switches in switched-capacitor devices, and nonvolatile memory all require high voltage to function. A Low Input Voltage CP for EH was created by Yi Li, Sheng Ming, and Quanzhen Duan. It consists of two parts: startup, which employs a Low Input Voltage Charge Pump (LVCP), and boost, which uses a High Input Voltage Charge Pump (HVCP). According to figure 5(a) below, the LVCP in this architecture is made up of two CP, a clock generator and a Gm Enhancer.Moreover, Dynamic Body Bias (DBB) was implemented to boost Power Conversion Efficiency (PCE). A complementary branch system is employed in the HVCP circuit, as shown in figure 5(b), which helps to eliminate output voltage ripples. This system is referring to the CTS charge pump technology.

*Figure 5*. *Detailed Schematic of LVCP and HVCP circuit* [2]

Kuo-Hsing Cheng, Chung-Yu Chang, and Chia-Hung Wei proposed a CMOS CP for sub-2.0V operation utilizing floating well and CTS, both of which successfully reduced the PMOS gate voltage while improving the transmitted voltage in the diode-connecting channel. These methods can help to lessen both the body effect and the threshold voltage drop [5]. As a result, the circuit below may provide a similar amount of current flowing out and capacitance while increasing the voltage.

Figure 6 CMOS Charge Pump in sub-2.0V operation [5]

According to the Andrea Ballo, Alfio, and Gaetani publications on evaluating of CP topology for Power Management of IoT Nodes [10], the application, CMOS technology, and design requirements determine the choice of a certain topology among those given in the preceding section. This study demonstrates that cross-coupled topology offers the lowest supply voltage while also having the lowest voltage conversion efficiency (VCE). Moreover, because they enable a lower input voltage, body and gate control systems may be a good alternative for low-supply-voltage systems such as TEG energy recovery. Clock-boosted flash memory could be beneficial if the primary function of internal DC-DC converters is to create a variety of voltage levels with quick settling periods. According to the comparison in this research, the boostrap and cross coupled charge pump topologies are the most commonly utilized to create high voltage from low input voltage. If low-threshold devices are available, they can be used for this purpose; however, because of their large leakage current, it is vital to consider the possible power efficiency loss. The usage of common threshold devices in the subthreshold region, on the other hand, results in a diminished capacity to transmit charge. Higher efficiency can be obtained in this situation by taking advantage of a wide area of active devices.

| Ref.                           | [2]                         | [3]                 | [12]                | [13]                 | [14]                      | [15]                 | [17]      | [18]                         | [20]      | [58                                 | 1.    | [23]     |

|--------------------------------|-----------------------------|---------------------|---------------------|----------------------|---------------------------|----------------------|-----------|------------------------------|-----------|-------------------------------------|-------|----------|

| Topology                       | Cross-coupled/<br>composite | Cross-coupled       | Bootstrap           | Dickson-with<br>DGB  | Cross-coupled<br>with BGB | Cross-coupled<br>DBB | Bootstrap | Bootstrap                    | Bootstrap | Adiabatic                           |       | Adaptive |

| No. Of Stages                  | 6 pararallel 24             | 3                   | 10                  | 4                    | 6                         | 3                    | 3         | 5                            | 1         | 3                                   | 7     | 10       |

| Aux. Circuit                   | Start-up circuit            | Clock booster<br>3x | Clock<br>booster 2x | Dynamic G<br>control | Backward G<br>Biasing     | Dynamic B<br>control | -         | Split-merge<br>four-branches | -         | Low-threshold<br>diode in every CTS |       | -        |

| Technology<br>(nm)             | 130                         | 65                  | 65                  | 65                   | 180                       | 130                  | 130       | 130                          | 180       | 13                                  | 0     | 65       |

| Min. Supply<br>(mV)            | 70                          | 150                 | 100                 | 550                  | 320                       | 150                  | 270       | 500                          | 390       | 12                                  | 5     | 120      |

| Clock Frequency<br>(MHz)       | 0.040                       | 15.2                | 10                  | 1.8                  | 0.45                      | 0.25                 | 0.8       | 2.5                          | 23        | 0.3                                 | 60    | 1        |

| Total Pumping Cap. (pF)        | 46.08                       | 22.5                | 1001                | 160                  | 288                       | 36,000 b             | 150       | 310                          | 500       | 96                                  | 224   | 286      |

| Load Cap. (pF)                 | 10,000 b                    | 30                  | 100                 | 400                  | 50.7                      | 10,000 b             | 500       | 800                          | 4000 b    | 10                                  | 0     | -        |

| Load Current at Peak η<br>(μA) | 12                          | 1.74                | 0.76                | 10                   |                           | 21                   | 5         | 30                           | 620       | 0.                                  | 1     | 3.9      |

| Max Output Power<br>(µW)       | 15                          | 1.5                 | 6.6                 | 4.7                  |                           | 10.5                 | 7         | 75                           | 620       | 0.061                               | 0.035 | 3        |

| Peak VCE (%)                   | 50                          | 80                  | 76                  | 96                   | 89                        | 86                   | 65        | 93                           | 93        | 70                                  | 80    | 58       |

| Peak η (%)                     | 58                          | 38.8                | 33                  | 66                   | -                         | 34 °                 | 58        | 78.6 °                       | 76        | 59                                  | 62    | 38.8     |

| Area (mm <sup>2</sup> )        | 0.6                         | 0.032               | 1.32                | 0.17                 | 0.14 mm <sup>2</sup>      | 0.066 <sup>b</sup>   | 0.42      | 0.98                         | 0.48      | 0.15                                | 0.1   | 0.78     |

*Figure 7. Comparison of different charge pumps.* [10]

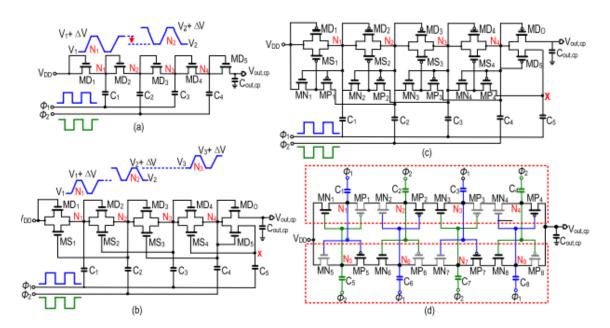

A innovative CMOS CP module with an integrated two-phase clock generator has been created for energy-harvesting step-up converters by Huan Peng, Nghia Tang, Youngoo, and Deukhyoun [13] as shown in figure 8. The goal of the charge pump is composed of two branches of charge transfer switches that include both NMOS and PMOS. These devices help in the transfer of charge from one capacitor to another. Using NMOS and PMOS devices enhances charge flow control and reduces the potential of reverse charge sharing. When combined with a corrected two-branch structure, it may entirely switch on and off the CTS with a low voltage supply. Backward control boosts internal voltages to increase clock amplitude, significantly reducing switching loss and the reverse charge-sharing event. This system can run on a small power supply by using sub threshold operation and a body bias approach. However, this purposed design is made up of six stages, each having a 24 pF pumping capacitor. With a 320 mV input, the charge pump's observed output voltage may grow from 0 to 2.04 V in 0.1 milliseconds.

Figure 8 CP With Body Bias and Backward Control Circuit [13]

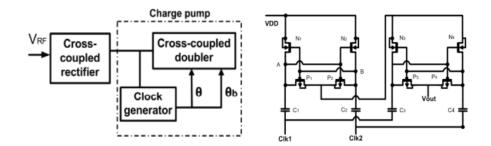

Kwangrok You, Hyungchul Kim, Minsun Kin, and Youngoo Yang presented in their work 900MHz CMOS RF-to-DC Converter Energy Harvesting with a Cross-Coupled Charge Pump, which involves of a cross coupled rectifier and a cross coupled charge pump. For their demonstrated design in this study, they employed a 0.13um CMOS technology. The charge pump may operate on an independent clock with a operating frequency of 25 MHz and a switch capacitor of 4 pF. Under these conditions, the charge pump shown a great performance of around 74% with RF power input of -6 dBm, input frequency of 900 MHz, load of 100K, and output voltage of 2.05 V. The cross coupled circuit arrangement reduces the voltage drop and reverse leakage current of the transistor [14].

Figure 9 (a)Block Diagram of RF to DC Converter (b) Cross coupled doubler circuit [14]

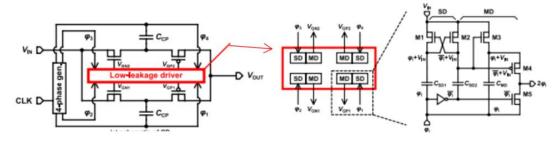

Yuto Tsuji, Tetsuya Hirose, and Toshihiro Ozaki describe a voltage boost converter (VBC) with minimal leakage drive for low-voltage energy harvesting, which includes three tiers of charge pumps with minimal leakage drivers, a ring oscillator, and a four-phase clock oscillator. A cross coupling charge pump design is used in the charge pump circuit. The driver involves of four sub-driver (SD) and main-driver (MD) pairs, each of which is assigned to producing four switching voltages, VGN1, VGN2, VGP1 and VGP2. The results of this study produced an output voltage that was four times larger than the input voltage VIN. The low-leakage driver controls the CPs so that they run with a small leakage current. The load current is unaffected by the amplitude of the control signal 2VIN. The proposed VBC transformed 0.6 V input to 2.38 V output and 0.1 V input to 0.362 V output when the load current was zero, according to simulation results. For a 0.6V input supply and a 1mA current draw, the highest efficiency was 70.3% [16].

Figure 10. Schematic of the proposed Charge Pump [16]

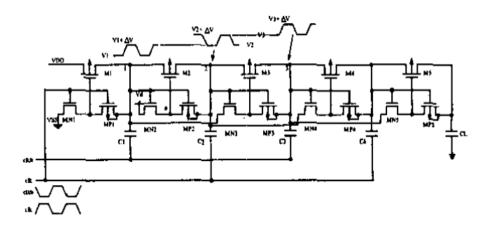

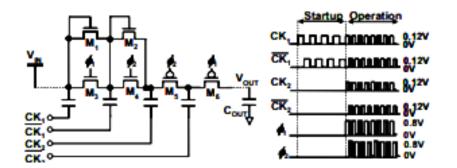

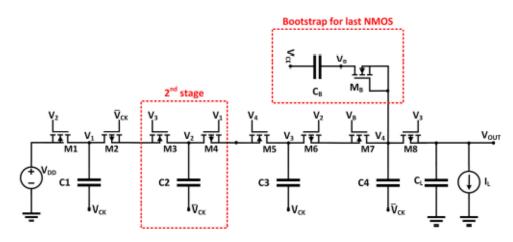

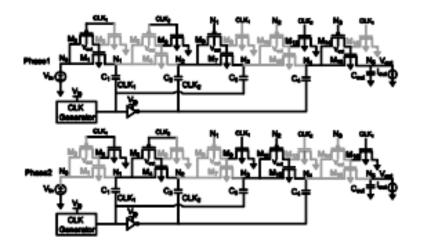

Po-Hung Chen, Koichi Ishida, and Xin Zhang developed a 120mV Input, Fully Integrated Dual-Mode Charge Pump in 65nm CMOS for a Thermoelectric Energy Harvester with an output voltage conversion efficiency of 38.8%. The proposed design can be observed in the figure below. NMOS transistors with the model numbers M3 and M4 make up the first half stages of the CMOS charge pump, while PMOS transistors with the model numbers M5 and M6 make up the back half stages. This method indicates that each transistor achieves the entire overdrive voltage when the gate terminals are controlled by high voltage clocks. Despite the fact that transistors M1 and M2 continue to operate, the majority of current flows via the CMOS switches M3 and M4 because their on-resistance is substantially lower than that of the diode-connected MOSFETs M1 and M2. As the result, the CMOS charge pump increases the performance of conversion, whereas the Dickson charge pump provides a low voltage start. With a 320 mV input, the suggested charge pump's observed output voltage may rise from zero voltage to 2.04 V in 0.1 milliseconds [18].

(a) Schematic of whole Charge Pump (b) Operations sequences of the proposed dual-model CP

*Figure 11. Proposed Design in fully integrated dual-mode charge pump* [18]

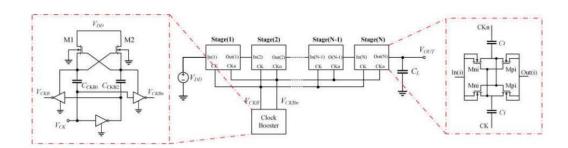

According to A. Ballo, A. D. Grasso, G. Palumbo and G. Giustolisi paper on Optimized Charge Pump with Clock Booster for Reduce Rise Time or Silicon Area, they have enhance Dickson Charge Pump (DCP) topology by adding clock booster in their proposed design as shown in figure 12. In contrasts to a standard Dickson charge pump, this design allows for an improvement in rise time while maintaining the same area occupancy or, whereas, an area decreased for a similar rise time. According to their simulation results, the suggested approach is helpful when the number of stages is big enough and the value of the load capacitor is smaller than the whole pumping capacitance. Furthermore, the rising time and size savings can be higher as 60% at the tradeoff of power consumption and minor circuit complexity due to the need of a clock booster [19].

*Figure 12. Schematic of the Charge Pump with Clock Booster* [19]

David Matousek, Jiri Hospodka and Ondrej Subrt have done two simulations to determine the size of and their impacts to efficiency and output voltage as describes in figure 13. The cell is made up of five transistors M1, M2, M3, M4, M5 and a pumping capacitor. This block is controlled by clock signals. Transistors M1, M3, M5 are closed during the first phase when CLK1 and CLK2 is equal to VDD. As a result, the transfer capacitor CT is biased to the supply voltage VDD. While transistors M2 and M4 are closed during the second phase CLK1 and CLK2 is equal to GND. As a result, transistor M2 keep bias transistor M5 unconnected. Transistor M4 links the transfer capacitor CT between the cell's input and output. As a result, the input voltage is raised by the voltage of the transfer capacitor from the biased phase. All transistors are opened in the final phase where the CLK1 is equal to GND while CLK2 is equal to VDD. At the beginning of the simulations, the efficiency rises with rising load current and falling clock frequency. Conversely, when the load current decreases and the clock frequency rises, the output voltage rises. The effectiveness of the provided charge pump's optimization depends on the results of the second phase of the simulations. With MOSFETs of the original sizes and a load of 1 M, the efficiency and output voltage are, respectively, 33.43% and 4.008 V. The efficiency may be improved by roughly 10% using the transistor sizing approach [20].

Figure 13 (a) One stage of Charge Pump (b) Schematic Diagram of Proposed Design [20]

A High-Performance Charge Pump Topology for Very Low Voltage Applications was proposed by A.Ballo, A.D. Grasso, and G. Palumbo [21]. They created and tested a four-stage and a six-stage Charge Pump to demonstrate the advantages of using STMicroelectronis' 65nm triple well CMOS technology. Each CTS is made up of an NMOS and a PMOS transistor linked in series with each other, as seen in the red outlined box. Every transistor connects its bulk terminal to the terminal designating the source during the conduction phase. Although less effectively owing to body impact, it operates in a similar manner as biasing the NMOS bulk to ground. The NMOS gate voltage is connected to node V3, whereas the PMOS gate voltage is driven by voltage V1. Except for the final stage, where a different MOSFET with a lower capacitance MB and CB is used for booting the gate voltage of the NMOS in an effort to remain the same operation as the other CTSs, and the first stage, in which the gate voltage of the PMOS is linked to the negated clock signal, this configuration continues to be repeated through the charge pump. Despite a little drop in VCE at voltages around the MOS threshold voltage owing to reverse losses, the proposed Charge Pumps have an extensive driving range, energy efficiency, and performance. It also performs effectively at an extremely low input voltage. Hence, the proposed solution seems to be especially well suited for uses needing very low input voltages.

Figure 14. Schematic the proposed Charge Pump [21]

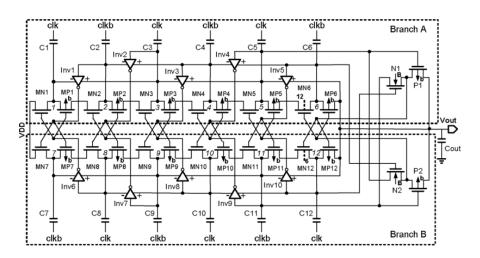

Kishore Kumar, Gabriel Chong, Harikrishan and Yazed has created a review paper on Low-Voltage Capacitive-Based Step-Up DC-DC Converters for RF Energy Harvesting System. All of the charge-pump approaches as shown in figure 15 in this paper are found to be appropriate for RFEH systems, where two or more of these techniques can be used to increase Power Conversion Effeciency (PCE) and startup performance across the board. Maximizing the PCE of charge pump is the primary design goal. The Rload, Nstage, and Cpump are the primary factors that have an impact on PCE. To achieve the intended specification, there must be trade-offs between variables like start-up time, Voutcp, and area. For example, increasing the size of a charge-pump transistor increases gate capacitance, which impacts switch loss. Furthermore, decreasing the size of the transistor improves conduction loss, reducing switching losses, which results in the overall PCE of the RFEH system. This leads to an optimal transistor size for minimal losses and the largest PCE of the charge pump, resulting in a higher power efficiency [22].

*Figure 15. Charge Pump Method (a) Conventional. (b) Charge transfer switch:Type-I (c) Charge transfer switch: Type-II . (d) Two-branch latch charge-pump*

Moreover, in a study paper A Charge Pump Based Power Management Unit With 66%-Efficiency in 65 nm CMOS by Abdulqader Mahmoud, Mohammad Alhawari, Baker Mohammad, Hani Saleh and Mohammed Ismail has proposed a cross coupled charge pump that has improvise from Dickson Charge Pump to increase and control a low input voltage as shown in in figure 10. In order to dramatically minimize the losses seen in typical DCP switches, an alternative switching mechanism is described. Silicon measurement results in 65 nm CMOS technology demonstrate a maximum efficiency of 66% at input voltage of 0.7 V and output power of 27W using a four-stage charge pump. The system can operate at a maximum operating frequency of 1.8MHz and is capable of handling load currents ranging from 0.1 A to 34 A. The proposed architecture may be employed in energy harvesting applications and supports an input voltage range of 0.55 to 0.7 V [26].

*Figure 16. Cross coupled charge pump [26]*

Table 1 below shows the different of CMOS technology, the supply voltage, generated voltage, the value of the pumping capacitor and load capacitor as well as the frequency used in 9 papers that used CP to produce high voltage from the lower supply voltage. Based on the comparison table, A Charge Pump Based Power Management Unit with 66% Efficiecny in 65nm CMOS by Abdulqader Mahmoud, Mohammad Alhawari, Baker Mohammad, Hani Saleh and Mohammed Ismail has a great charge pump as it can pump up to 3V with lowest supply voltage in between 0.55V to 0.7V which can be used in energy harvesting application. This paper is used cross coupled topology to boost up the output voltage with bigger load capacitor which is 400pF.

|                              | [5]         | [3]          | [9]         | [11]      | [13]          | [16]        | [18]      | [21]     | [26]         |

|------------------------------|-------------|--------------|-------------|-----------|---------------|-------------|-----------|----------|--------------|

| CMOS<br>tech                 | 250n<br>m   | 65nm         | 180n<br>m   | 350n<br>m | 180n<br>m     | 65n<br>m    | 65n<br>m  | 65n<br>m | 65n<br>m     |

| Supply<br>Voltage<br>(V)     | <2          | 0.55-<br>0.7 | 1-1.2       | 0.9-2     | 0.32-<br>0.44 | 0.1-<br>0.6 | 0.12      | 0.4      | 0.55-<br>0.7 |

| Output<br>Voltage<br>(V)     | 8.2<br>@Vi  | 2<br>@Vin    | 3.58<br>@Vi | ~3<br>@Vi | ~2<br>@Vin    | 2.38<br>@Vi | 0.77      | ~1       | 1.1-<br>3.4  |

| (•)                          | n =         | =0.6         | n=1.        | n=0.      | = 0.32        | n=          |           |          |              |

|                              | 0.9         |              | 2           | 9         |               | 0.6         |           |          |              |

| Pumping<br>Capacito<br>r (F) | 10 <b>p</b> | <b>40</b> p  | 20p         | 3р        | 24p           | 50p         | 28.6<br>p | 20р      | <b>40</b> p  |

| Load<br>Cap (F)              | 20p         |              | 10p         |           | 50.7          | 100p        |           | 160p     | 400p         |

| Frequency<br>(MHz)           | 50          | 0.5-<br>1.8  | 10          | 50        | 0.45          |             | 1         | 25       | 0.5-<br>1.8  |

Table 1 : Comparison of existing papers

### **2.2 Pulse Frequency Modulation (PFM)**

Based on the An Accurate, Low-Voltage, CMOS Switching Power Supply with Adaptive On-Time Pulse-Frequency Modulation (PFM) Control by Biranchinath Sahu and Gabriel, the proposed design is using PFM buck as shown in figure 17 which to step down the DC-DC converter with on-time scheme that generates a 27mV output ripple voltage from 1.4V to 4.2V input supply. Although the purpose of the circuit is to step down the voltage, however, the purpose of PFM in this proposed design is same as in this project which is to controls the low peak of the output ripple and sets the high peak. On the other hands, when the feedback sense voltage, which is obtained from the output voltage using a feedback resistor divider, falls below the reference value, the output of the comparator switches from low to high. This occurrence causes the complementary output of the SR latch to transition from high to low accordingly, therefore turning on the power PMOS transistor, causing the output ripple to rise as shown in figure 18.

*Figure 17. Schematic of a synchronous buck converter with PFM control [23].*

The range of input supply is equivalent with battery compatible range. With minimal circuit complexity added, this design may achieve 2% to 10% greater power efficiency than conventional fixed on time design, which is crucial under light-loading circumstances when idle current is a key factor in determining efficiency and battery-life performance. Hence, the result in this proposed design, the output voltage dropped to their reference voltage which set to 0.5V when they supplied the input voltage from 1.4V to 4.2V [23].

*Figure 18. Adaptive on-time PFM controller circuit [23]*

The paper A High-Voltage Generation Charge-Pump IC with Input Voltage Modulated Regulation for Neural Implant Devices by Alfian Abdi, Hyung Seok Kim, and Hyok-Kyu Cha details an intensive voltage development charge pump integrated circuit IC with an unique control mechanism for brain stimulation purposes. An input voltage modulated regulation with a low dropout regulator at the feedback path's input is utilized instead of the typically used pulse frequency modulation technique with a changing clock frequency to sustain the charge pump voltage output with varied current load ranging from 10 A to 1 mA.

Figure 19 Architecture of the proposed high voltage generator IC [25]

Figure 20. Proposed Charge Pump [25]

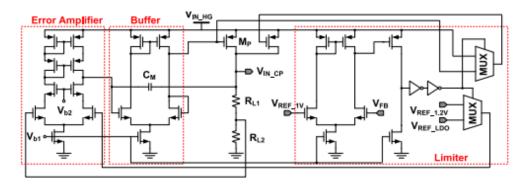

Based in the proposed design, the first two phases on the left demonstrate how the charge pump core works. CLK1 is high when CLK2 is high. Node A in the first stage will be high at this moment, whereas node B in the second stage will be low. SWN2, SWP1, SWN3, and SWP4 will be turned on, while SWN1, SWP2, SWN4, and SWP3 will be turned off. The input will charge the pumping capacitor C2, while the charge in capacitor C1 will discharge to charge capacitor C3. CLK2 is low during the following clock phase, whereas CLK1 is up. Node A is currently low whereas node B is high. A capacitor-less low-dropout (LDO) design is used because its output voltage can be changed faster than a capacitor of low-dropout (LDO) configuration. It is placed at the input of the charge pump. This is necessary to ensure that the entire HV generating circuit works properly during load transients. The main problem in the LDO design is stability at low load and loop gain. An error amplifier (EA), a buffer, a limiter, a power transistor (MP), and feedback resistors RL1 and RL2 comprise the LDO as describe in figure 21. It also adjusts the gate voltage of the MP to regulate its voltage drop through the limiter circuit. The limiter circuit is implemented with a comparator and analog multiplexers to limit the current through MP, particularly when the charge pump starts up to charge the pumping capacitors. [25]

Figure 21 LDO regulator [25]

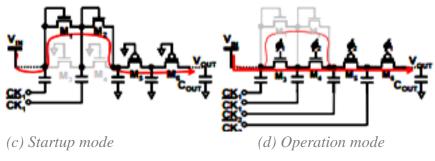

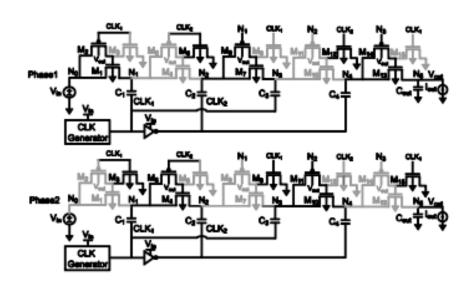

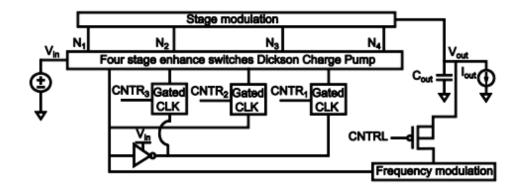

Charge Pump Based Power Management Unit with 66% Efficiecny in 65nm CMOS by Abdulqader Mahmoud, Mohammad Alhawari, Baker Mohammad, Hani Saleh and Mohammed Ismail described in this study uses an improved stage-switch Dickson charge pump (DCP) to boost and control a low input voltage. In order to dramatically minimize the losses seen in typical DCP switches, an alternative switching mechanism is described. The design proposed uses frequency and stage modulation as shown in figure 22.

Figure 22. Charge Pump with Power Management Unit

Based on this paper, cross coupled charge pump is being utilized to boost up the output voltage. It consists of load capacitor, four stages of charge pump, clock generator from the PFM, input and output voltages as shown in figure 23. The input voltage charges C1 during phase 1. C2 also charges C3, and C4 charges Cout. Cout finally drives the load. C1 charges C2, and C3 charges C4 in phase 2. The load continues to consume power from Cout. CLK1 is used to operate the gates of M2 and M3. To turn off M8,11,14, the gate control is obtained from the previous step. Using M7 as an example, in phase 2, M9 sends 0 to M7's gate. Furthermore, VsM8 = 1.2V and VgM8 = 1.2V. As a consequence, VgsM8 = 0 V, and M8 is turned off. During phase 1, however, VsM8 = 1.8V and VgM8 = 0.6V. So VgsM8 = 1.2 V, and M8 is turned on. As a result, M7 operates as a diode-connected transistor, with the transistor's drain and gate terminals connected. This configuration acts like a diode, allowing electricity to flow in one direction while blocking it in the other.

*Figure 23. Flow of the Charge Pump [26]*

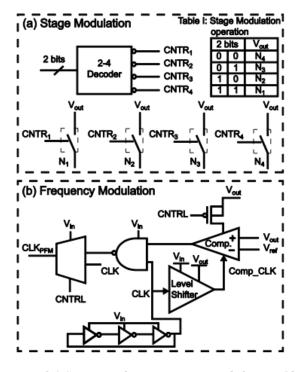

The frequency modulation tunes the voltage level and controls the output voltage based on a predetermined reference voltage, while the stage modulation offers various gain levels. In this paper, they are using pulse frequency modulation that consists of ring oscillator, level shifter and comparator, 2:1 muiltplexers and nand gate as shown in figure 24.

Figure 24 Stage and Frequency Modulation [26]

Stage modulation is a method that uses an active low decoder which the input in selected by external digital bits and switches to link each stage to the output. The CNTRL signal is used by the multiplexer to decide whether the ring oscillator for without regulation or output of the NAND if need regulation as sources of clock for the charge pump [26]. This paper has same configuration as in A Gain-Controlled, Low-Leakage Dickson Charge Pump for Energy Harvesting Applications studied by same authors. [28]

## CHAPTER 3

# **METHODOLOGY**

## **3.1 Flowchart**

Figure 25 illustrate the flow chart to develop a wide supply Integration CMOS DC-DC converter for energy harvesting application. Cadence Virtuoso software has been used throughout this project for simulations and schematic design.

Figure 25. Flow Chart of Wide Supply Integration CMOS DC-DC Converter for Energy Harvesting Applications

First step before start this project is to understand the basic charge pump and the existence charge pump for example Dickson Charge Pump. Hence, create a schematic design for Dickson Charge Pump to understand the principle of DC-DC converter where the output voltage is double from the input voltage. Furthermore, by testing the basic operations of charge pump, can understand more what parameters that will effect the output voltage. For example, by increasing the stage of the charge pump can increase the output voltage. However, the threshold voltage will be increases for this case.

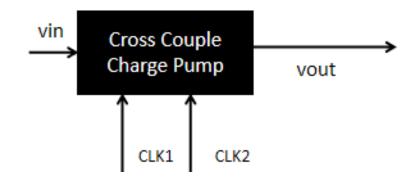

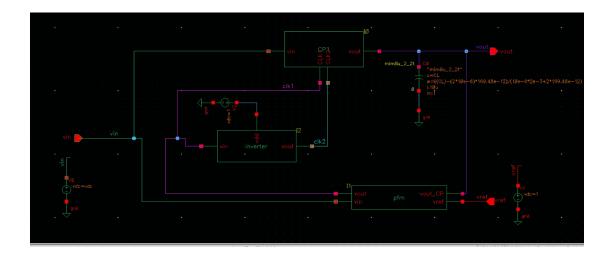

Next is design specification where to determine which topology of charge pump will be used to generate a stable output voltage which approximately 1V. In this project, cross couple charge pump is chosen to boost up output voltage as it has high efficiency as the voltage drop is reducing during charge transfer switches which can lessen the power loss as well as reducing the switching losses during in and off states. Besides that, cross couple can enhance stability as this design can minimize the reverse leakage currents. This effect can cause inefficiencies and affect the stability of the voltage boost process.

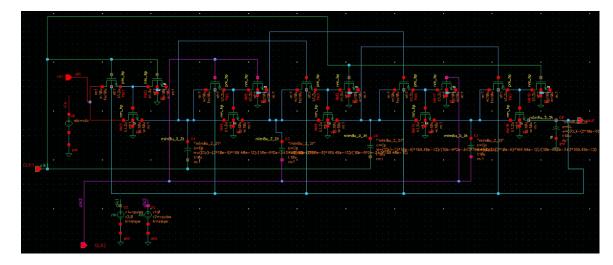

Once cross couple charge pump is decided to use in this project, schematic design need to be done to determine the specification for the design such as the size of the transistors, the number of stages for the charge pump, the value of pumping capacitors and the frequency will be used in this project. Next, in order to achieve our objectives which is to generate a stable output from varies supply voltage, Pulse Frequency Modulation is needed to regulate the frequency and adjust the output voltage accordingly to approximately 1V. Moreover, simulations are required to determine each of the components used are behaviour correctly as expected before integrate with the whole design. For example, creating a test bench for charge pump to simulate and obtain result to check whether the circuit able to boost up the supply voltage or not. Not just that, component used inside PFM also need to be simulated such as inverter, nand gate and latched comparator to ensure the result as same as expected.

Lastly, once the PFM and Charge Pump has been integrated and simulated, need to check whether the output voltage is able to sustain around 1V even though the supply voltage change from 0.35 to 0.75V. If the result are not as expected, need to check the design and adjust until can achieve our objectives,

Using 180nm CMOS technology, Dickson charge pump is used to understand the basic working of charge pump by simulating it using Cadence Virtuoso software. The five-stage charge pump shown below uses highperformance PMOS and a metal-insulator-metal capacitor. Cadence software will be used to analyze the design for DC characteristics. The goal of checking the DC characteristic is to verify that the circuit is receiving current and voltage. As shown in the given figure, each net has a voltage of 500 mV, 400 mV, 300 mV, 200 mV, and 100 mV, respectively, with a supply voltage of 500 mV.

# **3.2** Testing Basic Charge Pump (DCP)

Figure 26. Dickson Charge Pump circuit

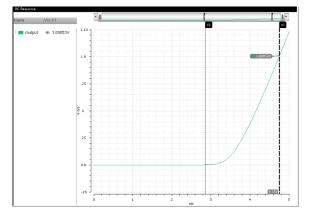

Next, Vdc is sweep for 0-1V, as a result, when the Vdc is high, the current at the Vin will be high as well. However, the output voltage, Vout is stable and remain 0V due to not operating as it need clock to operate. This is because, during DC, the capacitors act as open circuit. Hence, if looking at the Vth at M5 as shown in figure 15, the Vth = -436.617mV. Therefore, it requires 5\*Vth = 2.18V for the transistor to operate. Since the Vdc is about 0-1V, thus, the Vout is remain 0V.

Figure 27. Graph for DC characteristic for Vdc from 0 to 1V

| + | •        |          | •    |                                        | Next and Sector | 5    | Results Display                                                                                      |

|---|----------|----------|------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

|   |          |          |      |                                        | Window Expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Info | <u>H</u> elp                                                                                         |

|   | m:1 500m | l:18Øn 🔁 | w:4u | "php <sup>tholog</sup> 400m<br>M5 400m | vusat<br>vearly<br>vgd<br>vgs<br>vgt<br>vast_marg<br>vsb<br>vth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | -41.0209m<br>-41.0209m<br>572.171m<br>99.9999m<br>0<br>436.617m<br>58.9791m<br>99.9999m<br>-436.617m |

Figure 28 Vth value for M5 Transistor

When change sweep for Vdc from 0V to 3V, as shown in figure below, the voltage increase from uV to mV after 2.5V. While, when increase the sweep value to 5V, the output voltage become linear as shown in figure 30.

*Figure 29 : Graph for DC Characteristic (Vdc 0-3V)*

*Figure 30 : Graph for DC Characteristic (Vdc 0-5V)*

Figure 32 illustrates the graph where the transistor is turn on faster at 2V when load resistor RL is change from 1K ohm to 1 M ohms.

*Figure 31. Graph when*  $R_L = 1M$  *ohms*

Next, after voltage, the current will be tested by plotting the current in and current out. As shown in graph below, current out is opposite from current in as the current out is in negative value. This proves that the currents are flowing from input to output. Hence the DC characteristic are successfully tested and the circuit is works.

Figure 32. Graph for DC characteristic

On the other hand, PMOS transistor is change to NMOS transistor to test for clock. When the parameters below are configure, the output voltage seems like it pumping down the voltage as the value for output voltage is below than input voltage.

#### Freq =1Mhz, RL=1M ohm, CL=10pF, W/L = 1u/180n

Figure 33. Simulation result Vin =500mV

In addition, the transistor size is increased to 3u/180nm in order to determine whether the output voltage would change as the voltage is pushed down. However the outcomes remain unchanged and the output voltage continues to drop.

Next approach is increase the number of stages from 5 to 9 stages. However, the results turns out as in figure below where the output voltage is too much drop due to many stages.

Freq =500KHz, RL=1M ohm, CL=10pF, W/L = 3u/180n

Figure 34 Simulation result Vin=1V

Moreover, since the design keep on pumping down the output voltage, the next approach is connect the bulk of the transistor to the ground as shown in schematic design in figure 35 and set the parameter as below. The output voltage is pumping up where the supply voltage is 1V and the output voltage is 1.433V however, it is not achieve our goals which to supply around 0.5V-0.9V and the output voltage will be approximately 1V.

RL=1M ohm CL=50pF, freq =10MHz

Figure 35. Schematic and simulation result for Vin = IV

As a result of the output voltage being increased by the following approach. The next step is to create an output voltage Vout of around 1V using various supply voltages. This implies that even if the source voltage may change, the output voltage will always be around 1V. The load resistor RL should be adjusted according to the supply voltage, and the remaining parameters should remain constant until the required output voltage is reached.

Figure 36 Simulation Result of DCP

The result shows that the load resistor can affect the output voltage. The lowest the supply voltage, the higher the load resistor required. However, it only can supply at least 550mV in order to get ~1V output voltage.

Table 2 Parameters for Proposed Design I

| Vin (V) | RL(ohm) | CL (pF) | FREQ | CP (pF) | Vout (V) |

|---------|---------|---------|------|---------|----------|

|         |         |         | (Hz) |         |          |

| 550m    | 5G      | 50      | 600K | 1       | 1.0      |

| 650m    | 58M     | 50      | 600K | 1       | 1.0      |

| 750m    | 12M     | 50      | 600K | 1       | 0.99     |

| 850m    | 7M      | 50      | 600K | 1       | 1.02     |

| 950m | 5M | 50 | 600K | 1 | 1.05 |

|------|----|----|------|---|------|

|      |    |    |      |   |      |

## **3.3 PROPOSED DESIGN (Part I)**

The block diagram shown below is the first proposed design where the charge pump is directly connected to supply voltage. Hence, the output voltage is only depend on the input voltage. This method is an open loop circuit as it do not have any feedback circuit that can feedback the output to get the desired result. Since this circuit do not have any feedback circuit, hence it wont regulate the output voltage to get as expected result which is around 1 V.

Figure 37. Block Diagram of Charge Pump without PFM

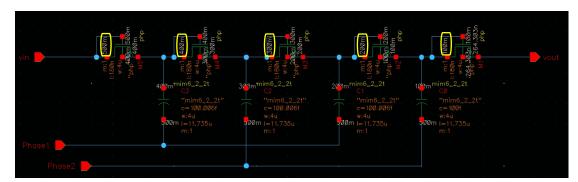

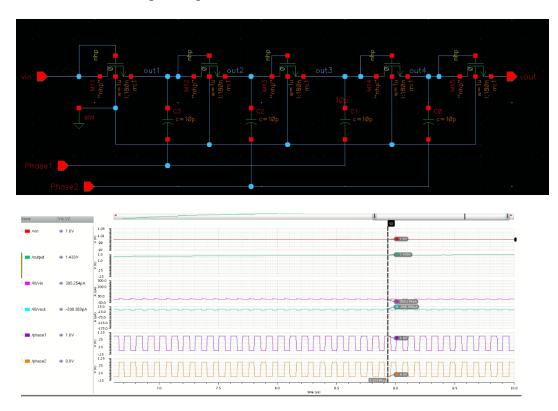

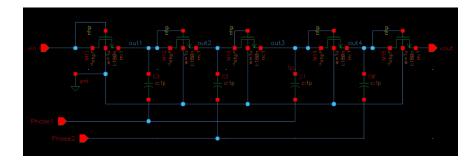

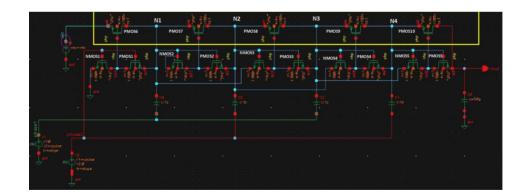

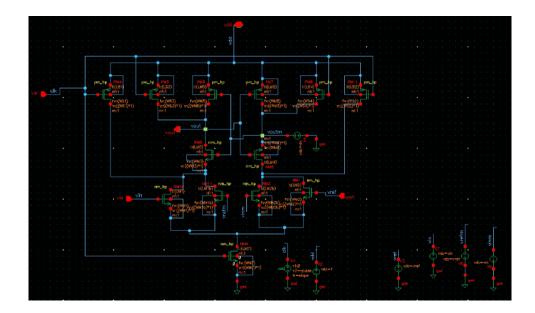

Nevertheless, since the bulk terminals of the NMOS transistor are linked to ground, a downside of the Dickson Charge Pump is that it can cause a reduction in the threshold voltage and body effect, which can reduce the pumping efficiency. The proposed design that will be used in this project is shown below. This proposed design is consists of the 5 stages of charge pump, two source clocks, one supply voltage and output voltage. As can be seen, both high performance NMOS and PMOS transistors and capacitor have been utilized in this design. The architecture is essentially the same as the Dickson Charge Pump, but it has been improved by the addition of a floating well and cross couple technique.

Figure 38. Proposed Design I

Based on figure above, the highlighted yellow is the floating well which using PMOS transistor. The floating well has the ability to maintain a constant voltage between the source and the body. It may lessen the body's impact. The parasitic capacitance of this circuit are reduced, and the design and implementation of this method in a traditional CMOS n-well process are both simple. Moreover, it resolves the body effect issue and boosts output voltage gains.

The charge transfer switches utilized in this circuit have the ability to be totally switched on and off as requested. The charge transfer switches technique is shown in figure above by the pair of MOS transistors NMOS and PMOS. The following explanation explains how the dynamically regulated charge transfer switches work. When clock phase 1 is high, clock phase 2 will be low, hence NMOS1 will be charged by couple effect of C4. Next, when the voltage at N1 is greater than its threshold voltage Vth, NMOS2 will be turned on. Thus, NMOS2 will transfer lower voltage to PMOS7 for it to turn on. After that, voltage at N2 become lower due to couple effect of C4 and when the voltage at N3 is bigger than its Vth, N2 will turn on the PMOS3. on the other hand, PMOS3 will transfer high voltage to PMOS8. however, PMOS8 will turn off due to gate-to-source voltage is zero which can avoid reverse current transmit by PMOS8. Next, for the clock phase 2, when the clock phase is high, it will cause the clock phase1 become lower hence, PMOS7 OFF and PMOS8 will turn on and the same case happen as in clock phase 1 for following transistor.

Because of this suggested design, the charge transfer switches and floating well may be employed to efficiently reduce the PMOS gate voltage while increasing the transmission voltage in the diode-connecting channel. These methods can lessen the body effect and the threshold voltage drop. As a result, the improved charge pump circuit may totally transfer voltage levels. The result are shown in appendices where the frequency are keep changing with input supply around 0.35V to 0.75V in order to get output voltage approximately 1V.

# 3.4 RESULTS AND DISCUSSIONS

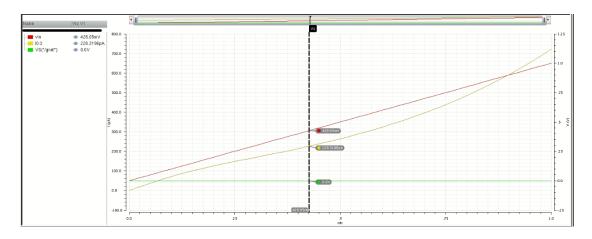

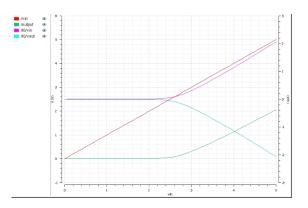

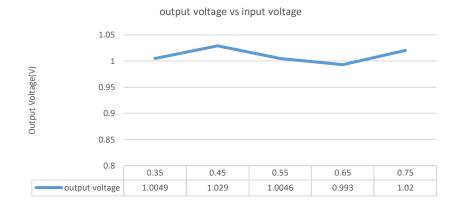

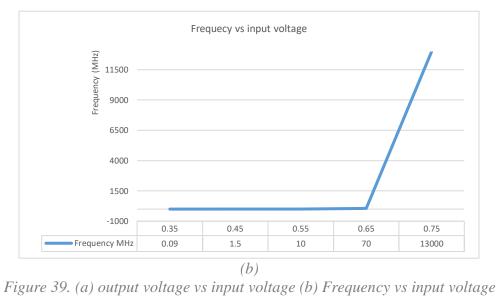

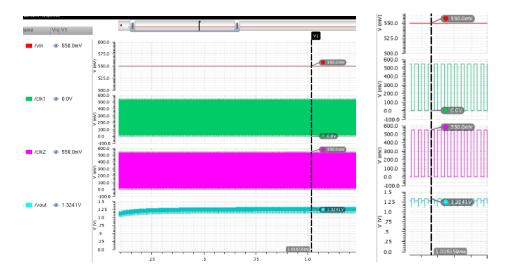

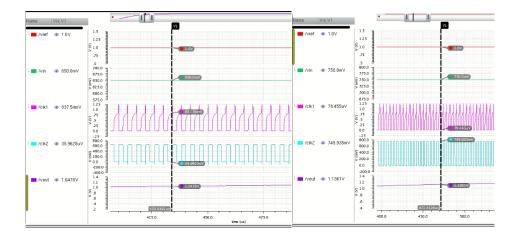

In this simulation, the charge capacitor (CP), load capacitor (CL), size of the transistor for PMOS and NMOS are all same which are 50p, 1p, 4u/180n respectively. However, the supply voltage and frequency are varies in order to get approximately 1V output voltage. Table below is the result of the simulation, where the higher the supply voltage, the bigger the clock frequency.

| Vin(mV) | Frequency (Hz) | Vout (V) | CL(F) | CP(F) | W/L (m) |

|---------|----------------|----------|-------|-------|---------|

| 350     | 90K            | 1.0049   | 50p   | 1p    | 4u/180n |

| 450     | 1.5M           | 1.029    | 50p   | 1p    | 4u/180n |

| 550     | 10M            | 1.0046   | 50p   | 1p    | 4u/180n |

| 650     | 70M            | 0.993    | 50p   | 1p    | 4u/180n |

| 750     | 13G            | 1.02     | 50p   | 1p    | 4u/180n |

Table 3 Parameters of Charge Pump without PFM

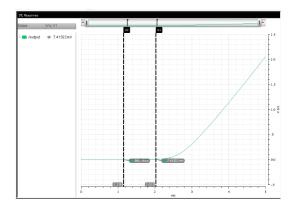

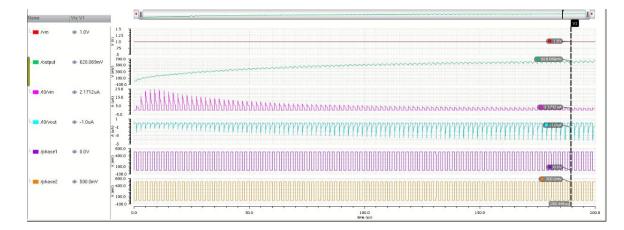

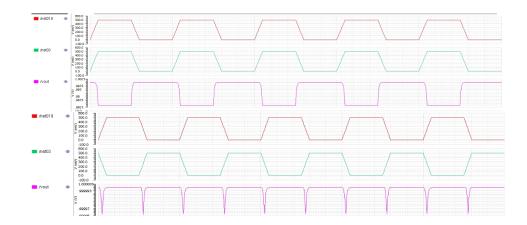

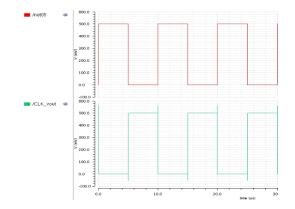

As shown in figure 39a, the result of the output voltage when the frequency is keep changing as shown in figure 39b in order to get approximately 1V while other parameters are constant. It shows that high frequency are required to pump the small input voltage in order to boost up the output voltage. This is because when the frequency is increases, the load current will decrease, hence the output voltage will be increase.

*(a)*

## **3.5 PROPOSED DESIGN (Part II)**

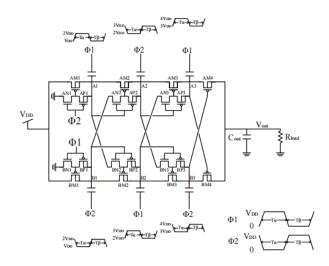

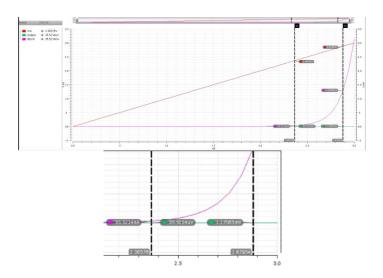

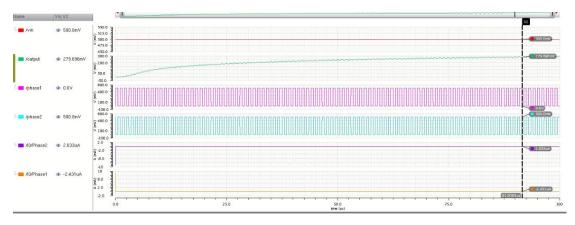

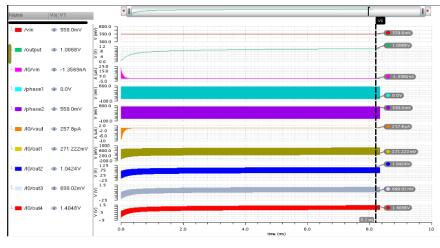

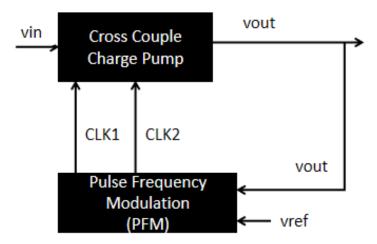

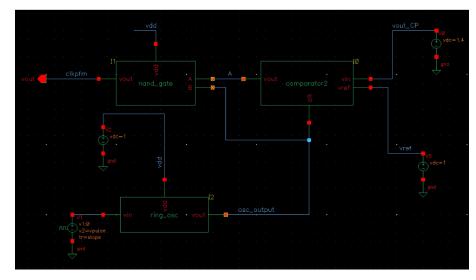

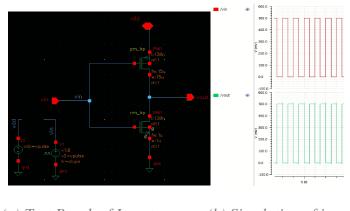

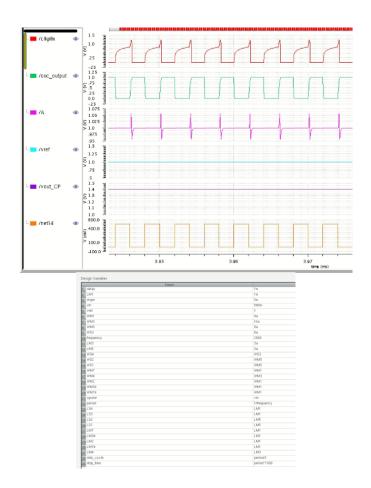

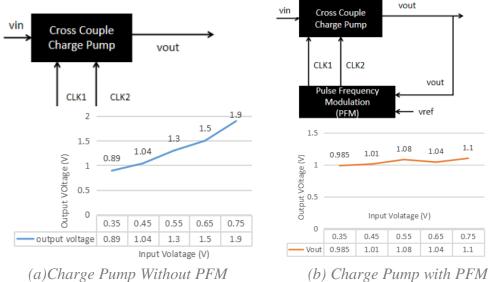

Additionally, to further accomplish our main goal for this project, which is to create a wide supply integrated CMOS employing a DC-DC converter, pulse frequency modulation (PFM) is also implemented. The primary function of PFM is to maintain the charge pump's output voltage at the correct reference voltage. The PFM control method is a technology often used in DC-DC converters to accomplish voltage management while boosting power efficiency. Below is shown the block diagram of the whole architecture in this project. Previously, the output of the charge pump is directly connect to the input supply and the clock source is coming from the external source. However, in this proposed design, the clock source of the charge pump is generated by the Pulse Frequency Modulation. The output voltage of the charge pump will be compared with reference voltage (Vref) which set to 1V. When the PFM detect there is mismatch in between output voltage and also reference voltage, the PFM will regulate the frequency and ensure that the output voltage will get approximately 1V.

Figure 40. High Level of Proposed Design II

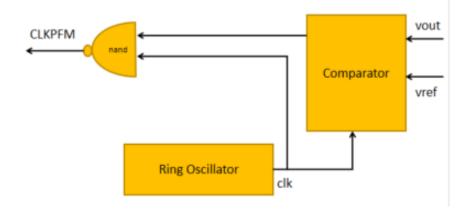

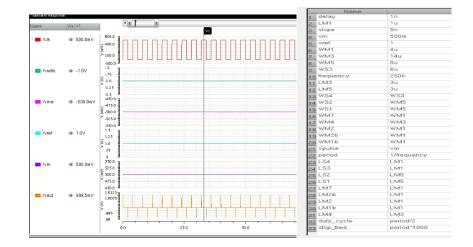

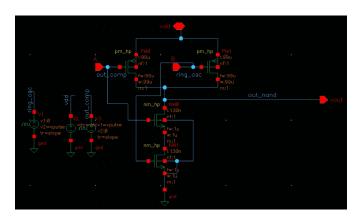

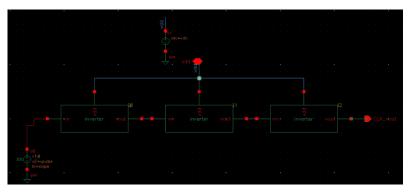

Figure 41 shows the details of the PFM where it consists of latch comparator, NAND gate, and ring oscillator. The purpose of comparator is to compare the reference voltage and output voltage and the output of the comparator will go to NAND gate. On the other hands, the purpose of ring oscillator is to generate clock. Hence, NAND gate will regulate these two clocks to generate a clock that will be a source clock for the charge pump. Ring oscillator is consists of three inverter that will continuously produce a clock.

Figure 41. The Architecture of PFM